一种SPAD阵列制备方法和SPAD芯片与流程

本申请涉及半导体领域,特别是涉及一种spad阵列制备方法和spad芯片。

背景技术:

1、spad(single photon avalanche diode,单光子雪崩二极管)是工作在击穿电压上的雪崩光电二极管,具有高灵敏度、低功耗、高探测效率等优点。

2、为了提升spad的光子探测效率(photon detection efficiency,pde),同时降低暗计数率(dark count rate,dcr),可以在spad的pn结两侧形成深p型阱(deep p well)。在制备过程中,需要在衬底上形成一层图形化光刻胶,并以该图形化光刻胶作为掩膜进行p型和n型离子注入形成pn结,再将该层图形化光刻胶去除。在形成p型阱时需要再次形成一层图形化光刻胶,将不需要离子注入的区域遮挡,离子注入形成p型阱后再将图形化光刻胶去除。所以在制备过程中,需要制作两次图形化光刻胶,需要两个光罩,导致制作成本增加;并且,还存在pn结与p型阱对准的问题,工艺控制难度增加。

3、因此,如何解决上述技术问题应是本领域技术人员重点关注的。

技术实现思路

1、本申请的目的是提供一种spad阵列制备方法和spad芯片,以降低制作成本和工艺难度。

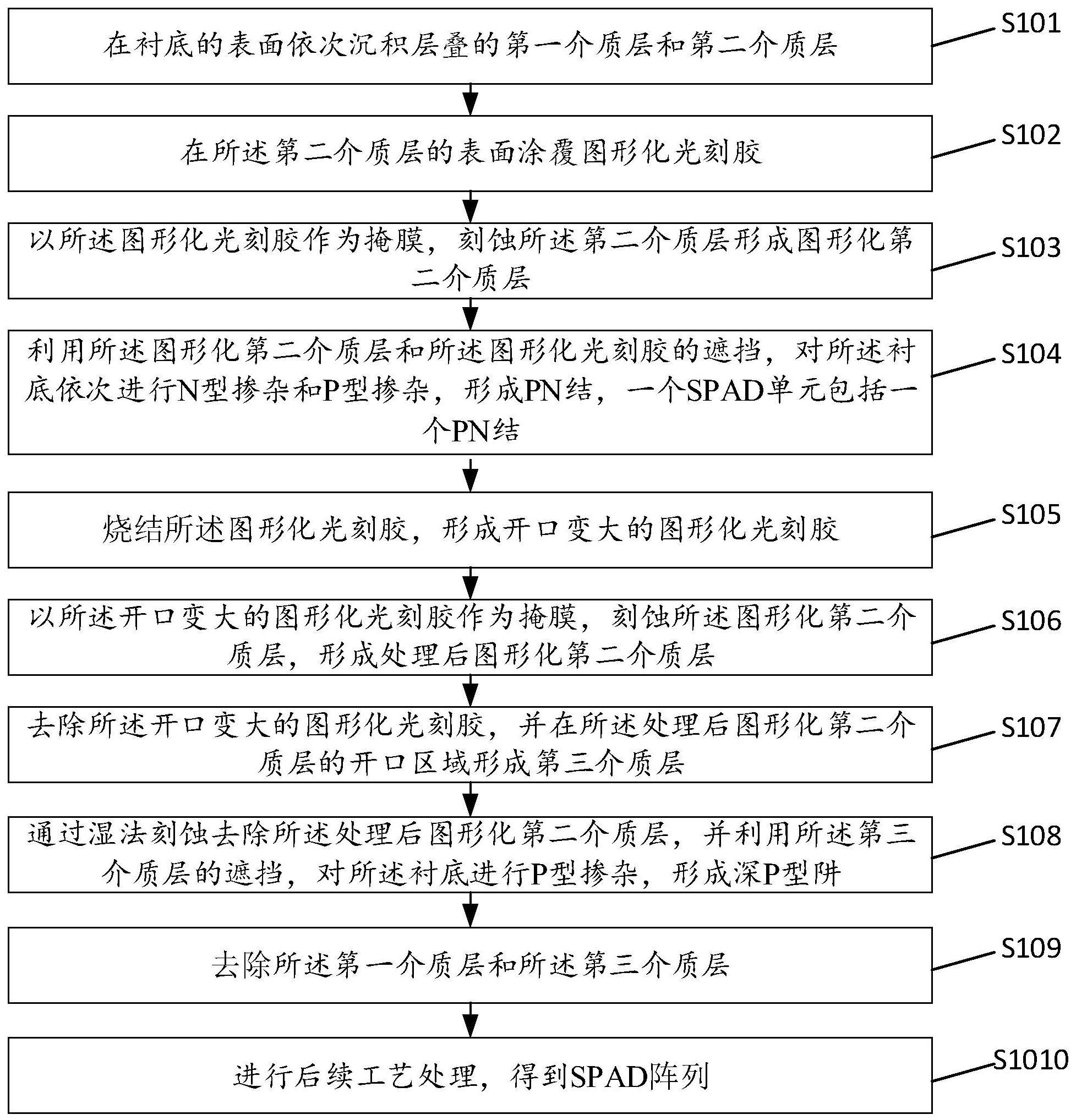

2、为解决上述技术问题,本申请提供一种spad阵列制备方法,包括:

3、在衬底的表面依次沉积层叠的第一介质层和第二介质层;

4、在所述第二介质层的表面涂覆图形化光刻胶;

5、以所述图形化光刻胶作为掩膜,刻蚀所述第二介质层形成图形化第二介质层;

6、利用所述图形化第二介质层和所述图形化光刻胶的遮挡,对所述衬底依次进行n型掺杂和p型掺杂,形成pn结,一个spad单元包括一个pn结;

7、烧结所述图形化光刻胶,形成开口变大的图形化光刻胶;

8、以所述开口变大的图形化光刻胶作为掩膜,刻蚀所述图形化第二介质层,形成处理后图形化第二介质层;

9、去除所述开口变大的图形化光刻胶,并在所述处理后图形化第二介质层的开口区域形成第三介质层;所述第三介质层的上表面与所述处理后图形化第二介质层的上表面齐平;

10、通过湿法刻蚀去除所述处理后图形化第二介质层,并利用所述第三介质层的遮挡,对所述衬底进行p型掺杂,形成深p型阱;

11、去除所述第一介质层和所述第三介质层;

12、进行后续工艺处理,得到spad阵列。

13、可选的,去除所述开口变大的图形化光刻胶之后,还包括:

14、对所述处理后图形化第二介质层做后退处理,形成开口变大的处理后图形化第二介质层。

15、可选的,在处理后图形化第二介质层的开口区域形成第三介质层包括:

16、沉积所述第三介质层,并对所述第三介质层进行抛光磨平。

17、可选的,对所述衬底进行p型掺杂具体为,在所述衬底内相邻spad单元之间形成深p型阱,深p型阱的p型离子浓度小于所述pn结的p型离子浓度。

18、可选的,进行后续工艺处理,得到spad阵列包括:

19、将远离所述pn结的衬底表面作为入光面,在所述深p型阱处制作深沟槽隔离区,所述深p型阱覆盖所述深沟槽隔离区的下半部分;在所述衬底的所述入光面设置光散射结构;

20、在所述衬底的所述入光面形成透光材料垫高层;

21、在所述透光材料垫高层表面,通过沉积透光材料层形成微透镜。

22、可选的,进行后续工艺处理,得到spad阵列包括:

23、将靠近所述pn结的衬底表面作为入光面,在所述深p型阱内制作深沟槽隔离区,所述深p型阱覆盖所述深沟槽隔离区的上半部分;

24、在所述衬底的所述入光面设置光散射结构;

25、在所述衬底的所述入光面形成透光材料垫高层;

26、在所述透光材料垫高层表面,通过沉积透光材料层形成微透镜。

27、可选的,所述第一介质层为氧化硅层,所述第二介质层为氮化硅层,所述第三介质层为氧化硅层或氮氧化硅层。

28、可选的,对所述衬底进行p型掺杂,形成深p型阱包括:

29、采用离子注入方式对所述衬底进行p型掺杂,形成深p型阱。

30、可选的,去除所述第一介质层和所述第三介质层之后,还包括:

31、对所述衬底的pn结区域再次进行p型掺杂,形成钉扎层。

32、本申请还提供给一种spad芯片,所述spad芯片中的spad阵列采用上述任一种所述的spad阵列制备方法制得。

33、本申请所提供的一种spad阵列制备方法,包括:在衬底的表面依次沉积层叠的第一介质层和第二介质层;在所述第二介质层的表面涂覆图形化光刻胶;以所述图形化光刻胶作为掩膜,刻蚀所述第二介质层形成图形化第二介质层;利用所述图形化第二介质层和所述图形化光刻胶的遮挡,对所述衬底依次进行n型掺杂和p型掺杂,形成pn结,一个spad单元包括一个pn结;烧结所述图形化光刻胶,形成开口变大的图形化光刻胶;以所述开口变大的图形化光刻胶作为掩膜,刻蚀所述图形化第二介质层,形成处理后图形化第二介质层;去除所述开口变大的图形化光刻胶,并在处理后图形化第二介质层的开口区域形成第三介质层;所述第三介质层的上表面与所述处理后图形化第二介质层的上表面齐平;通过湿法刻蚀去除所述处理后图形化第二介质层,并利用所述第三介质层的遮挡,对所述衬底进行p型掺杂,形成深p型阱;去除所述第一介质层和所述第三介质层;进行后续工艺处理,得到spad阵列。

34、可见,本申请的制备方法在第二介质层的表面形成图形化光刻胶,对第二介质层进行刻蚀形成图形化第二介质层,并利用图形化第二介质层和图形化光刻胶的遮挡进行n型掺杂和p型掺杂,形成pn结。烧结图形化光刻胶使得光刻胶的开口变大后,对图形化第二介质层进行刻蚀,刻蚀后的图形化第二介质层对应的区域即为形成深p型阱的区域,并沉积第三介质层以对不需要掺杂的区域进行遮挡,将刻蚀后的图形化第二介质层去除后进行掺杂即可形成深p型阱。本申请的制备方法只需要进行一次光刻和一个光罩即可,降低制作成本,同时在形成深p型阱时,避免了pn结与深p型阱对准的问题,降低工艺难度。

35、此外,本申请还提供一种具有上述优点的spad芯片。

技术特征:

1.一种spad阵列制备方法,其特征在于,包括:

2.如权利要求1所述的spad阵列制备方法,其特征在于,去除所述开口变大的图形化光刻胶之后,还包括:

3.如权利要求1所述的spad阵列制备方法,其特征在于,在处理后图形化第二介质层的开口区域形成第三介质层包括:

4.如权利要求1所述的spad阵列制备方法,其特征在于,对所述衬底进行p型掺杂具体为,在所述衬底内相邻spad单元之间形成深p型阱,深p型阱的p型离子浓度小于所述pn结的p型离子浓度。

5.如权利要求1所述的spad阵列制备方法,其特征在于,进行后续工艺处理,得到spad阵列包括:

6.如权利要求1所述的spad阵列制备方法,其特征在于,进行后续工艺处理,得到spad阵列包括:

7.如权利要求1所述的spad阵列制备方法,其特征在于,所述第一介质层为氧化硅层,所述第二介质层为氮化硅层,所述第三介质层为氧化硅层或氮氧化硅层。

8.如权利要求1所述的spad阵列制备方法,其特征在于,对所述衬底进行p型掺杂,形成深p型阱包括:

9.如权利要求1至8任一项所述的spad阵列制备方法,其特征在于,去除所述第一介质层和所述第三介质层之后,还包括:

10.一种spad芯片,其特征在于,所述spad芯片中的spad阵列采用如权利要求1至9任一项所述的spad阵列制备方法制得。

技术总结

本申请涉及半导体领域,公开了一种SPAD阵列制备方法,包括在衬底表面沉积第一介质层和第二介质层;在第二介质层表面涂覆图形化光刻胶;刻蚀第二介质层形成图形化第二介质层;利用图形化第二介质层和图形化光刻胶的遮挡,对衬底进行掺杂形成PN结;烧结图形化光刻胶,形成开口变大的图形化光刻胶;以开口变大的图形化光刻胶作为掩膜,刻蚀图形化第二介质层,并在处理后图形化第二介质层的开口区域形成第三介质层;去除处理后图形化第二介质层,并利用第三介质层的遮挡对衬底进行掺杂,形成深P型阱;去除第一介质层和第三介质层;进行后续工艺处理,得到SPAD阵列。本申请只需进行一次光刻和一个光罩,降低制作成本,同时降低工艺难度。

技术研发人员:徐涛,李爽,吕京颖

受保护的技术使用者:上海灵昉科技有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!