半导体器件的制造方法与流程

本发明属于半导体制造,具体涉及一种半导体器件的制造方法。

背景技术:

1、随着半导体制造工艺的不断发展,半导体器件的关键尺寸不断缩小,然而栅极宽度的缩小导致所谓的短沟道效应(short-channel effects),会导致漏致势垒降低(dibl,drain induced barrier lowering),使得半导体器件无法关断。

2、为应对该挑战,目前提出了鳍型场效应晶体管(fin fet)和全环栅型场效应晶体管(gaa fet)。在3nm以及更精细的制程中,gaa fet相对于fin fet展示出更大的优势,例如,对漏电流更好的控制,更小的dibl,更高的性能,更大的器件密度等等。

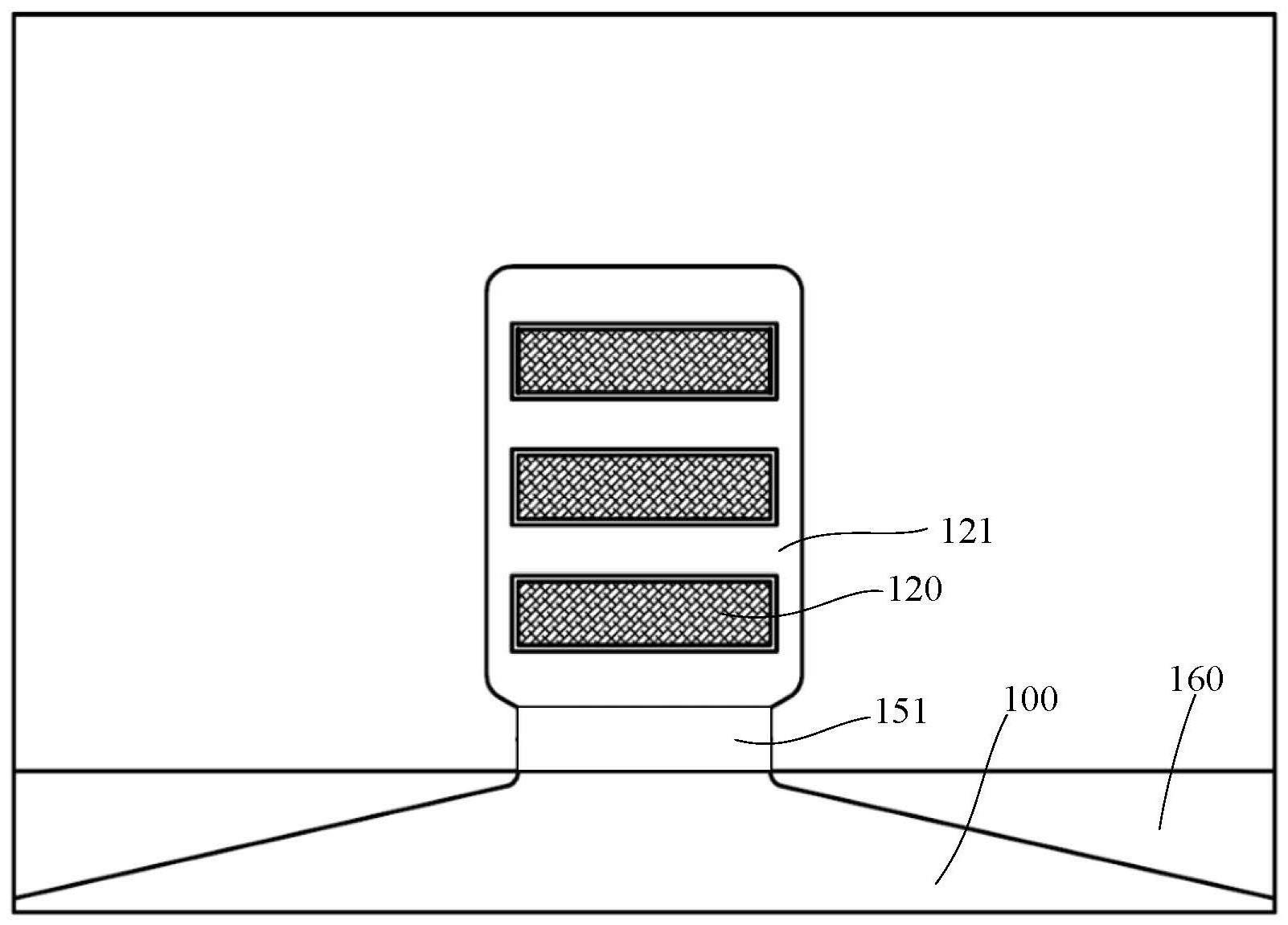

3、常规的gaa fet如图1所示,其包括衬底11、形成在衬底上的若干沟道区12、环绕沟道区12设置的栅极绝缘层(未示出)以及环绕栅极绝缘层设置的金属栅极13。沟道区12的所有侧面都被金属栅极围绕,从而能够得到更小的dibl。然而,仍需要对gaa fet进行进一步改进。

技术实现思路

1、本发明实施例公开了一种半导体器件的制造方法,以解决相关技术中半导体器件的高频开关特性不佳的问题。

2、为了解决上述技术问题,本发明实施例公开了一种半导体器件的制造方法,包括:

3、在衬底表面形成牺牲区;

4、在所述牺牲区上形成叠层结构,所述叠层结构包括交替堆叠的第一半导体层和第二半导体层;

5、去除所述牺牲区,以在所述衬底与所述叠层结构之间形成空腔;

6、在所述空腔内填充绝缘层;

7、去除所述第一半导体层和所述第二半导体层中的一者;

8、在所述第一半导体层和所述第二半导体层中的另一者周围形成栅极结构。

9、作为一些可选实施方式,所述在衬底表面形成牺牲区,包括:

10、对所述衬底表面的预设区域进行离子注入;

11、对离子注入后的区域进行退火处理以形成所述牺牲区。

12、作为一些可选实施方式,所述离子注入进行n型掺杂,所述离子注入的剂量为1×1015/cm2至5×1016/cm2。

13、作为一些可选实施方式,所述n型掺杂的掺杂物包括sb、as、p中的至少一个。

14、作为一些可选实施方式,所述在所述牺牲区上形成叠层结构,包括:

15、在所述衬底表面形成交替堆叠的所述第一半导体层和所述第二半导体层;

16、对交替堆叠的所述第一半导体层和所述第二半导体层进行刻蚀,以得到所述叠层结构,并暴露出至少一部分所述牺牲区的侧壁。

17、作为一些可选实施方式,所述对交替堆叠的所述第一半导体层和所述第二半导体层进行刻蚀,包括:

18、在交替堆叠的所述第一半导体层和所述第二半导体层的上方形成硬掩膜层,所述硬掩膜层在所述衬底上的投影与所述牺牲层相对应;

19、利用所述硬掩膜层,对所述第一半导体层、所述第二半导体层和所述衬底进行刻蚀,以形成所述叠层结构,且在所述叠层结构两侧的所述衬底内形成凹槽。

20、作为一些可选实施方式,在所述叠层结构两侧的所述衬底内形成凹槽的过程中,暴露出至少一部分所述牺牲区的侧壁。

21、作为一些可选实施方式,所述在所述牺牲区上形成叠层结构,还包括:

22、形成覆盖所述叠层结构和所述衬底的保护层;

23、对所述保护层和所述衬底进行各向异性刻蚀,保留所述叠层结构侧壁的保护层作为侧壁保护层,并暴露出至少一部分所述牺牲区的侧壁。

24、作为一些可选实施方式,所述形成覆盖所述叠层结构和所述衬底的保护层,包括:

25、采用ald工艺形成所述保护层;或者

26、所述保护层包括氮化硅基材料;或者

27、所述保护层包括氮化硅、sion、siocn或sicn中的至少一个。

28、作为一些可选实施方式,所述对所述保护层进行各向异性刻蚀,包括:

29、采用高刻蚀速率的工艺气体、高上电极射频功率及下电极射频功率,执行所述各向异性刻蚀。

30、作为一些可选实施方式,所述工艺气体包括氯气或碳氟类气体;或者

31、所述上电极射频功率范围为100至3000w,所述下电极射频功率范围为50至1000w。

32、作为一些可选实施方式,所述硬掩膜层包括氧化物绝缘层和氮化物绝缘层中的至少一个;或者

33、所述硬掩膜层包括位于内侧的氧化硅和位于外侧的氮化硅。

34、作为一些可选实施方式,所述去除所述牺牲区,包括:

35、对所述牺牲区进行各向同性等离子体刻蚀。

36、作为一些可选实施方式,所述对所述牺牲区进行各向同性等离子体刻蚀,包括:

37、在不加载下电极射频功率的情况下,在低压环境下对所述牺牲区进行刻蚀。

38、作为一些可选实施方式,所述低压环境为5m torr至800m torr。

39、作为一些可选实施方式,所述各向同性等离子体刻蚀所采用的刻蚀气体为使得所述牺牲区与所述衬底之间的刻蚀选择比大于预定值的刻蚀气体。

40、作为一些可选实施方式,所述衬底为硅,所述牺牲区为n型重掺杂的硅,所述各向同性等离子体刻蚀所采用的刻蚀气体为氯气;

41、所述牺牲区与所述衬底之间的刻蚀选择比大于200。

42、作为一些可选实施方式,所述第一半导体层和所述第二半导体层由具有不同晶格常数的半导体材料制成。

43、作为一些可选实施方式,所述第一半导体层和所述第二半导体层包括si、ge、sige、gesn、sigesn、gaas、insb、gap、gasb、inalas、ingaas、gasbp、gaassb、inp中的至少一个。

44、作为一些可选实施方式,所述在所述空腔内填充绝缘层,包括:

45、在所述叠层结构的周围以及所述衬底表面沉积所述绝缘层,直至所述空腔处的所述叠层结构下方的所述绝缘层与所述衬底上方的所述绝缘层贴合;

46、去除所述空腔以外的所述绝缘层。

47、作为一些可选实施方式,所述在所述叠层结构的周围以及所述衬底表面沉积所述绝缘层,包括:

48、利用原子层沉积工艺来沉积所述绝缘层。

49、作为一些可选实施方式,所述半导体器件的制造方法还包括:

50、对所述绝缘层进行退火处理。

51、作为一些可选实施方式,所述半导体器件的制造方法还包括:

52、去除所述侧壁保护层和所述硬掩膜层;

53、填充所述凹槽以形成浅沟槽隔离结构。

54、作为一些可选实施方式,在去除所述第一半导体层和所述第二半导体层中的一者之前,还包括:

55、在所述叠层结构的待形成所述栅极结构的区域的两侧分别形成源极区和漏极区。

56、作为一些可选实施方式,所述栅极结构包括围绕所述第一半导体层和所述第二半导体层中的所述另一者设置的栅极介电层和围绕所述栅极介电层设置的栅电极层;

57、被所述栅极结构围绕的所述第一半导体层和所述第二半导体层中的所述另一者形成为所述半导体器件的沟道区。

58、在本发明实施例的半导体器件的制造方法中,通过在半导体器件最下方的栅极结构与衬底之间形成绝缘层,抑制了最下方的栅极结构与衬底之间的寄生栅电容,提升了半导体器件的高频开关特性。

- 还没有人留言评论。精彩留言会获得点赞!