一种光刻胶定义线路半导体芯片封装的导接线路的形成方法与流程

本发明属于半导体封装,具体涉及一种光刻胶定义线路半导体芯片封装的导接线路的形成方法。

背景技术:

1、半导体封装传统是指将通过测试的晶圆按照产品型号及功能需求加工得到独立芯片的过程。封装过程为:来自晶圆前道工艺的晶圆通过划片工艺后被切割为小的晶片(die)(芯片),然后将切割好的晶片用胶水贴装到相应的基板(引线框架)架的小岛上,再利用超细的金属(金锡铜铝)导线或者导电性树脂将晶片的接合焊盘(bondpad)连接到基板的相应引脚(lead),并构成所要求的电路;然后再对独立的晶片用塑料外壳加以封装保护,塑封之后还要进行一系列操作,封装完成后进行成品测试,通常经过入检incoming、测试test和包装packing等工序,最后入库出货。

2、flipchip又称倒装片,是在i/opad上沉积锡铅球,然后将芯片翻转加热利用熔融的锡铅球与陶瓷基板相结合此技术替换常规打线接合,逐渐成为未来的封装主流,当前主要应用于高时脉的cpu、gpu(graphicprocessorunit)及chipset等产品为主。与cob相比,该封装形式的芯片结构和i/o端(锡球)方向朝下,由于i/o引出端分布于整个芯片表面,故在封装密度和处理速度上flipchip已达到顶峰,特别是它可以采用类似smt技术的手段来加工,因此是芯片封装技术及高密度安装的最终方向。倒装片连接有三种主要类型c4(controlledcollapsechipconnection)、dca(directchipattach)和fcaa(flipchipadhesiveattachement)。

3、flip-chip倒装封装另一个重要优点是电学性能。引线键合工艺已成为高频及某些应用的瓶颈,使用flip-chip封装技术改进了电学性能。

4、在芯片封装的过程中,需要将位于晶片(die)上的多个焊盘(也称为焊垫diepad)通过导线路引出,并分布到晶片不同的位置,以方便后续的倒装连接。由于焊垫一般分布在晶片的四周围,因此引出线路的建立是晶片封装的核心关键。高效、有效地引出线路,并建立精准的线路布局,可以保证芯片具备优异的电性能。为了实现高效的线路引出,通常需要在晶片上设计出合适的电路结构,以便在引出线路时能够尽可能地减少信号衰减和干扰。此外,引出线路的建立还需要考虑布线的长度、宽度和电气特性等因素,以满足芯片封装所需的高速传输和低功耗等性能要求。从而才能为智能手机、电视、电脑等各种电子设备的高性能运行提供支持。如何高效有效的将线路引出又是如何搭建精准的线路,使其满足高效电性能成为芯片先进封装的关键。

技术实现思路

1、本发明要解决的技术问题是克服现有的缺陷,提供一种光刻胶定义线路半导体芯片封装的导接线路的形成方法,以解决上述背景技术中提出的问题。

2、为实现上述目的,本发明提供如下技术方案:一种光刻胶定义线路半导体芯片封装的导接线路的形成方法,该半导体芯片封装安装结合在一基板上以与该基板上所布设的复数个焊点电性连接,包含:

3、一半导体芯片,其具有一焊垫表面,焊垫表面设有复数个焊垫;

4、至少一介电质层其被覆于该半导体芯片的焊垫表面上;

5、以及至少一导接线路,其设置于该介电质层中,且各导接线路的一端分别与半导体芯片上一焊垫电性连接,另一端则向外延伸并显露于该介电质层之外,以形成一焊点,可供与一基板上所预先布设的一焊点电性连接,以使该半导体芯片安装结合在该基板上;该半导体芯片处于一晶圆上,该晶圆上有复数个相同的半导体芯片;

6、其特征在于,该导接线路的形成方法包含下列步骤:

7、s1:在半导体芯片的焊垫表面上涂布第一层介电质层;

8、s2:利用光阻剂并以曝光显影方式在该第一层介电质层上成形焊垫表面上各焊垫的第一凹槽,使各焊垫能够经由各第一凹槽向外裸露;

9、s3:在所述各线路第一凹槽内或在各线路第一凹槽内与第一层介电质层上即所述半导体所在晶圆的表面,填入导电金属质,以分别作为各第一导接线路的原料,所述第一导接线路的原料上形成第二凹槽;

10、s4:在所述半导体芯片所在的晶圆表面填入银浆,银浆覆盖整块半导体芯片所在的晶圆上,再将银浆固化,该银浆作为第二导接线路的原料;

11、s5:在所述银浆上涂布光刻胶;

12、s6:利用预设好线路图案的光掩模以曝光显影方式于光刻胶上形成预设好线路图案的光刻胶定义线路;

13、s7:采用干式蚀刻去除光刻胶定义线路之外的第一层介电质层上的导电金属质,以分别形成上下方式叠加的第一导接线路和第二导接线路,并形成第一导接线路和第二导接线路的连接体;

14、s8:将所述光刻胶定义线路剥离,显露出第一导接线路与第二导接线路的连接体;

15、s9:在所述第一导接线路与第二导接线路的连接体表面包裹导电金属质,以形成第三导接线路;

16、s10:在所述第一层介电质层以及第三导接线路上涂布第二层介电质层;

17、s11:利用光阻剂以曝光显影方式于该第二层介电质层上分别成形与各第三导接线路一端连接的第三凹槽;

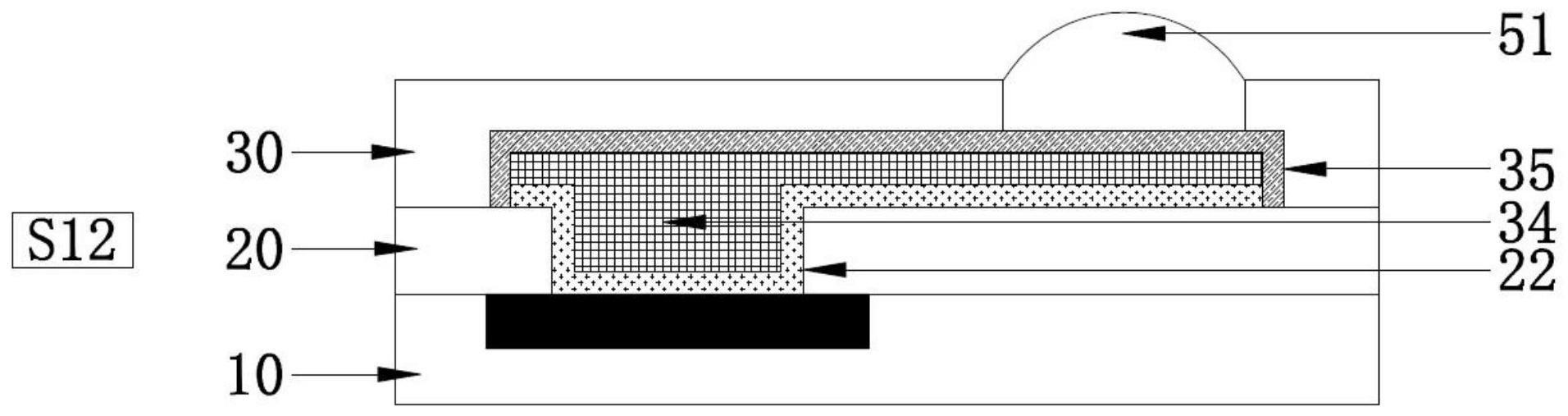

18、s12:在各第三凹槽内填入导电金属质以分别形成一焊点,该焊点显露于第二层介电质层的外面,可供分别电性连结至芯片的各焊垫。

19、优选的,所述该第一、二层介电质层和光刻胶的涂布方式为旋涂方式。

20、优选的,所述s3中在各线路第一凹槽内填入导电金属质,采用化学镍金。

21、优选的,所述s3中在各线路第一凹槽内与第一层介电质层上填入导电金属质,采用溅镀或蒸镀。

22、优选的,所述s4中填入银浆的方式采用丝网板印刷涂布,丝网板的网孔区域的形状尺寸与所述晶圆相近,相互适配。

23、优选的,所述丝网板的厚度为20-50um。

24、优选的,所述s4中将银浆固化,在取走丝网板后,将半导体芯片所在的晶圆静置15-20min,然后再将半导体芯片所在的晶圆放入氮气烤箱中,在200-300℃温度条件下烘烤20-40min。

25、优选的,所述s9中,在所述连接体表面包裹导电金属质,采用化学镍金。

26、优选的,所述该显露于第二层介电质层外面的焊点形成一凸出于第二层介电质层的外表面的半球形状。

27、优选的,所述焊点采用焊料回流印刷形成。

28、与现有技术相比,本发明提供了一种光刻胶定义线路半导体芯片封装的导接线路的形成方法,具备以下有益效果:

29、1、高精度:利用光刻胶定义线路可以实现非常高的线路精度,有助于保证导接线路的精度,从而保证导接线路的良好电性确保芯片的性能和功能。

30、2、高可靠性:采用两层介电质层和导电金属质进行构造,可以有效避免线路之间的短路和开路等问题,提高了芯片的可靠性和稳定性;较少层的介电质层还可以节省工艺与工时的投入节约成本。

31、3、高生产效率:采用旋涂方式涂布介电质层与光刻胶可以快速且均匀地覆盖在半导体芯片表面,同时利用光刻胶定义线路,作为线路的模版,利用光刻技术可以高效地生产出复杂的精准的线路图案,有助于提高生产效率;并且采用丝网板印刷银浆,不但效率大大提升,而且很节约用料节约成本。

32、4、多功能性:该方案可以根据需要设置不同形状和位置的导接线路和焊点,具有很强的可定制化和多功能性。

33、5、成本效益高:采用银浆和化学镍金等成本较低的材料可以有效降低生产成本,同时该方案采用的制程技术已经比较成熟,具有较高的可靠性和稳定性,有助于降低产品的综合成本。

34、6、灵活小巧:本发明的导接线路更优化更灵活,可布线空间更大利用率更高,避免了晶片封装过大,可更好的实现芯片封装高密度、整体结构更小巧、成品合格率更高。

- 还没有人留言评论。精彩留言会获得点赞!