封装结构及其制造方法与流程

本公开实施例涉及半导体领域,特别涉及一种封装结构及其制造方法。

背景技术:

1、封装结构是一种半导体器件被配置用作电子产品的一部分的结构。为了满足小型化和高度集成化封装结构的需求,目前提出层叠封装的概念,层叠封装具有堆叠的多个半导体器件,可以在具有较小的占用面积的同时满足快速处理大容量数据的需求。

2、通常的,层叠封装可以包括传统打线键合封装、倒装芯片(flip chip)封装以及硅通孔(tsv,through silicon via)封装。然而,这三种键合方式均具有一定的缺陷。

技术实现思路

1、本公开实施例提供一种封装结构及其制造方法,至少能够在不增大封装结构尺寸的同时,既降低封装结构的成本,又提高封装结构的性能。

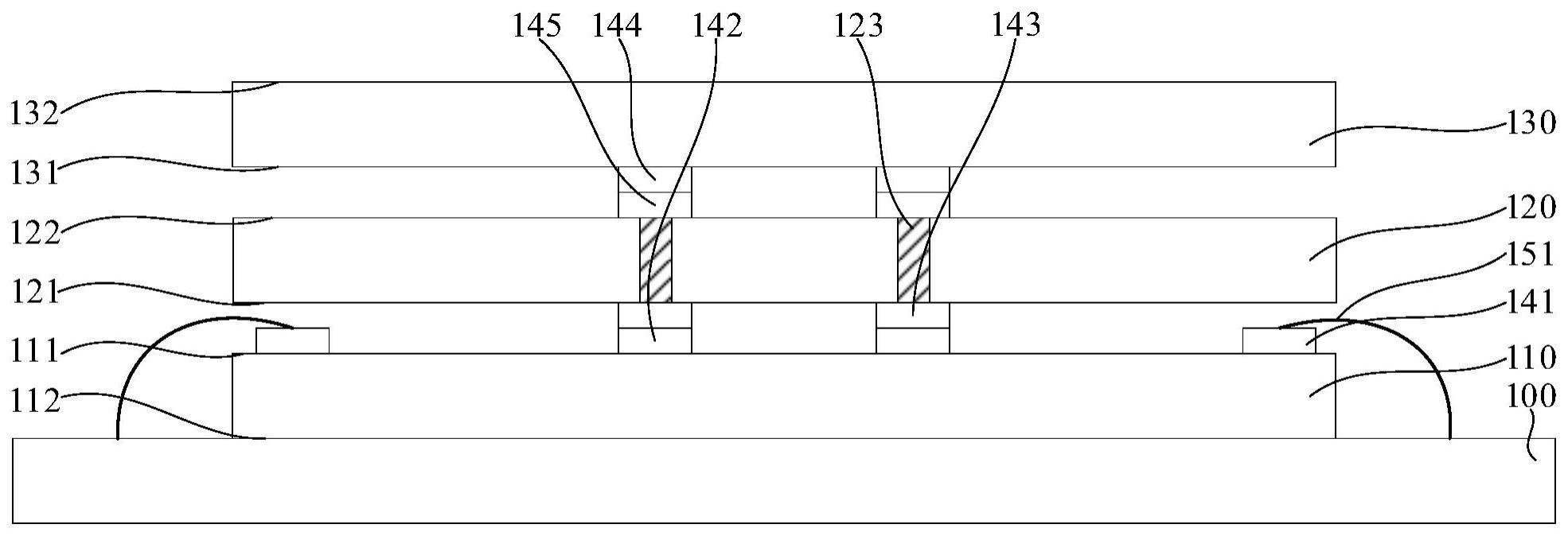

2、根据本公开一些实施例,本公开实施例一方面提供一种封装结构,包括:基底;第一芯片,位于所述基底上方,所述第一芯片具有相对的第一正面以及第一背面,所述第一背面朝向所述基底,所述第一芯片上具有第一焊盘和第二焊盘,且所述第一正面露出所述第一焊盘和所述第二焊盘,其中,所述第一焊盘位于所述第一芯片的边缘;第一导线,所述第一导线一端与所述基底电连接,另一端与所述第一焊盘电连接;第二芯片,所述第二芯片位于所述第一芯片上方,所述第二芯片具有相对的第二正面和第二背面,所述第二正面朝向所述第一芯片的第一正面,所述第二芯片上具有第三焊盘,且所述第二正面露出所述第三焊盘,所述第二芯片内具有贯穿所述第二芯片的导电结构,所述导电结构的一端与所述第三焊盘电连接,所述第二背面露出所述导电结构的另一端,所述第三焊盘与所述第二焊盘正对且电连接;第三芯片,所述第三芯片位于所述第二芯片上方,所述第三芯片具有相对的第三正面以及第三背面,所述第三正面朝向所述第二背面,且所述第三芯片上具有第四焊盘,所述第三正面露出所述第四焊盘,且所述第四焊盘与所述导电结构电连接。

3、在一些实施例中,还包括:第一电连接部,所述第一电连接部位于所述第四焊盘与所述导电结构之间。

4、在一些实施例中,所述第一芯片、所述第二芯片以及所述第三芯片的侧面齐平。

5、在一些实施例中,还包括:第二电连接部,所述第二电连接部位于所述第二焊盘与所述第三焊盘之间。

6、在一些实施例中,所述基底为基板,还包括:

7、第三电连接部,所述第三电连接部位于所述基板上,且所述第一导线与所述基底电连接的一端电连接所述第三电连接部。

8、在一些实施例中,所述封装结构包括沿垂直于所述基底表面依次堆叠的多个所述第二芯片,且相邻层的所述第二芯片之间电连接。

9、在一些实施例中,所述封装结构包括在所述基底表面并排排布的至少两个所述第一芯片,相邻的所述第一芯片的所述第一焊盘通过第二导线电连接。

10、在一些实施例中,所述第三电连接部环绕于所述至少两个所述第一芯片的外围,所述第一导线连接临近所述第三电连接部的所述第一焊盘与所述第三电连接部。

11、根据本公开一些实施例,本公开实施例另一方面还提供一种封装结构的制造方法,包括:提供基底;提供第一芯片,所述第一芯片具有相对的第一正面以及第一背面,所述第一芯片上具有第一焊盘和第二焊盘,且所述第一正面露出所述第一焊盘和所述第二焊盘,其中,所述第一焊盘位于所述第一芯片的边缘;将所述第一芯片键合至所述基底表面,所述第一背面朝向所述基底;提供第一导线,所述第一导线一端与所述基底电连接,另一端与所述第一焊盘电连接;提供第二芯片,所述第二芯片具有相对的第二正面和第二背面,所述第二芯片上具有第三焊盘,且所述第二正面露出所述第三焊盘,所述第二芯片内具有贯穿所述第二芯片的导电结构,所述导电结构的一端与所述第三焊盘电连接,所述第二背面露出所述导电结构的另一端;将所述第二芯片键合于所述第一芯片上方,使所述第二正面朝向所述第一芯片的第一正面,所述第三焊盘与所述第二焊盘正对且电连接;提供第三芯片,所述第三芯片具有相对的第三正面以及第三背面,所述第三芯片上具有第四焊盘,所述第三正面露出所述第四焊盘;将所述第三芯片键合至所述第二芯片上方,所述第三正面朝向所述第二背面,且所述第四焊盘与所述导电结构电连接。

12、在一些实施例中,所述提供基底以及所述将所述第一芯片键合至所述基底表面包括:形成第三电连接部,所述第三电连接部位于所述基底的一侧表面上;将所述第一芯片粘合至所述基底的表面上,使得所述第三电连接部位于所述第一芯片的外围。

13、本公开实施例提供的技术方案至少具有以下优点:

14、本公开实施例提供的封装结构的技术方案中,包括:基底;第一芯片位于基底上方,第一芯片具有相对的第一正面和第一背面,第一背面朝向基底,第一芯片上具有第一焊盘和第二焊盘,且在第一正面上露出第一焊盘和第二焊盘,第一焊盘位于第一芯片的边缘;第一导线,第一导线一端与基底电连接,另一端与第一焊盘电连接;第二芯片位于第一芯片上方,第二芯片具有相对的第二正面和第二背面,第二正面朝向第一芯片的第一正面,第二芯片上具有第三焊盘,第二正面露出第三焊盘,第二芯片内具有贯穿第二芯片的导电结构,导电结构的一端与第三焊盘电连接,第二背面露出导电结构的另一端,第三焊盘与第二焊盘正对且电连接;第三芯片位于第二芯片的上方,第三芯片具有相对的第三正面和第三背面,第三正面朝向第二背面,且第三芯片上具有第四焊盘,第三正面露出第四焊盘,且第四焊盘与导电结构电连接。在相关技术中,层叠封装结构通常可以包括传统打线键合封装、倒装芯片封装以及硅通孔封装。其中,传统打线键合封装中,每一芯片均需通过导线将芯片上的焊盘与基底电连接,芯片与基底的距离越远,该芯片与基底间的打线的长度越长,这会导致封装结构中的信号传输路径较长,使得封装结构的性能表现较差。倒装芯片封装中,芯片的正面具有焊盘,芯片正面与基底正对且焊盘使得芯片与基底电连接,这种封装结构不需要使用打线键合工艺,可以减小封装结构中的信号传输路径,但无法在一倒装芯片的上方再次堆叠倒装芯片,封装结构中具有多个芯片时,其他倒装芯片只能布置在基底的其他区域上,这会导致封装结构的尺寸增大。硅通孔封装中,每一芯片中均具有贯穿芯片的导电结构,不同层的芯片之间可以通过导电结构实现电连接,这种封装结构可以提高封装结构的性能,降低封装结构的功耗,并且能缩小封装结构的尺寸,但会产生较高的成本。本公开实施例中位于基底上方的第一芯片采用第一导线与基底电连接,由于第一芯片与基底的距离较近,第一导线并不会增加封装结构中的信号传输路径。位于第一芯片上方的第二芯片中具有贯穿第二芯片的导电结构,第二芯片通过导电结构与其他芯片电连接,能够提升封装结构的性能,降低封装结构的功耗,并且由于封装结构中并非全部使用第二芯片,相对于纯硅通孔封装结构能够降低部分成本。位于第二芯片上方的第三芯片采用正面具有焊盘的倒装芯片能够在进一步减小成本、减小信号传输路径的同时,不占用基底中的其他区域布置芯片,不增加封装结构的尺寸。因此,本公开实施例至少能够在不增大封装结构尺寸的同时,既降低封装结构的成本,又提高封装结构的性能。

- 还没有人留言评论。精彩留言会获得点赞!