内置ESD保护二极管的SGT器件及其制作方法与流程

本发明属于半导体器件,具体地说是一种内置esd保护二极管的sgt器件及其制作方法。

背景技术:

1、sgt(屏蔽栅),即shielded gate trench (sgt) mosfet,其基本结构如图10所示,它包括n型衬底000,在n型衬底000的背面设有漏极金属051,在n型衬底000的正面设有n型外延层001,在n型外延层001的正面设有沟槽01,在沟槽01的下段侧面以及底面设有第一屏蔽栅氧化层02,在第一屏蔽栅氧化层02的中间夹有屏蔽栅p型多晶硅21,在沟槽01的上段侧面设有第二屏蔽栅氧化层03,在第二屏蔽栅氧化层03的中间夹有控制栅多晶硅22,控制栅多晶硅22与屏蔽栅p型多晶硅21之间被氧化层隔开,在对应沟槽01外侧的n型外延层001的正面设有p型体区031,在p型体区031的正面设有源极n+型掺杂区42与背栅p+型掺杂区41,背栅p+型掺杂区41位于源极n+型掺杂区42的外侧,在源极n+型掺杂区42、背栅p+型掺杂区41、控制栅多晶硅22与第二屏蔽栅氧化层03的正面设有绝缘介质层40,在绝缘介质层40的正面设有源极金属50,源极金属50通过接触柱与源极n+型掺杂区42、背栅p+型掺杂区41以及控制栅多晶硅22相连,在源极金属50的正面设有钝化层60。

2、相比于传统的trench(沟槽) mosfet,sgt mos将栅极分为了控制栅与屏蔽栅(或分离栅)两部分,屏蔽栅一般与源极相连保持低电位。由于屏蔽栅的存在,sgt mosfet器件的cgd(栅-漏电容)几乎被完全屏蔽,这使得sgt器件的栅电荷大大降低从而能够大大提高器件的开关速度,降低开关损耗。然而传统sgt的esd(静电放电)性能并没有得到专门优化,一般sgt的esd防护设计依然采用在器件外单独设计esd器件来解决,这就使得传统sgt器件产品的面积大大增加,从而增加成本。

技术实现思路

1、本发明的目的是克服现有技术中存在的不足,提供一种内置esd保护二极管的sgt器件及其制作方法。

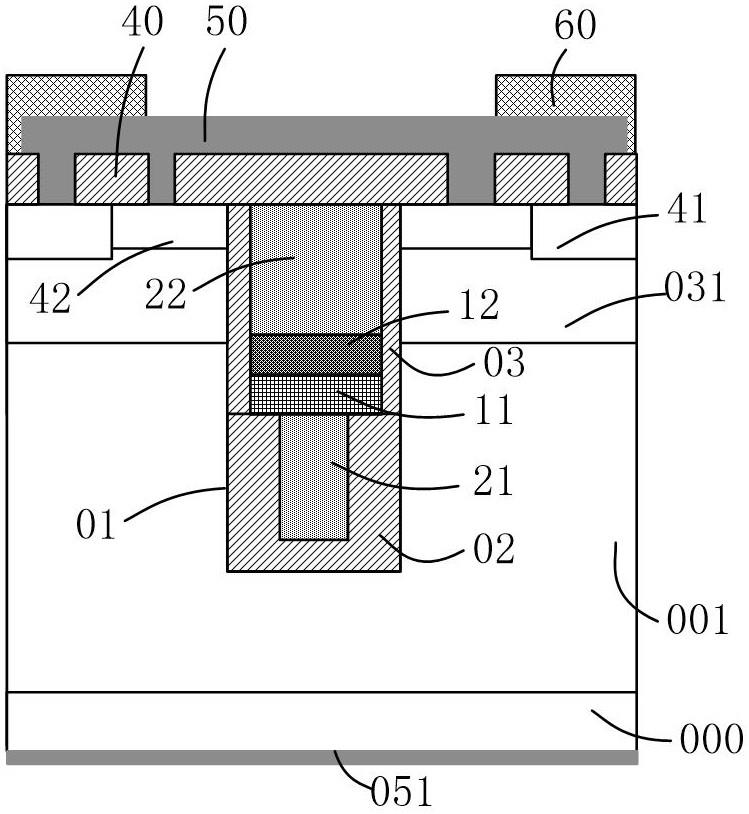

2、按照本发明提供的技术方案,所述内置esd保护二极管的sgt器件,包括n型衬底,在n型衬底的背面设有漏极金属,在n型衬底的正面设有n型外延层,在n型外延层的正面设有沟槽,在沟槽的下段侧面以及底面设有第一屏蔽栅氧化层,在第一屏蔽栅氧化层的中间夹有屏蔽栅p型多晶硅,在沟槽的上段侧面设有第二屏蔽栅氧化层,第二屏蔽栅氧化层的单侧厚度小于第一屏蔽栅氧化层的单侧厚度;

3、在第二屏蔽栅氧化层的中间夹有p型多晶硅、n型多晶硅与控制栅多晶硅,n型多晶硅位于p型多晶硅的正面,控制栅多晶硅位于n型多晶硅的正面;

4、在对应沟槽外侧的n型外延层的正面设有p型体区,在p型体区的正面设有源极n+型掺杂区与背栅p+型掺杂区,背栅p+型掺杂区位于源极n+型掺杂区的外侧,在源极n+型掺杂区、背栅p+型掺杂区、控制栅多晶硅与第二屏蔽栅氧化层的正面设有绝缘介质层,在绝缘介质层的正面设有源极金属,源极金属通过接触柱与源极n+型掺杂区、背栅p+型掺杂区以及控制栅多晶硅相连,在源极金属的正面设有钝化层。

5、作为优选,所述屏蔽栅p型多晶硅的宽度小于p型多晶硅的宽度,屏蔽栅p型多晶硅的厚度大于p型多晶硅的厚度。

6、作为优选,所述p型多晶硅、n型多晶硅与控制栅多晶硅的宽度相等,且p型多晶硅的厚度与n型多晶硅的厚度均小于控制栅多晶硅的厚度。

7、作为优选,所述控制栅多晶硅为n型控制栅多晶硅或者p型控制栅多晶硅。

8、作为优选,所述p型多晶硅的厚度与n型多晶硅的厚度相等。

9、作为优选,所述背栅p+型掺杂区的厚度大于源极n+型掺杂区的厚度。

10、上述的内置esd保护二极管的sgt器件的制作方法,该制作方法包括以下步骤:

11、s1、准备n型衬底;

12、s2、在n型衬底的正面通过外延工艺制作出n型外延层,在n型外延层的正面挖出沟槽;

13、s3、在沟槽内先通过热氧化工艺与刻蚀工艺制作出第一屏蔽栅氧化层,再通过多晶硅垫积及掺杂工艺与刻蚀工艺制作出屏蔽栅p型多晶硅;

14、s4、在沟槽内先通过热氧化工艺与刻蚀工艺制作出第二屏蔽栅氧化层,再通过多晶硅垫积及掺杂工艺、刻蚀工艺与平坦化工艺制作出p型多晶硅;

15、s5、在沟槽内通过多晶硅垫积及掺杂工艺、刻蚀工艺与平坦化工艺制作出n型多晶硅;

16、s6、在沟槽内通过多晶硅垫积及掺杂工艺、刻蚀工艺与平坦化工艺制作出控制栅多晶硅;

17、s7、在沟槽外侧的n型外延层的正面通过离子注入工艺、退火工艺与激活工艺制作出p型体区,在p型体区的正面通过离子注入工艺、退火工艺与激活工艺制作出源极n+型掺杂区以及位于源极n+型掺杂区外侧的背栅p+型掺杂区;

18、s8、在源极n+型掺杂区、背栅p+型掺杂区、控制栅多晶硅与第二屏蔽栅氧化层的正面垫积出绝缘介质层,在对应背栅p+型掺杂区、源极n+型掺杂区与控制栅多晶硅位置的绝缘介质层上通过接触孔光刻工艺、刻蚀工艺刻蚀出接触孔,通过al溅射工艺、光刻工艺与刻蚀工艺将源极金属制作出来,在接触孔内形成接触柱,在源极金属的正面垫积出钝化层;

19、s9、通过光刻工艺与刻蚀工艺将钝化层刻穿,将源极金属露出以便封装,通过晶圆减薄工艺与背面金属化工艺将漏极金属制作出来。

20、本发明能够在芯片面积相同的情况下大大提高sgt器件的esd防护能力,同时不影响sgt器件的开关速度与频率。本发明能够在esd防护能力相同的情况下大大降低芯片的面积,降低了制作成本。

技术特征:

1.一种内置esd保护二极管的sgt器件,包括n型衬底(000),在n型衬底(000)的背面设有漏极金属(051),在n型衬底(000)的正面设有n型外延层(001),在n型外延层(001)的正面设有沟槽(01),在沟槽(01)的下段侧面以及底面设有第一屏蔽栅氧化层(02),在第一屏蔽栅氧化层(02)的中间夹有屏蔽栅p型多晶硅(21),在沟槽(01)的上段侧面设有第二屏蔽栅氧化层(03),第二屏蔽栅氧化层(03)的单侧厚度小于第一屏蔽栅氧化层(02)的单侧厚度;

2.如权利要求1所述的内置esd保护二极管的sgt器件,其特征是:所述屏蔽栅p型多晶硅(21)的宽度小于p型多晶硅(11)的宽度,屏蔽栅p型多晶硅(21)的厚度大于p型多晶硅(11)的厚度。

3.如权利要求1所述的内置esd保护二极管的sgt器件,其特征是:所述p型多晶硅(11)、n型多晶硅(12)与控制栅多晶硅(22)的宽度相等,且p型多晶硅(11)的厚度与n型多晶硅(12)的厚度均小于控制栅多晶硅(22)的厚度。

4.如权利要求3所述的内置esd保护二极管的sgt器件,其特征是:所述控制栅多晶硅(22)为n型控制栅多晶硅或者p型控制栅多晶硅。

5.如权利要求3所述的内置esd保护二极管的sgt器件,其特征是:所述p型多晶硅(11)的厚度与n型多晶硅(12)的厚度相等。

6.如权利要求1所述的内置esd保护二极管的sgt器件,其特征是:所述背栅p+型掺杂区(41)的厚度大于源极n+型掺杂区(42)的厚度。

7.权利要求1-6任意一项所述的内置esd保护二极管的sgt器件的制作方法,其特征是该制作方法包括以下步骤:

技术总结

本发明涉及一种内置ESD保护二极管的SGT器件及其制作方法,它包括N型衬底、漏极金属、N型外延层、第一屏蔽栅氧化层、屏蔽栅P型多晶硅、第二屏蔽栅氧化层、P型多晶硅、N型多晶硅、控制栅多晶硅、P型体区、源极N+型掺杂区、背栅P+型掺杂区、绝缘介质层、源极金属与钝化层;在第一屏蔽栅氧化层的中间夹有屏蔽栅P型多晶硅,在第二屏蔽栅氧化层的中间夹有P型多晶硅、N型多晶硅与控制栅多晶硅,N型多晶硅位于P型多晶硅的正面,控制栅多晶硅位于N型多晶硅的正面。本发明在芯片面积相同的情况下提高SGT器件的ESD防护能力,同时不影响SGT器件的开关速度与频率。

技术研发人员:朱伟东,赵泊然,李振道,孙明光

受保护的技术使用者:江苏应能微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!