改善高压MOS偏移隔离层均匀性的方法与流程

本申请涉及半导体,具体涉及一种改善高压mos偏移隔离层均匀性的方法。

背景技术:

1、随着器件尺寸的不断减小,对于高压(hv)mos器件来说,高k栅介质-金属栅(hkmg)制程成为发展的方向。目前有前栅(gate-first)和后栅(gate-last)hkmg制程,对于gate-first制程,由于金属栅需要经历多道高温制程,会严重影响器件的性能和可靠性。相对于此,gate-last制程可以有效的避免高温制程,有效的保证器件的性能和可靠性,但是赝栅结构平坦性成为了金属栅高度均匀性的关键。

2、现有技术为了保证实施gate-last制程时赝栅结构的平坦性采取了一些措施,例如在赝栅结构中形成开口较小的间隙,并在间隙的侧壁形成阻挡侧墙。这些措施存在一定的负面影响,进而影响器件的性能。

技术实现思路

1、鉴于以上所述现有技术的缺点,本申请的目的在于提供一种改善高压mos偏移隔离层均匀性的方法,用于解决现有技术中形成的高压mos偏移隔离层的均匀性差的问题。

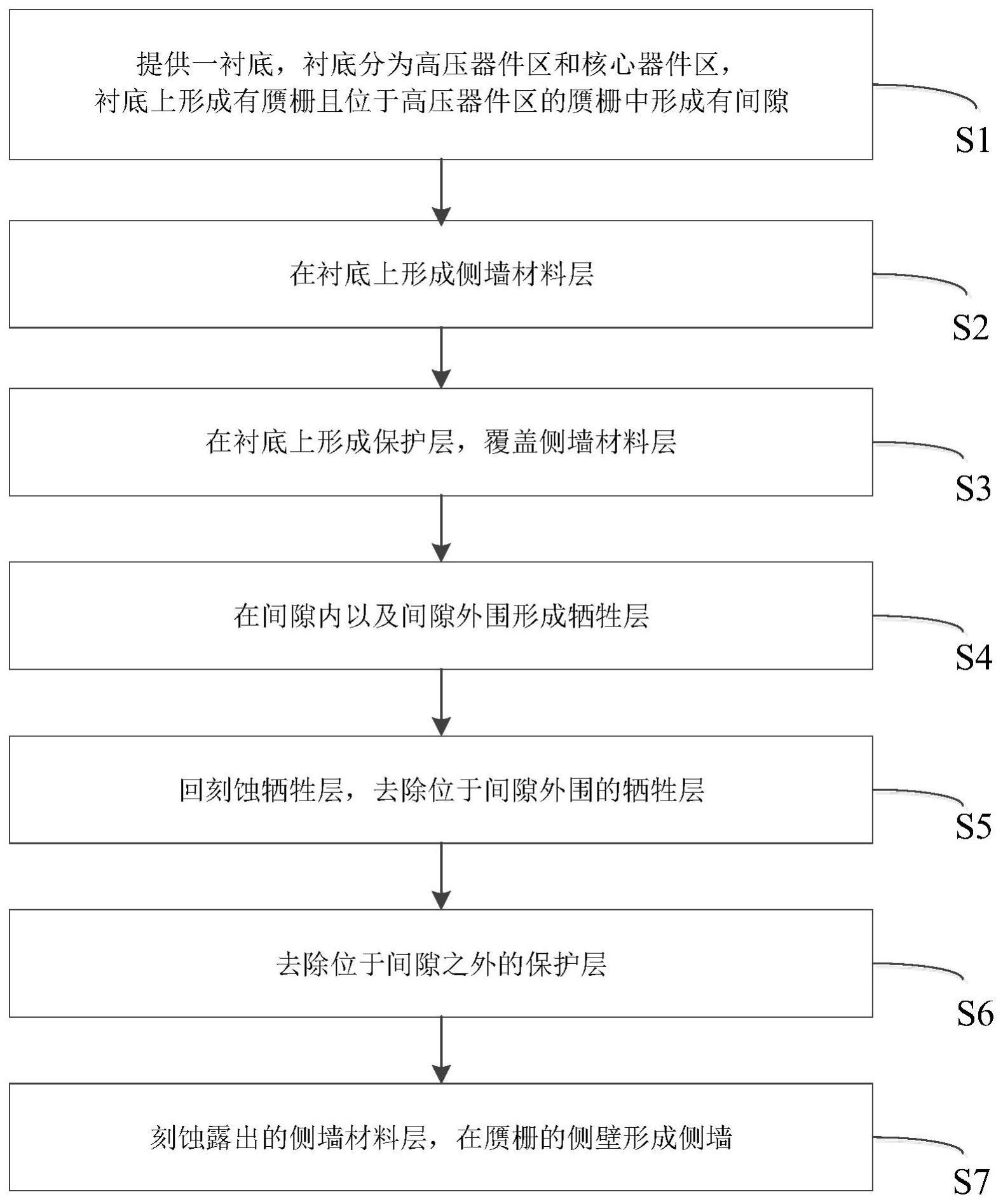

2、为实现上述目的及其它相关目的,本申请提供一种改善高压mos偏移隔离层均匀性的方法,包括:

3、步骤s1,提供一衬底,衬底分为高压器件区和核心器件区,衬底上形成有赝栅且位于高压器件区的赝栅中形成有间隙;

4、步骤s2,在衬底上形成侧墙材料层;

5、步骤s3,在衬底上形成保护层,覆盖侧墙材料层;

6、步骤s4,在间隙内以及间隙外围形成牺牲层;

7、步骤s5,回刻蚀牺牲层,去除位于间隙外围的牺牲层;

8、步骤s6,去除位于间隙之外的保护层;

9、步骤s7,刻蚀露出的侧墙材料层,在赝栅的侧壁形成侧墙。

10、优选的,通过沉积工艺形成侧墙材料层。

11、优选的,该沉积工艺包括化学气相沉积。

12、优选的,侧墙材料层的材料包括碳氮化硅。

13、优选的,侧墙材料层的厚度为80埃-100埃。

14、优选的,通过另一沉积工艺形成保护层。

15、优选的,该另一沉积工艺包括原子层沉积。

16、优选的,保护层的材料包括二氧化硅。

17、优选的,保护层的厚度为10埃-30埃。

18、优选的,步骤s7中的刻蚀具有高选择比,该刻蚀完成后,完全去除牺牲层,间隙底部存在由侧墙材料层和保护层层叠构成的阻挡层。

19、如上所述,本申请提供的改善高压mos偏移隔离层均匀性的方法,具有以下有益效果:可以有效保证高压器件区赝栅高度和核心低压器件区器件性能。

技术特征:

1.一种改善高压mos偏移隔离层均匀性的方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,通过沉积工艺形成所述侧墙材料层。

3.根据权利要求2所述的方法,其特征在于,所述沉积工艺包括化学气相沉积。

4.根据权利要求1或2所述的方法,其特征在于,所述侧墙材料层的材料包括碳氮化硅。

5.根据权利要求1或2所述的方法,其特征在于,所述侧墙材料层的厚度为80埃-100埃。

6.根据权利要求1所述的方法,其特征在于,通过另一沉积工艺形成所述保护层。

7.根据权利要求6所述的方法,其特征在于,所述另一沉积工艺包括原子层沉积。

8.根据权利要求1或6所述的方法,其特征在于,所述保护层的材料包括二氧化硅。

9.根据权利要求1或6所述的方法,其特征在于,所述保护层的厚度为10埃-30埃。

10.根据权利要求1所述的方法,其特征在于,所述步骤s7中的刻蚀具有高选择比,所述刻蚀完成后,完全去除所述牺牲层,所述间隙底部存在由所述侧墙材料层和所述保护层层叠构成的阻挡层。

技术总结

本申请提供一种改善高压MOS偏移隔离层均匀性的方法,包括:步骤S1,提供一衬底,衬底分为高压器件区和核心器件区,衬底上形成有赝栅且位于高压器件区的赝栅中形成有间隙;步骤S2,在衬底上形成侧墙材料层;步骤S3,在衬底上形成保护层,覆盖侧墙材料层;步骤S4,在间隙内以及间隙外围形成牺牲层;步骤S5,回刻蚀牺牲层,去除位于间隙外围的牺牲层;步骤S6,去除位于间隙之外的保护层;步骤S7,刻蚀露出的侧墙材料层,在赝栅的侧壁形成侧墙。通过本申请,可以有效保证高压器件区赝栅高度和核心低压器件区器件性能。

技术研发人员:何志斌

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!