一种LDMOS工艺TVS器件及其制造方法与流程

本发明涉及半导体,尤其涉及一种ldmos工艺tvs器件及其制造方法。

背景技术:

1、瞬态电压抑制器(tvs)被广泛应用于esd保护领域,传统的tvs器件普遍采用二极管结构,存在箝位电压高,箝位系数大的缺点,难以有效保护电路。

2、现有技术中,提供一种scr结构的tvs器件,能够有效地降低箝位系数,但是使用该结构的tvs器件存在触发电压高、易触发闩锁效应、esd窗口难以优化等问题。

3、因此,如何在不影响器件其他性能的情况下降低箝位系数,是目前需要解决的问题。

技术实现思路

1、本发明的目的是提出一种ldmos工艺tvs器件及其制造方法,能够降低器件箝位系数,提高器件的静电防护及电流泄放能力。

2、为了实现上述目的,本发明提供了一种ldmos工艺tvs器件,包括:

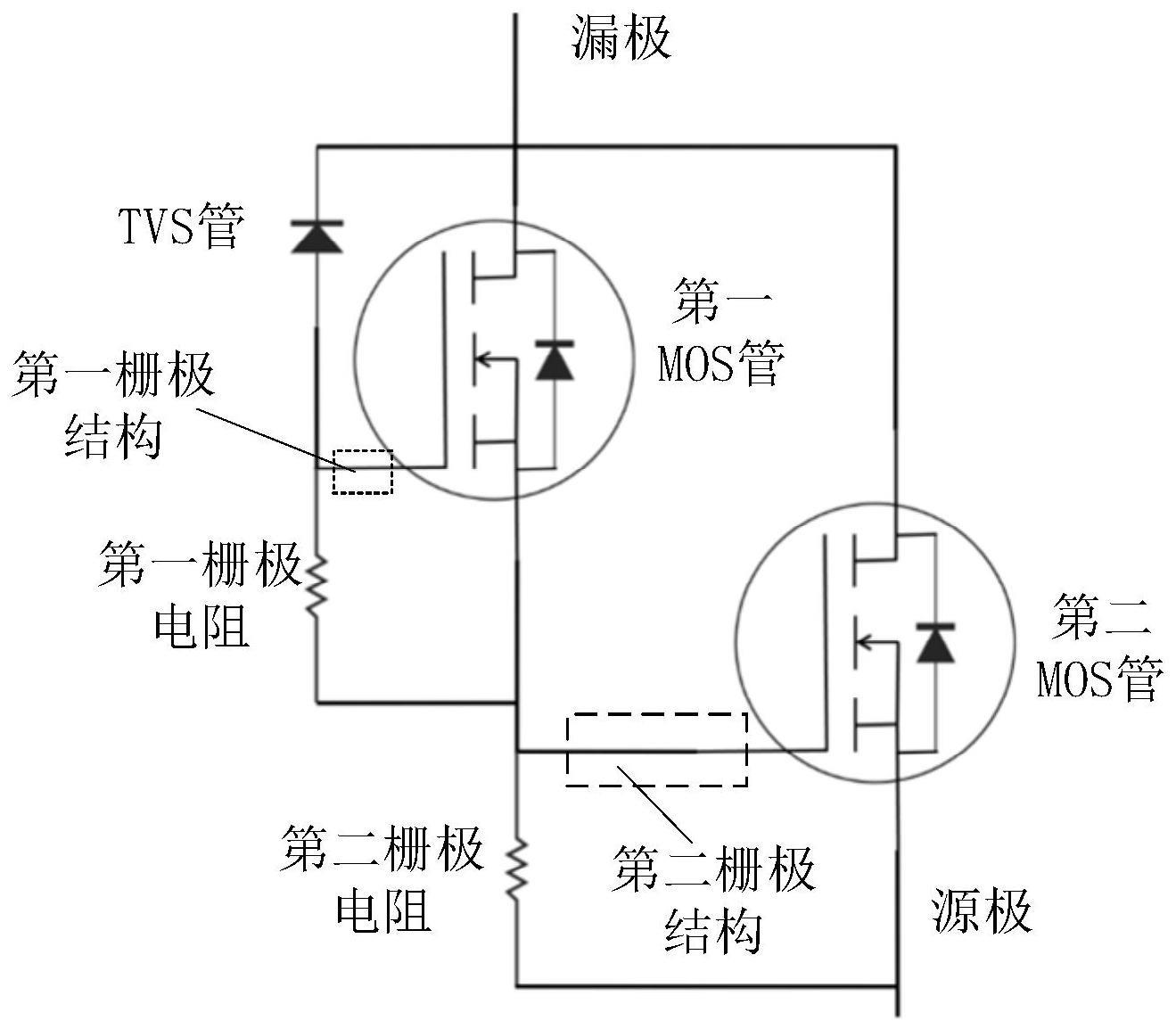

3、基板主体,所述基板主体从中央至外周包括内圈区和外圈区;所述内圈区中形成有元胞区、触发区和内圈终端区;所述元胞区中形成有第一mos管,所述触发区中形成有tvs管;

4、所述内圈区的所述基板主体上形成有第一栅极电阻、第一栅极结构;所述第一栅极结构与所述第一mos管的栅极相连接;

5、所述外圈区的所述基板主体上形成有第二mos管、第二栅极电阻、第二栅极结构,所述第二栅极结构与所述第二mos管的栅极相连接;

6、互连金属,使所述tvs管的阳极通过所述第一栅极结构与所述第一mos管的栅极相连接;使所述第一栅极电阻的一端连接于所述tvs管的阳极和所述第一栅极结构,另一端连接于所述第一mos管的源极;使所述第一mos的漏极连接于所述tvs管的阴极和所述第二mos管的漏极;使所述第二栅极电阻的一端连接于所述第二栅极结构和所述第一mos的源极,另一端连接于所述第二mos管的源极;

7、所述第一mos管和所述第二mos管通过ldmos工艺制造,所述互连金属均设置在所述基板主体的同一侧。

8、可选方案中,所述内圈区终端区环绕于所述元胞区的外周;所述内圈区终端区包括分压内环和分压外环,所述分压内环和所述分压外环之间为所述触发区。

9、可选方案中,所述元胞区位于所述内圈区的中央,所述触发区位于所述元胞区的一侧边缘,所述内圈终端区为环形,将所述元胞区和所述触发区包围在内。

10、可选方案中,所述基板主体包括第一导电类型的衬底和形成在所述衬底上的同质外延层,所述衬底的掺杂浓度大于所述外延层的掺杂浓度;

11、所述触发区包括:形成在所述外延层中的重掺杂第一导电类型的第一深体区和第一导电类型的第一阱区,形成在所述第一阱区中的第二导电类型的第一注入区,所述第一深体区和所述第一注入区构成二极管形式的所述tvs管。

12、可选方案中,所述元胞区和所述元胞区至所述触发区包括:形成在所述外延层中的第二导电类型的第二阱区,形成在所述第二阱区的重掺杂第二导电类型的第二注入区;形成在所述外延层中的重掺杂第一导电类型的第二深体区,形成在所述深体区上部外周的第一导电类型的第三阱区;形成在所述第三阱区的第二导电类型的第三注入区;形成在所述外延层上方的多晶硅;其中所述第二注入区构成所述第一mos管的漏极,所述第二深体区、所述第三阱区和所述第三注入区共同构成所述第一mos管的源极,所述多晶硅构成所述第一mos管的栅极、所述第一栅极结构和所述第一栅极电阻,或者所述第二阱区构成所述第一栅极电阻。

13、可选方案中,所述内圈区和所述外圈区之间设有环形的隔离氧化环。

14、可选方案中,所述tvs器件还包括包围所述外圈区的外圈终端区,所述外圈终端区包括分压内环和分压外环,所述分压内环和所述分压外环为环形的多晶硅柱。

15、本发明还提供了一种ldmos工艺tvs器件的制造方法,包括:

16、提供基板主体,所述基板主体包括第一导电类型的衬底和形成在所述衬底上的同质外延层,所述衬底的掺杂浓度大于所述外延层的掺杂的浓度;

17、规划出内圈区和外圈区,并于所述内圈区规划出内圈元胞区、触发区和内圈终端区,于所述外圈区规划出外圈元胞区;

18、通过注入、扩散工艺,在所述外延层中形成重掺杂第一导电类型的深体区,其中位于所述触发区中的所述深体区定义为第一深体区,位于所述内圈元胞区和所述外圈元胞区中的所述深体区定义为第二深体区;

19、形成第一氧化层,覆盖所述外延层和所述深体区;

20、在所述第一氧化层上形成第一氮化硅;

21、利用光刻、刻蚀、注入工艺在所述内圈元胞区和所述外圈元胞区的所述外延层中形成轻掺杂的第二导电类型的第二阱区;

22、在所述第二阱区上形成第二氧化层;

23、利用刻蚀工艺去除所述第一氧化层上的所述第一氮化硅;

24、利用注入工艺和所述第二氧化层作为掩模在所述外延层形成轻掺杂的第一导电类型的阱区,其中位于所述触发区的所述阱区定义为第一阱区,位于所述内圈元胞区和所述外圈元胞区的所述阱区定义为第三阱区;

25、利用刻蚀工艺去除所述外延层表面的所述第一氧化层和所述第二氧化层;

26、利用热氧或薄膜工艺在所述外延层上形成第三氧化层;

27、利用薄膜工艺在所述第三氧化层上淀积第二氮化硅;

28、利用光刻、刻蚀工艺去除部分所述第二氮化硅,利用热氧化工艺在所述外延层上形成第四氧化层;

29、利用刻蚀工艺去除剩余的所述第二氮化硅,利用热氧工艺在所述外延层上形成第五氧化层;

30、利用薄膜工艺在所述第四氧化层和所述第五氧化层上淀积多晶硅;利用刻蚀工艺去除部分所述多晶硅;

31、利用光刻、注入工艺在所述第一阱区形成重掺杂第二导电类型的第一注入区,在所述第二阱区形成重掺杂第二导电类型的第二注入区,在所述第三阱区形成重掺杂第二导电类型的第三注入区;

32、利用薄膜工艺在所述第四氧化层、所述第五氧化层和所述多晶硅上形成第六氧化层;

33、利用光刻、刻蚀工艺,刻蚀所述第六氧化层、所述第五氧化层,以在所述外延层上形成接触孔;

34、在所述金属孔中及所述基板主体的上表面形成互连金属;

35、所述第一深体区和所述第一注入区构成二极管形式的tvs管;

36、位于所述内圈区的:所述第二注入区构成第一mos管的漏极,所述第二深体区、所述第三阱区和所述第三注入区共同构成所述第一mos管的源极,所述多晶硅构成所述第一mos管的栅极、第一栅极结构和第一栅极电阻,或者所述第二阱区构成所述第一栅极电阻;所述第一栅极结构与所述第一mos管的栅极相连接;

37、位于所述外圈区的:所述第二注入区构成第二mos管的漏极,所述第二深体区、所述第三阱区和所述第三注入区共同构成所述第二mos管的源极,所述多晶硅构成所述第二mos管的栅极、第二栅极结构和第二栅极电阻,或者所述第二阱区构成所述第二栅极电阻;所述第二栅极结构与所述第二mos管的栅极相连接;

38、所述互连金属使所述tvs管的阳极通过所述第一栅极结构与所述第一mos管的栅极相连接;使所述第一栅极电阻的一端连接于所述tvs管的阳极和所述第一栅极结构,另一端连接于所述第一mos管的源极;使所述第一mos的漏极连接于所述tvs管的阴极和所述第二mos管的漏极;使所述第二栅极电阻的一端连接于所述第二栅极结构和所述第一mos的源极,另一端连接于所述第二mos管的源极;使所述内圈元胞区中的所述第一多晶硅与所述第一mos管的源极相接。

39、可选方案中,所述内圈终端区环绕于所述内圈元胞区的外周;

40、所述内圈终端区包括分压内环和分压外环,所述分压内环和所述分压外环之间为所述触发区。

41、可选方案中,所述内圈元胞区位于所述内圈区的中央,所述触发区位于所述内圈元胞区的一侧边缘,所述内圈终端区为环形,将所述内圈元胞区和所述触发区包围在内。

42、可选方案中,所述方法还包括:在所述内圈区和所述外圈区之间形成环形的隔离氧化环。

43、可选方案中,所述深体区的结深大于所述第二阱区的结深。

44、可选方案中,所述深体区与所述衬底相接。

45、本发明的有益效果在于:

46、本发明将tvs管的动态电阻转换为mos管的跨导,mos管具有负的温度系数,这两点使本发明与传统tvs器件相比具有更小的单位面积动态电阻,降低了器件箝位系数,提高了器件的静电防护及电流泄放能力。

- 还没有人留言评论。精彩留言会获得点赞!