一种纳米级工艺制程下的ESD保护结构的制作方法

本发明涉及集成电路静电保护,具体为一种纳米级工艺制程下的esd保护结构。

背景技术:

1、随着集成电路制造工艺制程从微米级发展到纳米级,微米级的有效esd(electro-static discharge,静电释放)保护结构的版图面积对于纳米级制程来讲就显得比较大,当芯片io口数量比较多时,很多大面积微米级esd保护结构就会明显增加整个芯片面积。

2、现有的纳米级工艺制程下,nmos管沟道在导通情况下一般深度为300a左右,n+和p+注入的结深在150纳米左右。采用nmos管n沟道导通泄放esd电流,其电流通路集中在沟道表面,而且还存在ldd(轻掺杂漏)结构,这种情况下该nmos管非常容易过热击穿损坏,这就是在微米工艺制程下普通esd的nmos器件设计如此巨大的原因。

3、在后续的微米工艺制程下,也有技术人员设计了ggnmos保护结构,ggnmos保护结构是通过采用了漏端n+和psub击穿形成寄生npn管来泄放esd电流。这种结构相比以前用沟道泄放esd电流有很大进步,但由于但是ggnmos依然存在ldd(轻掺杂漏)结构,同时该寄生npn管的集电区和发射区是普通n+扩散区注入,所以结深比较浅(150nm左右),大量高强度的esd电流依旧通过结深比较浅的n+集电区流入结深比较浅的n+发射区。对于大电流的esd来讲依然存在比较薄弱的环节,这种情况下就需要将ggnmos的面积做的非常大,同样不适用于纳米级工艺制程下的产品。

技术实现思路

1、为了解决现有纳米级别的芯片制造工艺中,esd结构所占面积过大的问题,本发明提供一种纳米级工艺制程下的esd保护结构,其可以在实现有效的静电保护的基础上,降低静电结构本身所占用的面积。

2、本发明的技术方案是这样的:一种纳米级工艺制程下的esd保护结构,其特征在于,其包括:rc侦测结构和防护用npn三极管;所述rc侦测结构识别esd事件,并启动所述防护用npn三极管导通泄放esd电流;

3、所述防护用npn三极管为基于n型esd注入形成的深n+扩散区npn三极管,其包括:在p-外延上生成的基于p+扩散区实现的触发源、以及基于深n+扩散区实现的集电区和发射区;

4、所述触发源连接所述rc侦测结构,并设置在整个器件的最中间;

5、所述集电区闭合围绕在所述触发源的外侧,所述集电区连接pad;

6、所述发射区闭合围绕在所述集电区外侧,所述发射区连接gnd;

7、所述发射区外侧为闭合的p+保护环,所述p+保护环基于p+扩散区实现,且连接gnd;

8、所述集电区和所述发射区之间部分构成工作基区。

9、其进一步特征在于:

10、所述发射区下方设置阻挡空穴保护环;所述阻挡空穴保护环基于nw或者dnw实现;

11、所述集电区和所述发射区的n型esd注入间距大于3微米;

12、所述集电区与所述触发源之间的注入间距、以及所述发射区和所述p+保护环之间的注入间距都大于2.5微米;

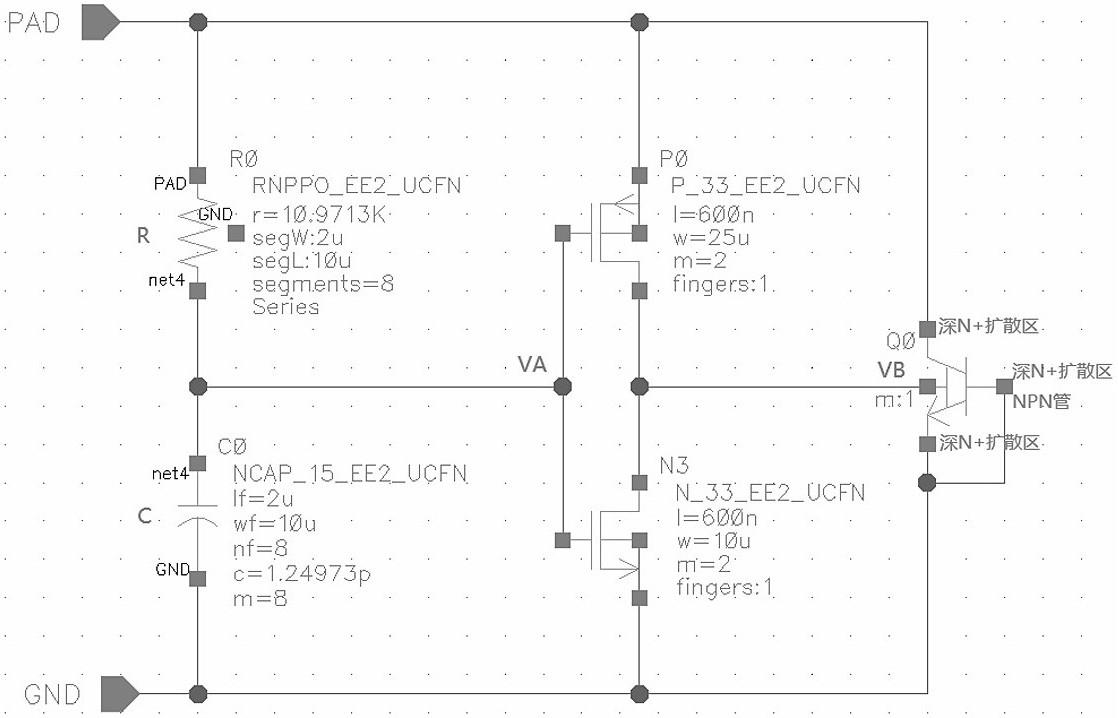

13、所述rc侦测结构包括电阻r、电容c、pmos管p0和nmos管n3;

14、所述pmos管p0和nmos管n3构成反向器,所述pmos管p0的栅极和所述nmos管n3的栅极连接构成反相器输入端va,所述pmos管p0的漏极和所述nmos管n3的漏极连接构成反相器输出端vb;

15、所述电阻r的一端和所述pmos管p0的源极连接pad,所述电阻r的另一端连接所述电容c的一端后接入所述反相器的输入端va,所述电容c的另一端和所述nmos管n3的源极接地;

16、所述反相器的输出端vb连接所述防护用npn三极管的触发源;

17、所述防护用npn三极管的面积为90um*60um;所述集电区的有效设计面积为1100um2,所述发射区的有效设计面积为1600um2;n型esd注入的集电区和发射区设计宽度为8um;

18、所述防护用npn三极管中,深n+扩散区的注入结深控制在500nm。

19、本申请提供的一种纳米级工艺制程下的esd保护结构,其包括rc侦测结构和防护用npn三极管,防护用npn三极管中的基于p+扩散区实现的触发源连接rc侦测结构;一旦有静电产生,rc侦测电路产生的侦测电流经过触发源进入防护用npn三极管中,从触发源产生流向p-外延的电流,当p-外延电阻和该电流产生的电压达到npn管开启电压时,防护用npn三极管就会导通来泄放esd电流。同时本申请通过发射区下设置nw阻挡空穴保护环,加速使得基区有一电流流向发射区,从而加速开启npn管来泄放esd电流。本申请中的防护用npn三极管是通过三极管的基体触发导通,因为防护用npn三极管没有标准工艺制程产生的ldd轻掺杂漏结构,而且esd电流是经过寄生的npn管基体泄放,并非集中在扩散区沟道表面,因此本申请中的防护用npn三极管在比较小的版图面积下可以提供比较高的esd防护能力,因此使得本申请中的防护用npn三极管更结构适用于高密度芯片和纳米工艺制程中。

技术特征:

1.一种纳米级工艺制程下的esd保护结构,其特征在于,其包括:rc侦测结构和防护用npn三极管;所述rc侦测结构识别esd事件,并启动所述防护用npn三极管导通泄放esd电流;

2.根据权利要求1所述一种纳米级工艺制程下的esd保护结构,其特征在于:所述发射区下方设置阻挡空穴保护环;所述阻挡空穴保护环基于nw或者dnw实现。

3.根据权利要求1所述一种纳米级工艺制程下的esd保护结构,其特征在于:所述集电区和所述发射区的n型esd注入间距大于3微米。

4.根据权利要求1所述一种纳米级工艺制程下的esd保护结构,其特征在于:所述集电区与所述触发源之间的注入间距、以及所述发射区和所述p+保护环之间的注入间距都大于2.5微米。

5.根据权利要求1所述一种纳米级工艺制程下的esd保护结构,其特征在于:所述rc侦测结构包括电阻r、电容c、pmos管p0和nmos管n3;

6.根据权利要求1所述一种纳米级工艺制程下的esd保护结构,其特征在于:所述防护用npn三极管的面积为90um*60um;所述集电区的有效设计面积为1100um2,所述发射区的有效设计面积为1600um2;n型esd注入的集电区和发射区设计宽度为8um。

7.根据权利要求1所述一种纳米级工艺制程下的esd保护结构,其特征在于:所述防护用npn三极管中,深n+扩散区的注入结深控制在500nm。

技术总结

本申请提供的一种纳米级工艺制程下的ESD保护结构,其包括RC侦测结构和防护用NPN三极管,防护用NPN三极管中的基于P+扩散区实现的触发源连接RC侦测结构;一旦有静电产生,RC侦测电路产生的侦测电流经过触发源进入防护用NPN三极管中,从触发源产生流向P‑外延的电流,当P‑外延电阻和该电流产生的电压达到NPN管开启电压时,防护用NPN三极管就会导通来泄放ESD电流。本申请中的防护用NPN三极管是通过三极管的基体触发导通,因为防护用NPN三极管没有标准工艺制程产生的LDD轻掺杂漏结构,而且ESD电流是经过寄生的NPN管基体泄放,并非集中在扩散区沟道表面,因此在比较小的版图面积下可以提供比较高的ESD防护能力,更结构适用于高密度芯片和纳米工艺制程中。

技术研发人员:余自然

受保护的技术使用者:无锡翼盟电子科技有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!