半导体结构及半导体结构的制作方法与流程

本公开涉及半导体的,尤其涉及一种半导体结构及半导体结构的制作方法。

背景技术:

1、芯片键合技术中,先将晶圆切割成芯片颗粒,然后选取合格的芯片与目标晶圆进行直接键合,实现无球三维多层堆叠封装。无球三维多层堆叠封装中,在一层芯片颗粒与晶圆键合后,需要将芯片之间空隙填平,才能继续后续的晶圆减薄/大马士革等工艺。然而在对芯片之间空隙填平的过程中,多层芯片的堆叠容易受芯片之间空隙中填充材料产生的应力而导致芯片脱落甚至断裂。

技术实现思路

1、以下是对本公开详细描述的主题的概述。本概述并非是为了限制权利要求的保护范围。

2、为克服相关技术中存在的问题,本公开提供了一种半导体结构及半导体结构的制作方法。

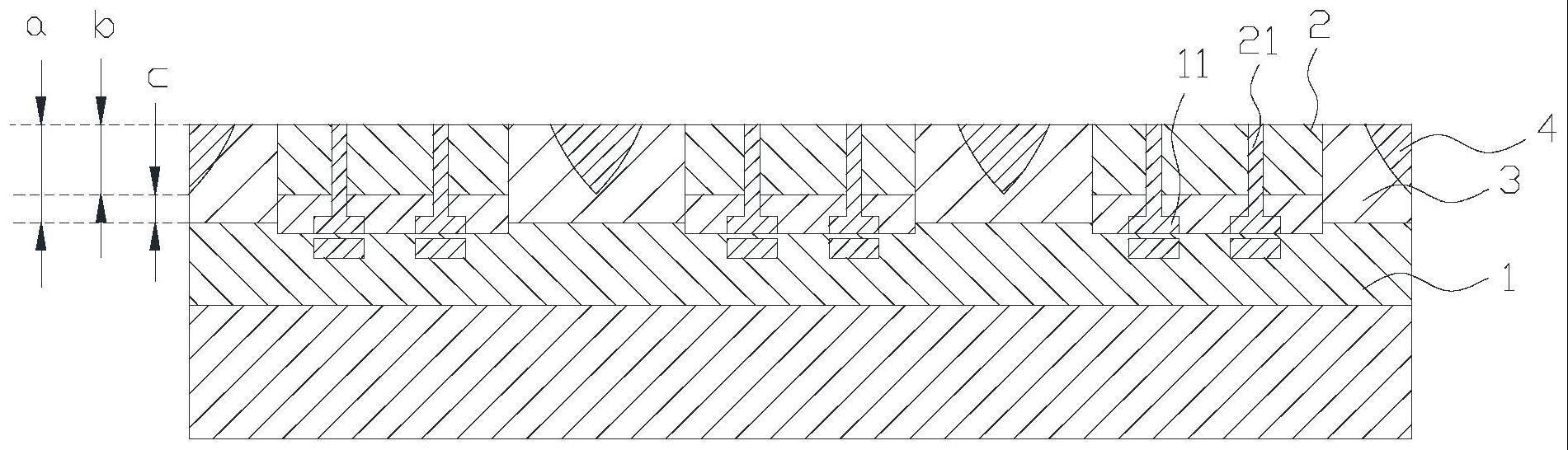

3、本公开实施例第一方面,提供一种半导体结构,所述半导体结构包括:多个芯片,相邻所述芯片间隔分布,所述芯片之间的空隙依次堆叠有介电层和中间层;

4、所述介电层覆盖于所述芯片的顶面和侧面,并将相邻所述芯片之间的空间的底部填充,所述介电层的顶面与所述芯片的顶面平齐;

5、所述中间层填充于所述介电层在相邻所述芯片之间围合的空间,所述中间层的顶面与所述芯片的顶面平齐。

6、根据本公开的一些实施例,所述中间层的最小高度大于所述介电层的最小高度。

7、根据本公开的一些实施例,所述芯片堆叠有多层,所述芯片具有垂直互联结构,上层所述芯片与下层所述芯片通过所述垂直互连结构连接,上层所述芯片的一侧的所述介电层覆盖下层所述芯片一侧的所述介电层,并覆盖下层所述芯片一侧的所述中间层。

8、根据本公开的一些实施例,所述芯片的底面具有金属极,所述金属极与所述垂直互连结构连接,下层所述芯片上的所述垂直互连结构与上层所述芯片底面的金属极连接。

9、根据本公开的一些实施例,所述半导体结构还包括基底,所述芯片键合于所述基底上,所述介电层覆盖自相邻所述芯片之间暴露的所述基底的顶面。

10、根据本公开的一些实施例,相邻两芯片之间的所述中间层的宽度随高度的降低而降低。

11、根据本公开的一些实施例,所述模塑化合物层的材料包括环氧塑封料;所述中间层的材料包括旋转涂布玻璃;所述介电层的材料包括二氧化硅或氮化硅或二者的混合物。

12、本公开实施例的第二方面,提供一种半导体结构的制作方法,所述半导体结构的制作方法包括:

13、提供基底和芯片;

14、将所述芯片键合于所述基底的第一表面上,相邻芯片间隔设置;

15、形成介电层,所述介电层填充相邻所述芯片之间的部分空间,并覆盖所述芯片的侧壁和顶面以及暴露出的所述基底的顶面;

16、于所述芯片一侧的所述介电层上形成中间层,所述中间层填充相邻所述介电层在所述芯片之间围合的空间,并覆盖所述芯片一侧的所述介电层;

17、于所述中间层以及所述芯片顶面上的所述介电层上形成模塑化合物层,所述模塑化合物层填充所述中间层在相邻所述芯片之间围合的空间,并覆盖所述中间层和所述芯片顶面的所述介电层;

18、采用背面减薄工艺去除部分所述芯片、部分所述介电层、部分中间层以及全部模塑化合物层,所述背面减薄工艺至少将芯片减薄至使得所述垂直互连结构的顶端自所述芯片顶面露出,并将剩余所述中间层以及剩余所述介电层暴露。

19、根据本公开的一些实施例,所述采用背面减薄工艺去除部分所述芯片、部分所述介电层、部分中间层以及全部模塑化合物层之后,所述半导体结构的制作方法还包括:

20、于所述减薄后的所述芯片上键合新的所述芯片,新的所述芯片堆叠于减薄后的所述芯片上,并通过新的所述芯片内的垂直互连结构与减薄后的所述芯片连接。

21、根据本公开的一些实施例,所述模塑化合物层的材料包括环氧塑封料。

22、本公开的实施例提供的技术方案可以包括以下有益效果:通过介电层以及中间层的组合,能够根据选用芯片的不同而改变介电层和中间层的高度,以此实现对多层堆叠芯片的应力调节,减小芯片受填充材料应力而脱落甚至断裂的可能。

23、应当理解的是,以上的一般描述和后文的细节描述仅是示例性和解释性的,并不能限制本公开。在阅读并理解了附图和详细描述后,可以明白其他方面。

技术特征:

1.一种半导体结构,其特征在于,所述半导体结构包括:多个芯片,相邻所述芯片间隔分布,所述芯片之间的空隙依次堆叠有介电层和中间层;

2.根据权利要求1所述的半导体结构,其特征在于,所述中间层的最小高度大于所述介电层的最小高度。

3.根据权利要求1所述的半导体结构,其特征在于,所述芯片堆叠有多层,所述芯片具有垂直互联结构,上层所述芯片与下层所述芯片通过所述垂直互连结构连接,上层所述芯片的一侧的所述介电层覆盖下层所述芯片一侧的所述介电层,并覆盖下层所述芯片一侧的所述中间层。

4.根据权利要求3所述的半导体结构,其特征在于,所述芯片的底面具有金属极,所述金属极与所述垂直互连结构连接,下层所述芯片上的所述垂直互连结构与上层所述芯片底面的金属极连接。

5.根据权利要求1所述的半导体结构,其特征在于,所述半导体结构还包括基底,所述芯片键合于所述基底上,所述介电层覆盖自相邻所述芯片之间暴露的所述基底的顶面。

6.根据权利要求1所述的半导体结构,其特征在于,相邻两芯片之间的所述中间层的宽度随高度的降低而降低。

7.根据权利要求1所述的半导体结构,其特征在于,所述中间层的材料包括旋转涂布玻璃;所述介电层的材料包括二氧化硅或氮化硅或二者的混合物。

8.一种半导体结构的制作方法,其特征在于,所述半导体结构的制作方法包括:

9.根据权利要求8所述的半导体结构的制作方法,其特征在于,所述采用背面减薄工艺去除部分所述芯片、部分所述介电层、部分中间层以及全部模塑化合物层之后,所述半导体结构的制作方法还包括:

10.根据权利要求8所述的半导体结构的制作方法,其特征在于,所述模塑化合物层的材料包括环氧塑封料。

技术总结

本公开是关于一种半导体结构及半导体结构的制作方法,半导体结构包括:所述半导体结构包括:多个芯片,相邻所述芯片间隔分布,所述芯片之间的空隙依次堆叠有介电层和中间层;所述介电层覆盖于所述芯片的顶面和侧面,并将相邻所述芯片之间的空间的底部填充,所述介电层的顶面与所述芯片的顶面平齐;所述中间层填充于所述介电层在相邻所述芯片之间围合的空间,所述中间层的顶面与所述芯片的顶面平齐。本公开通过介电层和中间层的组合,能够根据选用芯片的不同而改变介电层和中间层的高度,以此实现对多层堆叠芯片的应力调节,减小芯片受填充材料应力而脱落甚至断裂的可能。

技术研发人员:毛宇

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!