半导体结构及其制备方法与流程

本公开涉及半导体,特别是涉及一种半导体结构及其制备方法。

背景技术:

1、在沟槽型金属氧化物半导体场效应晶体管(metal oxide semiconductor fieldeffect transistor,简称mosfet)的制造工艺中,栅氧化层和栅极在沟槽内部形成,用来控制mosfet的开与关。因此,栅氧化层和栅极的制备是非常重要的工艺。

2、然而,由于沟槽底部的应力原因,mosfet中沟槽侧壁的栅氧化层比沟槽底部的栅氧化层厚。如此,导致沟槽底部的栅氧化层耐压能力不足,容易被击穿。并且沟槽底部过薄的栅氧化层也容易导致该处的栅漏电容过大,限制了相应半导体器件在高频应用中的使用。

3、因此,如何提高栅氧化层的耐压能力是亟需解决的问题。

技术实现思路

1、基于此,本公开实施例提供了一种半导体结构及其制备方法,以有效提高栅氧化层的耐压能力。

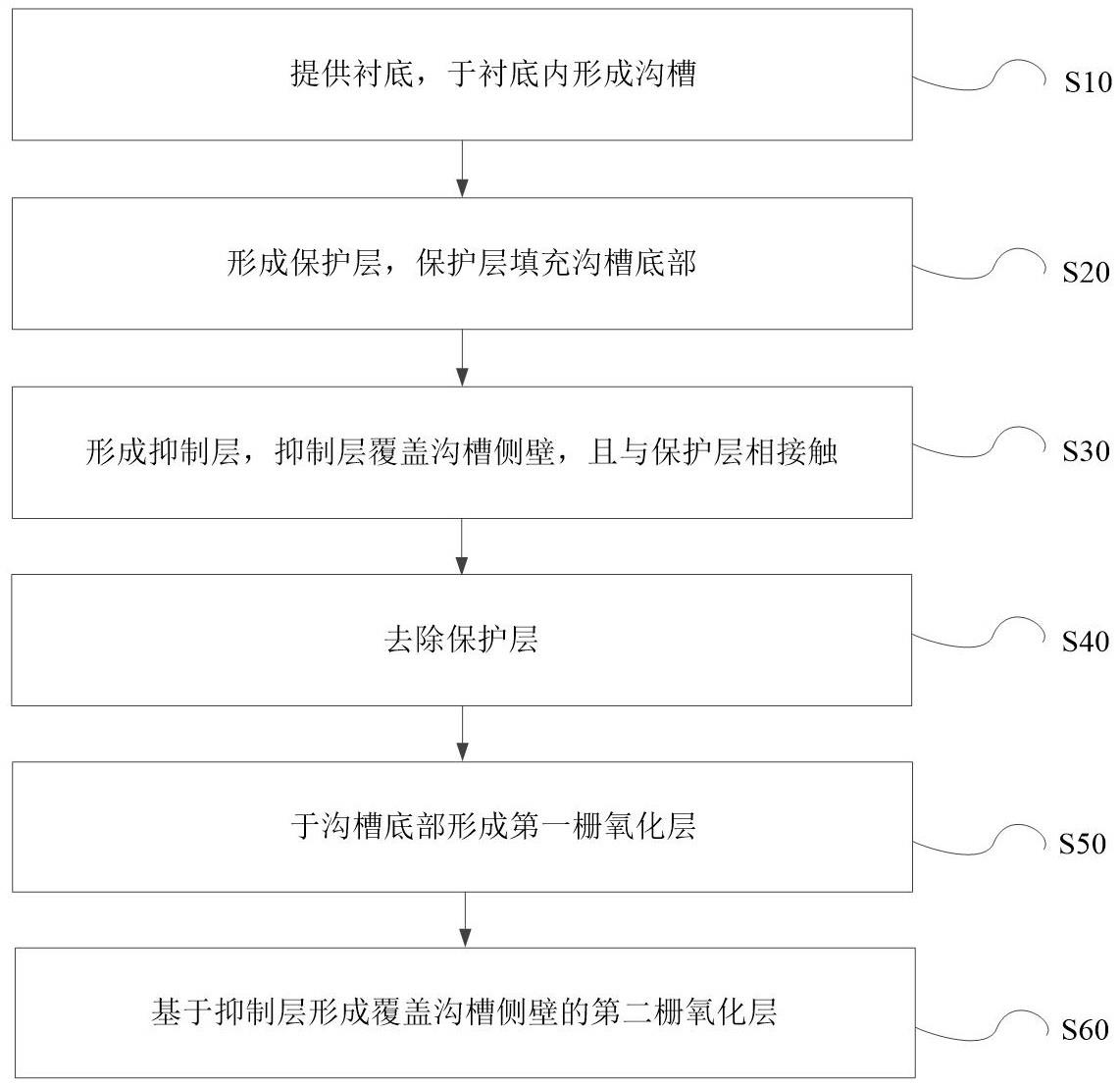

2、本公开一些实施例提供了一种半导体结构的制备方法,包括以下步骤:

3、提供衬底,于衬底内形成沟槽;

4、形成保护层,保护层填充沟槽底部;

5、形成抑制层,抑制层覆盖沟槽侧壁,且与保护层相接触;

6、去除保护层;

7、于沟槽底部形成第一栅氧化层;

8、基于抑制层形成覆盖沟槽侧壁的第二栅氧化层。

9、本公开实施例中,通过先在沟槽底部填充保护层,然后再形成覆盖沟槽侧壁的抑制层,且使抑制层与保护层相接触。意想不到的效果是,在去除保护层后,即可得到只覆盖沟槽侧壁的抑制层。这样可以通过控制抑制层的形成厚度,来控制后续基于抑制层形成的覆盖沟槽侧壁的第二栅氧化层的厚度。如此,可以简单地调整沟槽底部的第一栅氧化层和沟槽侧壁的第二栅氧化层的厚度差。例如,使得沟槽底部形成的第一栅氧化层的厚度大于沟槽侧壁形成的第二栅氧化层的厚度。基于此,通过上述半导体结构的制备方法可以简单地增大沟槽底部的栅氧化层厚度,故改善了沟槽底部的栅氧化层耐压不足的问题,从而降低了沟槽底部的栅漏电容,提升了相应半导体器件的高频性能。

10、可选地,第二栅氧化层通过氧化抑制层形成。

11、可选地,第一栅氧化层采用热氧化工艺形成;第二栅氧化层通过在形成第一栅氧化层的同时同步氧化抑制层形成。

12、本公开实施例中,当采用热氧化工艺对去除保护层后的结构进行氧化时,由于沟槽侧壁覆盖有抑制层,故使得沟槽底部形成的第一栅氧化层的厚度大于沟槽侧壁形成的第二栅氧化层的厚度。如此,增大了沟槽底部的栅氧化层厚度,进一步改善了沟槽底部的栅氧化层耐压不足的问题。

13、可选地,形成第一栅氧化层的氧化速率大于形成第二栅氧化层的氧化速率。如此,可以通过同一热氧化工艺确保沟槽底部形成的第一栅氧化层的厚度大于沟槽侧壁形成的第二栅氧化层的厚度,从而改善了沟槽底部的栅氧化层耐压不足的问题。

14、可选地,形成保护层的步骤包括:

15、形成初始保护层,初始保护层覆盖沟槽侧壁且填充沟槽底部;

16、去除覆盖沟槽侧壁的初始保护层以形成保护层。

17、本公开实施例中,可以通过先于沟槽内形成初始保护层再去除部分初始保护层以暴露出沟槽侧壁的方式,使保留于沟槽底部的初始保护层作为保护层,从而利用保护层定义沟槽底部第一栅氧化层的形成区域。如此,有利于简化保护层的形成工艺,以提高生产效率。

18、可选地,形成初始保护层之前,制备方法还包括:形成修复层,修复层随形覆盖沟槽的内壁。其中,初始保护层形成于修复层背离衬底的表面。所述去除覆盖沟槽侧壁的初始保护层,还包括:去除覆盖沟槽侧壁的修复层。

19、本公开实施例中,先形成修复层,再于修复层背离衬底的表面形成初始保护层。如此,可以利用修复层修复沟槽内壁(包括侧壁和底壁)的表面损伤,从而提高初始保护层的形貌质量。

20、可选地,初始保护层填平沟槽底部,且沟槽底部的初始保护层的最大厚度大于同一位置沟槽底部的高度。形成保护层还包括:在去除覆盖沟槽侧壁的初始保护层时,同步去除沟槽底部的部分初始保护层,以形成保护层。其中,保护层的最大厚度等于或大致等于同一位置沟槽底部的高度。

21、本公开实施例中,初始保护层填平沟槽底部,且沟槽底部的初始保护层的最大厚度大于同一位置沟槽底部的高度,可以确保沟槽底部的初始保护层具有冗余量,以便于后续在去除沟槽侧壁初始保护层的过程中,即使同步去除了沟槽底部的部分初始保护层,还可以确保形成的保护层能够填平沟槽底部,有效保障待形成第一栅氧化层的区域面积。

22、可选地,沟槽底部的初始保护层的厚度与沟槽侧壁上的初始保护层的厚度之比的取值范围包括:7~9。如此,通过合理选择沟槽底部初始保护层与沟槽侧壁上初始保护层的厚度比值,可以有效控制沟槽侧壁上初始保护层和沟槽底部初始保护层去除部分的比值,以便于较好的控制保护层的形貌。

23、可选地,衬底的材料包括硅或高掺杂硅;抑制层的材料包括碳化硅或低掺杂硅。

24、本公开实施例中,衬底的材料为硅或高掺杂硅,抑制层的材料为碳化硅或低掺杂硅,可以保证衬底的氧化速率高于抑制层的氧化速率,以确保沟槽底部形成的第一栅氧化层的厚度大于沟槽侧壁形成的第二栅氧化层的厚度。

25、可选地,形成第二栅氧化层之后,制备方法还包括:采用热氧化工艺,氧化衬底靠近第一栅氧化层和第二栅氧化层的表面,以形成第三栅氧化层。其中,第一栅氧化层、第二栅氧化层和第三栅氧化层共同构成栅氧化层。

26、本公开实施例中,于衬底靠近第一栅氧化层和第二栅氧化层的表面形成第三栅氧化层,可以进一步增加沟槽底部的栅氧化层厚度,从而进一步改善沟槽底部的栅氧化层耐压不足的问题。

27、基于同样的发明构思,本公开实施例还提供了一种半导体结构,采用上述一些实施例中的制备方法获得。该半导体结构包括:衬底、第一栅氧化层以及第二栅氧化层。衬底内具有沟槽。第一栅氧化层填充于沟槽底部。第二栅氧化层覆盖沟槽侧壁,并与第一栅氧化层相连接。其中,第一栅氧化层的厚度大于第二栅氧化层的厚度;第一栅氧化层和第二栅氧化层共同构成栅氧化层。

28、本公开实施例中,半导体结构采用如上结构,该半导体结构所能实现的技术效果与前述实施例中半导体结构的制备方法所能具有的技术效果相同,此处不再详述。

29、可选地,半导体结构还包括:第三栅氧化层。第三栅氧化层位于衬底和第一栅氧化层之间,以及衬底和第二栅氧化层之间。其中,第一栅氧化层、第二栅氧化层和第三栅氧化层共同构成栅氧化层。

30、本公开实施例中,位于衬底和第一栅氧化层之间,以及衬底和第二栅氧化层之间的第三栅氧化层,进一步增加了沟槽底部的栅氧化层厚度,从而进一步改善了沟槽底部的栅氧化层耐压不足的问题。

31、如上所述,本公开实施例提供的半导体结构及其制备方法,通过先在沟槽底部填充保护层,然后再形成覆盖沟槽侧壁的抑制层,且使抑制层与保护层相接触的方式,可以在去除保护层并形成栅氧化层后获得意想不到的效果为:简单有效增大沟槽底部的栅氧化层厚度,以改善沟槽底部的栅氧化层耐压不足的问题,从而降低了沟槽底部的栅漏电容,并提升相应半导体器件的高频性能;并且,保护层基于填充沟槽底部获得,也利于简化半导体结构的制备工艺,以提升生产效率。

- 还没有人留言评论。精彩留言会获得点赞!