半导体器件及其制造方法与流程

本公开涉及半导体器件及其制造方法,更具体地,涉及包括测试焊盘的半导体器件及其制造方法。

背景技术:

1、半导体器件因其小尺寸、多功能特性和/或低制造成本而广泛用于电子工业。半导体器件可以被分类为用于存储逻辑数据的半导体存储器件、用于处理逻辑数据的半导体逻辑器件、以及具有半导体存储器件的功能和半导体逻辑器件的功能两者的混合半导体器件中的任何一种。

2、随着对高速和/或低功率电子装置的需求,对其中使用的高速和/或低电压半导体器件也有需求,并要求高度集成的半导体器件满足这些需求。然而,随着半导体器件的集成密度增加,半导体器件的电特性和产量会降低。因此,已经对用于改善半导体器件的电特性和产量的技术进行了各种各样的研究。

技术实现思路

1、本公开的主题涉及具有改善的电气特性和可靠性的半导体器件及其制造方法。例如,在混合接合技术中,上芯片和下芯片能够被连接,例如,它们之间没有间隙,没有中间物。然而,可能会发生微断开,例如晶粒不连接。在具有混合接合的半导体器件中,检测上芯片和下芯片之间的微断开可能是困难的,因为微断开的大小可能取决于测试温度。例如,在相对低的测试温度,由于下芯片和上芯片热收缩,下芯片和上芯片可能沿着下芯片和上芯片的整个界面断开。相比之下,在相对高的测试温度,由于下芯片和上芯片热膨胀,仅断开的段(segment)会沿着彼此面对的下芯片和上芯片的界面出现。

2、测试焊盘,其能够代替用于混合cu接合的普通焊盘,可以位于芯片边缘或拐角中,与芯片中心相比,在芯片边缘或拐角处,微断开的可能性更高,因为由下芯片和上芯片中的另一个施加在每个上的力趋向于朝向中心最大。测试焊盘可以大于普通焊盘,以增强凹陷(dishing),例如,彼此面对的上芯片和下芯片的表面形成凹面。延伸超过下芯片和上芯片的宽度的测试焊盘不对半导体器件的性能产生负面影响。

3、检测上芯片和下芯片之间的微断开的能力能够有助于补救微断开,其能够提高半导体器件的电气特性的可靠性和均匀性。此外,所公开的构思有利地在测试过程中不需要额外的步骤,因为在典型的测试步骤中,单个测试焊盘能够替换为普通焊盘。

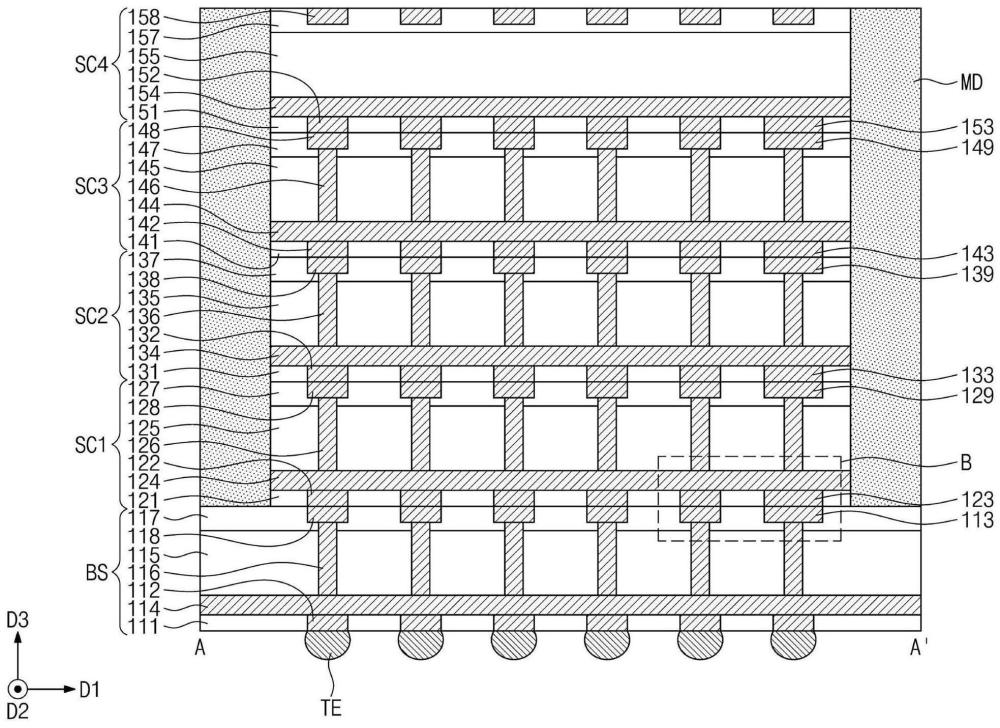

4、在一方面,一种半导体器件可以包括:基底结构,包括第一接合焊盘和第一测试焊盘;以及半导体芯片,包括与基底结构的第一接合焊盘接触的第二接合焊盘以及与基底结构的第一测试焊盘接触的第二测试焊盘。半导体芯片的第二接合焊盘的宽度可以小于半导体芯片的第二测试焊盘的宽度。可以在基底结构的第一测试焊盘和半导体芯片的第二测试焊盘之间提供气隙。

5、在一方面,一种半导体器件可以包括:第一绝缘结构;在第一绝缘结构中的第一接合焊盘;在第一绝缘结构中的第一测试焊盘;在第一绝缘结构上的第二绝缘结构;第二接合焊盘,其提供在第二绝缘结构中并与第一接合焊盘接触;以及第二测试焊盘,其提供在第二绝缘结构中并与第一测试焊盘接触。第二接合焊盘的宽度可以小于第二测试焊盘的宽度。第二测试焊盘可以具有与第一测试焊盘接触的接触表面和与第一测试焊盘间隔开的暴露表面。暴露表面可以比接触表面更靠近第二测试焊盘的侧表面。

6、在一方面,一种半导体器件可以包括:基底结构,包括第一接合焊盘和第一测试焊盘;以及半导体芯片,包括与基底结构的第一接合焊盘接触的第二接合焊盘以及与基底结构的第一测试焊盘接触的第二测试焊盘。半导体芯片的第二接合焊盘的宽度可以小于半导体芯片的第二测试焊盘的宽度。基底结构的第一接合焊盘的宽度可以小于基底结构的第一测试焊盘的宽度。可以在基底结构的第一测试焊盘和半导体芯片的第二测试焊盘之间提供气隙。气隙可以邻接第一测试焊盘的一部分和第二测试焊盘的一部分。

技术特征:

1.一种半导体器件,包括:

2.根据权利要求1所述的半导体器件,其中,所述基底结构的所述第一接合焊盘沿所述第一方向的宽度小于所述基底结构的所述第一测试焊盘沿所述第一方向的宽度。

3.根据权利要求1所述的半导体器件,其中,所述半导体芯片包括中心区域和围绕所述中心区域的周围区域,

4.根据权利要求1所述的半导体器件,其中,所述半导体芯片的所述第二测试焊盘比所述半导体芯片的所述第二接合焊盘更靠近所述半导体芯片的侧表面。

5.根据权利要求1所述的半导体器件,其中:

6.根据权利要求5所述的半导体器件,其中,所述气隙邻接所述接触表面。

7.根据权利要求5所述的半导体器件,其中,所述气隙的最上部分的高度高于所述接触表面的高度,以及

8.根据权利要求1所述的半导体器件,其中,所述半导体芯片的所述第二测试焊盘包括:导电层;以及部分地围绕所述导电层的阻挡层,以及

9.一种半导体器件,包括:

10.根据权利要求9的半导体器件,其中,所述第一和第二绝缘结构包括:中心区域;和围绕所述中心区域的周围区域,

11.根据权利要求10所述的半导体器件,其中,所述第二测试焊盘包括多个第二测试焊盘,以及

12.根据权利要求9所述的半导体器件,其中,所述第二测试焊盘包括沿着所述第一方向具有不同宽度的多个第二测试焊盘。

13.根据权利要求9所述的半导体器件,其中,所述第二测试焊盘的形状不同于所述第二接合焊盘的形状。

14.根据权利要求13所述的半导体器件,其中,当在平面图中观察时,所述第二测试焊盘具有多边形形状。

15.根据权利要求9所述的半导体器件,其中,所述第二测试焊盘包括:导电层和部分地围绕所述导电层的阻挡层,以及

16.根据权利要求15所述的半导体器件,其中,所述第二测试焊盘的所述阻挡层的底表面与所述第一测试焊盘间隔开。

17.根据权利要求9所述的半导体器件,其中,所述接触表面是平的,以及

18.根据权利要求9所述的半导体器件,其中,所述暴露表面限定气隙。

19.一种半导体器件,包括:

20.根据权利要求19所述的半导体器件,其中:

技术总结

一种半导体器件包括:基底结构,其包括第一接合焊盘和第一测试焊盘;以及半导体芯片,其包括与基底结构的第一接合焊盘接触的第二接合焊盘和与基底结构的第一测试焊盘接触的第二测试焊盘。半导体芯片的第二接合焊盘的宽度小于半导体芯片的第二测试焊盘的宽度。在基底结构的第一测试焊盘和半导体芯片的第二测试焊盘之间提供气隙。

技术研发人员:金暋起,白承德,李赫宰

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/25

- 还没有人留言评论。精彩留言会获得点赞!