芯片及芯片堆叠结构的制作方法

本发明涉及集成电路,特别是涉及一种芯片及芯片堆叠结构。

背景技术:

1、为了实现更高的晶体管集成度,多个半导体芯片自下而上依次堆叠在半导体衬底上,半导体芯片与半导体衬底之间、以及半导体芯片相互之间通过引线键合元件进行连接,并且在半导体芯片内部通过硅通孔(英文:through silicon via,简称:tsv)将半导体芯片内部的金属互连线与引线键合元件连接起来,从而实现半导体芯片相互之间的通信。

2、然而,经过一定时间的使用,半导体芯片内部的硅通孔性能将会退化,可能会造成半导体芯片失效。

技术实现思路

1、基于此,有必要提供一种避免部分硅通孔的性能退化而造成整个半导体芯片失效的芯片及芯片堆叠结构。

2、第一方面,提供了一种芯片,所述芯片包括:

3、芯片本体;

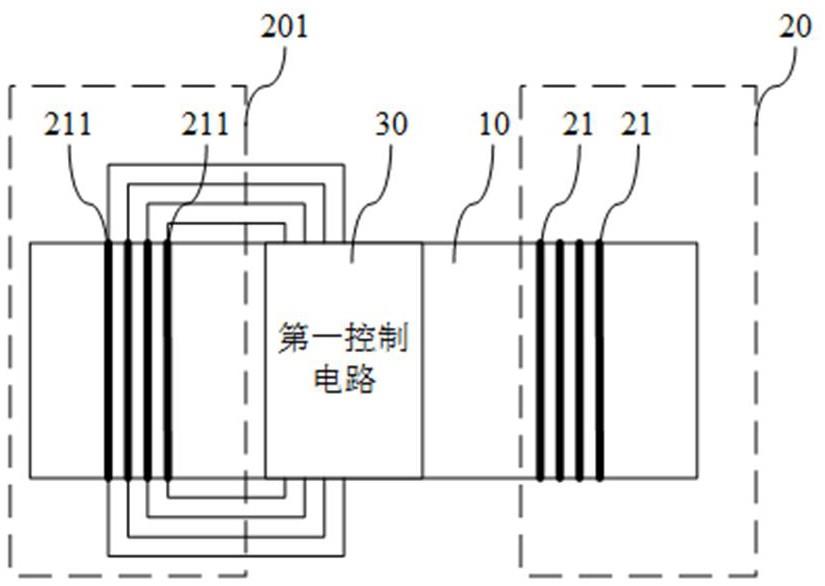

4、互连结构,包括多个贯穿所述芯片本体且彼此间隔设置的互连元件;至少一个所述互连结构为第一互连结构,所述第一互连结构中的所述互连元件为第一互连元件;

5、第一控制电路,设置于所述芯片本体内;所述第一控制电路的输入端与一个所述第一互连结构的每一所述第一互连元件的第一端分别连接,所述第一控制电路的输出端与同一所述第一互连结构的每一所述第一互连元件的第二端分别连接;所述第一控制电路用于根据选择信号将一个所述第一互连元件的第一端接收的信号传输至另一所述第一互连元件的第二端。

6、在其中一个实施例中,所述第一控制电路包括:

7、第一选择模块,包括多个输入端和一个输出端;所述第一选择模块的各个输入端与一个所述第一互连结构的各个所述第一互连元件的第一端一一连接;所述第一选择模块用于根据所述选择信号将所述第一选择模块的一个输入端接收的信号从所述第一选择模块的输出端输出;

8、第二选择模块,包括一个输入端和多个输出端;所述第二选择模块的输入端与所述第一选择模块的输出端连接,所述第二选择模块的各个输出端与同一所述第一互连结构的各个所述第一互连元件的第二端一一连接;所述第二选择模块用于根据所述选择信号将所述第一选择模块输出的信号从所述第二选择模块的一个输出端输出。

9、在其中一个实施例中,所述第一控制电路还包括:

10、第一输出端口,与所述第一选择模块的输出端连接;所述第一输出端口用于将所述第一选择模块输出的信号传输至所述芯片本体中。

11、在其中一个实施例中,所述第一控制电路包括多个所述第一选择模块、多个所述第二选择模块和多个所述第一输出端口,多个所述第一选择模块分别与多个所述第二选择模块和多个所述第一输出端口一一连接。

12、在其中一个实施例中,至少一个所述互连结构为第二互连结构,所述第二互连结构中的所述互连元件为第二互连元件。

13、在其中一个实施例中,所述第一互连结构的各个所述第一互连元件用于接收的信号,与所述第二互连结构的各个所述第二互连元件用于接收的信号一一相同。

14、在其中一个实施例中,所述第一互连结构的各个所述第一互连元件用于接收的信号,与所述第二互连结构的各个所述第二互连元件用于接收的信号各不相同。

15、在其中一个实施例中,所述芯片还包括:

16、第二控制电路,设置于所述芯片本体内;所述第二控制电路的输入端与一个所述第二互连结构的每一所述第二互连元件分别连接,所述第二控制电路用于根据选择信号将至少一个所述第二互连元件接收的信号传输至所述芯片本体中。

17、在其中一个实施例中,所述第二控制电路包括:

18、第三选择模块,包括多个输入端和一个输出端;所述第三选择模块的各个输入端与一个所述第二互连结构的各个所述第二互连元件一一连接;所述第三选择模块用于根据所述选择信号将所述第三选择模块的一个输入端接收的信号从所述第三选择模块的输出端输出;

19、第二输出端口,与所述第三选择模块的输出端连接;所述第二输出端口用于将所述第三选择模块输出的信号传输至所述芯片本体中。

20、在其中一个实施例中,所述第二控制电路包括多个所述第三选择模块和多个所述第二输出端口,多个所述第三选择模块与多个所述第二输出端口一一连接。

21、在其中一个实施例中,所述第二控制电路还包括:

22、第三输出端口,输入端与所述第一选择模块的输出端连接,输出端与所述第二输出端口的输出端连接;所述第三输出端口用于将所述第一选择模块输出的信号传输至所述芯片本体中。

23、在其中一个实施例中,所述第二输出端口用于根据第一控制信号将所述第三选择模块输出的信号传输至所述芯片本体中,所述第三输出端口用于根据第二控制信号将所述第一选择模块输出的信号传输至所述芯片本体中,所述第一控制信号和所述第二控制信号相反。

24、第二方面,提供了一种芯片堆叠结构,所述芯片堆叠结构包括基板和多个如第一方面提供的芯片,多个所述芯片沿第一方向层叠设置在所述基板上,相邻两个所述芯片的所述互连结构的各个所述互连元件一一连接。

25、在其中一个实施例中,至少一个所述互连结构为第二互连结构,所述第二互连结构中的所述互连元件为第二互连元件;

26、每一所述芯片的所述第一互连结构的各个所述第一互连元件与相邻所述芯片的所述第二互连结构的各个所述第二互连元件连接。

27、在其中一个实施例中,所述芯片堆叠结构还包括:

28、第三控制电路,设置于所述基板内;与所述基板相邻的所述芯片的各个所述互连元件分别与所述第三控制电路连接;所述第三控制电路用于根据所述选择信号将所述第三控制电路接收的信号传输至连接的至少一个所述互连元件。

29、在其中一个实施例中,所述第三控制电路包括:

30、输入端口,用于接收传输至所述基板的信号;

31、第四选择模块,包括一个输入端和多个输出端;所述第四选择模块的输入端与所述输入端口连接,与所述基板相邻的所述芯片的各个所述互连元件与所述第四选择模块的各个输出端一一连接;所述第四选择模块用于根据所述选择信号将所述输入端口接收的信号从所述第四选择模块的一个输出端输出。

32、在其中一个实施例中,所述第三控制电路包括多个所述输入端口和多个所述第四选择模块,多个所述输入端口和多个所述第四选择模块一一连接。

33、上述芯片及芯片堆叠结构,包括芯片本体、互连结构和第一控制电路,互连结构包括多个贯穿芯片本体且彼此间隔设置的互连元件,至少一个互连结构为第一互连结构,第一互连结构中的互连元件为第一互连元件,第一控制电路设置于芯片本体内,第一控制电路的输入端与一个第一互连结构的每一第一互连元件的第一端分别连接,第一控制电路的输出端与同一第一互连结构的每一互连元件的第二端分别连接,第一控制电路根据选择信号将一个第一互连元件的第一端接收的信号传输至另一第一互连元件的第二端,可以在一个第一互连元件由于使用出现性能退化时,利用第一控制电路将其传输的信号切换至另一互连元件进行传输,从而避免部分硅通孔的性能退化而造成整个半导体芯片失效。

- 还没有人留言评论。精彩留言会获得点赞!