一种具有渐变凹槽终端的高电子迁移率晶体管及制备方法

本发明涉及半导体材料制备,具体涉及一种具有渐变凹槽终端的高电子迁移率晶体管及制备方法。

背景技术:

1、随着新能源技术的发展,电力电子系统不断向着高效、大功率的方向发展,这也对功率器件提出了更高的要求,为了满足功率电子小型化、高效化的需求,有必要对其性能进行进一步提升。氮化镓器件由于其优异的材料特性成为新一代功率器件的主角,如何进一步提高氮化镓高电子迁移率晶体管的功率性能,提升其稳定性成为研究重点。目前主流的氮化镓功率器件主要有两种,p型栅增强型以及cascode(级联)型,p型栅器件通过势垒层上方、栅极下方的p型氮化镓帽层耗尽沟道中的电子,这一方案需要刻蚀掉非栅区域的p型氮化镓帽层,不可避免地引入刻蚀损伤,影响器件表现;而级联型通过耗尽型氮化镓器件与增强型硅功率管连接实现增强型,由于异质结特性,在未加外界偏压的时候器件即为耗尽型,不需要刻蚀处理,这也使得其饱和输出电流较高,如何进一步提升耗尽型器件的性能成为问题的关键。

2、常规的gan基hemt(high electron mobility transistor,高电子迁移率晶体管)的栅极为肖特基接触,存在较大的泄漏电流,导致静态功耗很大,而且导通状态下会导致栅极驱动电压不足。通常多沟道材料制备的器件具有负的阈值电压,为耗尽型器件,在应用中可以采用cascode结构,将多沟道耗尽型gan器件与增强型si器件连接起来,利用si器件的关断实现增强型。

3、但是,常规材料结构的高电子迁移率晶体管器件中,二维电子气面密度较小,不利于实现低导通电阻,导致电路应用中存在损耗。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种具有渐变凹槽终端的高电子迁移率晶体管及制备方法。本发明要解决的技术问题通过以下技术方案实现:

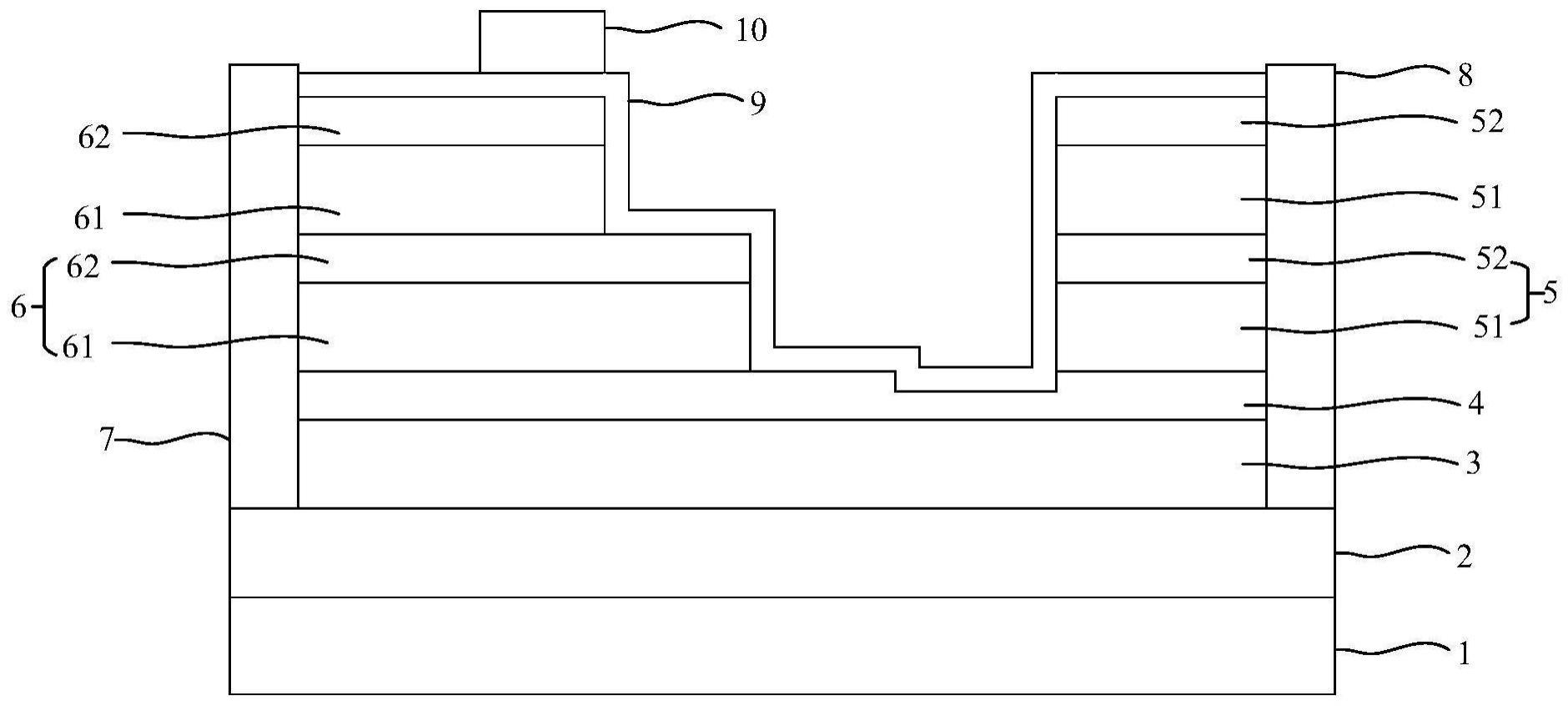

2、一种具有渐变凹槽终端的高电子迁移率晶体管,所述高电子迁移率晶体管包括:

3、从下至上依次层叠设置的衬底层、缓冲层、第一异质结结构,所述第一异质结结构包括从下至上依次层叠设置的第一沟道层和第一势垒层,其中,在所述第一势垒层上设置有凹槽;

4、第一组合层,所述第一组合层包括n层依次层叠设置在部分所述第一势垒层的第一组合子层,每层所述第一组合子层包括从下至上依次层叠设置的第二势垒层和第二沟道层;

5、第二组合层,所述第二组合层包括n层依次层叠设置在部分所述第一势垒层的第二组合子层,每层所述第二组合子层包括从下至上依次层叠设置的第三势垒层和第三沟道层,其中,从最下层的第1层第二组合子层至最上层的第n层第二组合子层中靠近所述第一组合层的一端呈层阶梯状结构设置,且所述第一势垒层的凹槽设置在所述第一组合层和所述第二组合层之间;

6、源极,设置在所述缓冲层上,与所述第二组合层的侧面相接触,且位于远离所述第一组合层的一侧;

7、漏极,设置在所述缓冲层上,与所述第一组合层的侧面相接触,且位于远离所述第二组合层的一侧;

8、介质层,连续的设置在每一层所述第二组合子层的台阶面上、所述第一势垒层的上表面、所述第一势垒层的凹槽内和所述第一组合层的上表面;

9、栅极,设置在所述第n层第二组合子层上方的介质层上。

10、在本发明的一个实施例中,所述第一势垒层的凹槽的一侧面与所述第一组合层的一侧面在同一平面,所述第一势垒层的凹槽与所述第二组合层间隔设置。

11、在本发明的一个实施例中,所有所述第一沟道层、所述第二沟道层和所述第三沟道层的厚度相同,所有所述第二沟道层的宽度均相同,所有所述第一势垒层、所述第二势垒层和所述第三势垒层的厚度相同,所有所述第二势垒层的宽度均相同。

12、在本发明的一个实施例中,所述第一沟道层、所述第二沟道层和所述第三沟道层的材料相同,所述第一势垒层、所述第二势垒层和所述第三势垒层的材料相同。

13、在本发明的一个实施例中,所述第一沟道层、所述第二沟道层和所述第三沟道层的材料包括gan,所述第一势垒层、所述第二势垒层和所述第三势垒层的材料包括algan或inaln。

14、在本发明的一个实施例中,所述高电子迁移率晶体管还包括若干层第二异质结结构,所述若干层第二异质结结构从下至上依次层叠设置在所述缓冲层与所述第一异质结结构之间,所述第二异质结结构包括从下至上依次层叠设置的第四沟道层和第四势垒层。

15、在本发明的一个实施例中,所述介质层的材料包括al2o3或sio2。

16、本发明实施例还提供一种具有渐变凹槽终端的高电子迁移率晶体管的制备方法,所述制备方法用于制备上述任一项实施例所述的高电子迁移率晶体管,所述制备方法包括:

17、选取衬底层;

18、在所述衬底层上生长缓冲层;

19、在所述缓冲层上生长第一沟道层;

20、在所述第一沟道层上生长第一势垒层;

21、在所述第一势垒层上依次生长交替层叠设置的n层沟道层和n层势垒层;

22、去除两端的所述第一沟道层、所述第一势垒层、所述沟道层和所述势垒层,以暴露两端的所述缓冲层,在所述缓冲层的两端所暴露的部分上分别制备源极和漏极;

23、刻蚀n层沟道层和n层势垒层,以形成靠近所述漏极侧的n层第二沟道层和n层第二势垒层,以及,靠近所述源极侧的n层第三沟道层和n层第三势垒层,其中,第n层第二沟道层和第n层第二势垒层组成第一组合子层,n层第一组合子层组成第一组合层,第n层第三沟道层和第n层第三势垒层组成第二组合子层,n层第二组合子层组成第一组合层,从最下层的第1层第二组合子层至最上层的第n层第二组合子层中靠近所述第一组合层的一端呈层阶梯状结构设置,且所述第一势垒层的凹槽设置在所述第一组合层和所述第二组合层之间;

24、刻蚀所述第一势垒层表面,以在所述第一势垒层上形成凹槽;

25、在每一层所述第二组合子层的台阶面上、所述第一势垒层的上表面、所述第一势垒层的凹槽内和所述第一组合层的上表面生长连续的介质层;

26、在所述第n层第二组合子层上方的介质层上制备栅极。

27、在本发明的一个实施例中,所述第一势垒层的凹槽的一侧面与所述第一组合层的一侧面在同一平面,所述第一势垒层的凹槽与所述第二组合层间隔设置。

28、在本发明的一个实施例中,所有所述第一沟道层、所述第二沟道层和所述第三沟道层的厚度相同,所有所述第二沟道层的宽度均相同,所有所述第一势垒层、所述第二势垒层和所述第三势垒层的厚度相同,所有所述第二势垒层的宽度均相同。

29、与现有技术相比,本发明的有益效果在于:

30、本发明提供一种具有渐变凹槽终端的多沟道绝缘栅高电子迁移率晶体管,该高电子迁移率晶体管的一端设置有包括n层依次层叠设置在部分第一势垒层的第一组合子层,该第一组合子层包括从下至上依次层叠设置的第二势垒层和第二沟道层,同时,在另一端设置有包括n层依次层叠设置在部分第一势垒层的第二组合子层,该第二组合子层包括从下至上依次层叠设置的第三势垒层和第三沟道层,并且从最下层的第1层第二组合子层至最上层的第n层第二组合子层中靠近第一组合层的一端呈层阶梯状结构设置,由此可以在器件的栅极靠漏极边缘处引入渐变凹槽深度的终端结构来分散电场峰值,使得偏压较高时器件中的电场分布更加均匀,进而实现更高的击穿电压。

31、以下将结合附图及实施例对本发明做进一步详细说明。

- 还没有人留言评论。精彩留言会获得点赞!