半导体结构的制备方法及半导体结构与流程

本发明涉及半导体,半导体结构的制备方法及半导体结构。

背景技术:

1、缩小器件的尺寸是提升半导体器件集成密度的重要方式。随着晶体管尺寸的逐渐微缩,量子隧穿效应也将无法忽视,这会导致栅极与沟道之间存在漏电流的问题。采用高k材料作为栅介质材料能够降低漏电流的问题,但是这又会导致沟道的载流子迁移率下降,影响晶体管的性能。沟道的载流子迁移率性能可以通过在衬底上制备特定的外延层进行改善。在实际的器件制备过程中,通常需要涉及多层外延层的制备,但是多层外延层的性能往往难以兼顾,导致其制备难度较高。

技术实现思路

1、基于此,为了降低半导体器件中的多层外延层的制备难度,有必要提供一种半导体结构的制备方法。

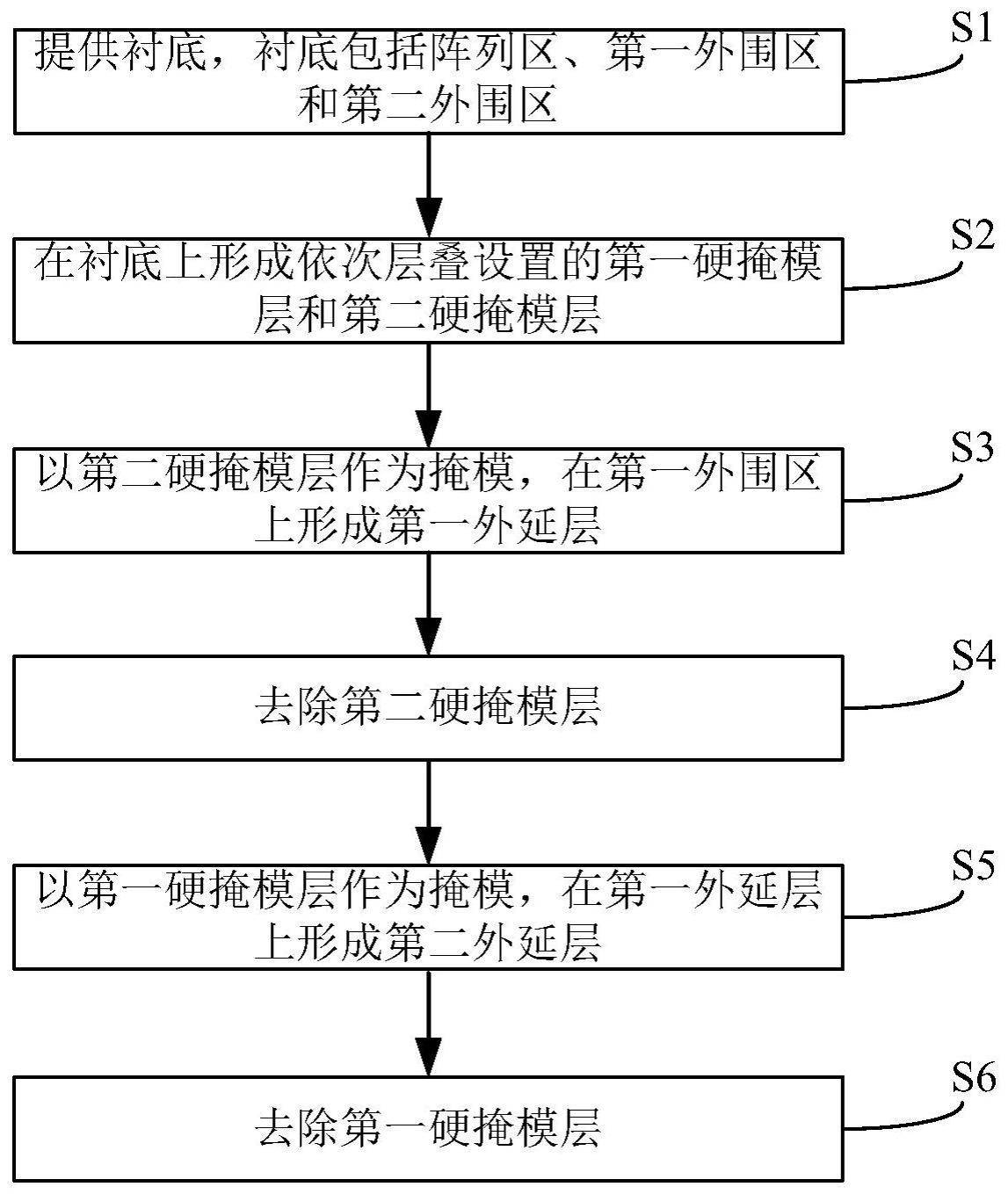

2、根据本公开的一些实施例,提供了一种半导体结构的制备方法,其包括:

3、提供衬底,所述衬底包括阵列区、第一外围区和第二外围区;

4、在所述衬底上形成依次层叠的第一硬掩模层和第二硬掩模层,所述第一硬掩模层和所述第二硬掩模层均具有露出所述第一外围区的开口,所述第一硬掩模层的材料不同于所述第二硬掩模层的材料;

5、以所述第二硬掩模层为掩模,在所述第一外围区上形成第一外延层,所述第一外延层的材料不同于所述衬底的材料;

6、去除所述第二硬掩模层;

7、以所述第一硬掩模层为掩模,在所述第一外延层上形成第二外延层,所述第二外延层的材料不同于所述第一外延层的材料;以及,

8、去除所述第一硬掩模层。

9、在本公开的一些实施例中,在所述衬底上形成依次层叠的所述第一硬掩模层和所述第二硬掩模层,包括:

10、在所述衬底上形成依次层叠的第一硬掩模材料层、第二硬掩模材料层和第三硬掩模材料层,所述第三硬掩模材料层的材料与所述第一硬掩模材料层的材料相同;

11、在所述第三硬掩模材料层上形成图案化的第一光刻胶层,所述第一光刻胶层具有露出位于所述第一外围区上的所述第三硬掩模材料层的开口;

12、以所述第一光刻胶层为掩模,采用湿法刻蚀去除位于所述第一外围区上的所述第三硬掩模材料层,以保留的所述第三硬掩模材料层作为第三硬掩模层;

13、去除所述第一光刻胶层;

14、以所述第三硬掩模层为掩模,采用湿法刻蚀去除所述第一外围区上的所述第二硬掩模材料层,以保留的所述第二硬掩模材料层作为所述第二硬掩模层;

15、采用湿法刻蚀去除所述第三硬掩模层和所述第一外围区上的所述第一硬掩模材料层,以保留的所述第一硬掩模材料层作为所述第一硬掩模层。

16、在本公开的一些实施例中,所述第一硬掩模材料层的厚度与所述第三硬掩模材料层的厚度的比值大于或等于1,且小于或等于1.1。

17、在本公开的一些实施例中,在去除所述第一硬掩模层之后,还包括:

18、在所述衬底上形成依次层叠的第一介质层和第二介质层,所述第一介质层和所述第二介质层中均设置有露出位于所述第一外围区上的所述第二外延层以及露出所述第二外围区的开口;

19、对所述第二外延层进行氧化处理,使所述第二外延层转化为第一栅氧化层,并在所述第二外围区上形成第二栅氧化层;

20、在所述第一栅氧层上形成第一栅极结构,在所述第一栅极结构的相对两侧形成p型源漏区,以形成p型晶体管,所述p型晶体管的沟道区包括所述第一外延层;

21、在所述第二栅氧层上形成第二栅极结构,在所述第二栅极结构的相对两侧形成n型源漏区,以形成n型晶体管,所述n型晶体管的沟道区位于所述衬底内。

22、在本公开的一些实施例中,在所述衬底上形成依次层叠的所述第一介质层和所述第二介质层,包括:

23、在所述衬底上形成依次层叠的第一介质材料层、第二介质材料层和第三介质材料层,所述第三介质材料层的材料与所述第一介质材料层的材料相同;

24、在所述第三介质材料层上形成图案化的第二光刻胶层,所述第二光刻胶层具有露出位于所述第一外围区和所述第二外围区上的所述第三介质材料层的开口;

25、以所述第二光刻胶层为掩模,采用湿法刻蚀去除位于所述第一外围区和所述第二外围区上的所述第三介质材料层,以保留的所述第三介质材料层作为第三介质层;

26、去除所述第二光刻胶层;

27、以所述第三介质层为掩模,采用湿法刻蚀去除位于所述第一外围区和所述第二外围区上的所述第二介质材料层,以保留的所述第二介质材料层作为所述第二介质层;

28、采用湿法刻蚀去除所述第三介质层以及位于所述第一外围区和所述第二外围区上的所述第一介质材料层,以保留的所述第一介质材料层作为所述第一介质层。

29、在本公开的一些实施例中,所述第一介质材料层的厚度与所述第三介质材料层的厚度的比值大于或等于1,且小于或等于1.1。

30、在本公开的一些实施例中,所述第一介质层的材料包括氧化硅,所述第二介质层的材料包括氮化硅和氮氧化硅中的一种或多种。

31、在本公开的一些实施例中,以所述第一硬掩模层为掩模,在所述第一外延层上形成所述第二外延层,包括:

32、在所述第一外延层和所述第一硬掩模层上形成第二外延材料层,位于所述第一外延层上的所述第二外延材料层为单晶态,位于所述第一硬掩模层上的所述第二外延材料层为多晶态;

33、选择性去除位于所述第一硬掩模层上的所述第二外延材料层,保留位于所述第一外延层上的所述第二外延材料层,以保留的所述第二外延材料层作为所述第二外延层。

34、在本公开的一些实施例中,所述衬底的材料包括硅,所述第一外延层的材料包括硅锗,所述第二外延层的材料包括硅,所述第一硬掩模层的材料包括氧化硅,所述第二硬掩模层的材料包括氮化硅和氮氧化硅中的一种或多种。

35、在本公开的一些实施例中,所述阵列区中形成有埋入式晶体管。

36、在本公开的一些实施例中,所述第一外延层的厚度为7-15nm。

37、在本公开的一些实施例中,所述第二外延层的厚度为3-7nm。

38、传统技术中通常仅采用一层掩模以完成多层外延层的制备。但是本公开在研究过程中发现,外延层的性能和生长时所用的掩模存在较为密切的关系。本公开提供的半导体结构的制备方法中,创造性地提出了采用多层掩模,先采用第二硬掩模层制备第一外延层,再采用第一硬掩模层制备第二外延层,从而使得第一外延层和第二外延层都能够在更为合适的掩模中制备,从而更易于兼顾第一外延层和第二外延层的性能。这不仅使得制备的各层外延层的性能均较好,同时还能够降低制备多层外延层对于工艺窗口的要求,从而使得半导体器件中的多层外延层的制备难度得到降低。

39、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,并可依照说明书的内容予以实施,以下以本发明的较佳实施例并配合附图详细说明如后。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的半导体结构的制备方法,其特征在于,在所述衬底上形成依次层叠的所述第一硬掩模层和所述第二硬掩模层,包括:

3.根据权利要求2所述的半导体结构的制备方法,其特征在于,所述第一硬掩模材料层的厚度与所述第三硬掩模材料层的厚度的比值大于或等于1,且小于或等于1.1。

4.根据权利要求1~3任意一项所述的半导体结构的制备方法,其特征在于,在去除所述第一硬掩模层之后,还包括:

5.根据权利要求4所述的半导体结构的制备方法,其特征在于,在所述衬底上形成依次层叠的所述第一介质层和所述第二介质层,包括:

6.根据权利要求5所述的半导体结构的制备方法,其特征在于,所述第一介质材料层的厚度与所述第三介质材料层的厚度的比值大于或等于1,且小于或等于1.1。

7.根据权利要求5所述的半导体结构的制备方法,其特征在于,所述第一介质层的材料包括氧化硅,所述第二介质层的材料包括氮化硅和氮氧化硅中的一种或多种。

8.根据权利要求1~3及5~7任意一项所述的半导体结构的制备方法,其特征在于,以所述第一硬掩模层为掩模,在所述第一外延层上形成所述第二外延层,包括:

9.根据权利要求1~3及5~7任意一项所述的半导体结构的制备方法,其特征在于,所述衬底的材料包括硅,所述第一外延层的材料包括硅锗,所述第二外延层的材料包括硅,所述第一硬掩模层的材料包括氧化硅,所述第二硬掩模层的材料包括氮化硅和氮氧化硅中的一种或多种;和/或,

10.根据权利要求1~3任意一项所述的半导体结构的制备方法,其特征在于,所述第一外延层的厚度为7-15nm;和/或,

技术总结

本公开提供了一种半导体结构的制备方法,其包括:提供衬底,衬底包括阵列区、第一外围区和第二外围区;在衬底上形成依次层叠的第一硬掩模层和第二硬掩模层,第一硬掩模层和第二硬掩模层均具有露出第一外围区的开口,第一硬掩模层的材料不同于第二硬掩模层的材料;以第二硬掩模层为掩模,在第一外围区上形成第一外延层,第一外延层的材料不同于衬底的材料;去除第二硬掩模层;以第一硬掩模层为掩模,在第一外延层上形成第二外延层,第二外延层的材料不同于第一外延层的材料;以及,去除第一硬掩模层。

技术研发人员:刘欣然,徐亚超,张瑞奇,严勋

受保护的技术使用者:长鑫科技集团股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!