一种存储器的多层级三维封装结构及制作方法与流程

本发明属于三维封装,具体涉及一种存储器的多层级三维封装结构及制作方法。

背景技术:

1、存储器作为计算机的记忆系统,是计算机系统不可或缺的部分。随着技术的不断革新发展,航空、航天的运载、武器等领域不断要求更快、更小、更轻的计算机主体部分。因此,系统集成技术蓬勃发展,各种组装、封装技术不断涌现。使得计算机系统向微型化、轻型化发展。近年来,在这种刚性需求的驱使下,存储器也向着大容量小尺寸发展。为了扩充存储器容量,出现了存储器裸芯片叠片组装的工艺,但简单的裸芯片叠层数量受限,一般用于正式产品(非研制品)的裸芯片堆叠层数为两层。如果强制增加叠层数量,其产品的成品率及可靠性大幅度降低。

2、专利公开号为cn108899307a,名称为一种基板堆叠系统集成模块侧向互连结构的制备方法的专利申请,通过在电路基板上组装好裸芯片、无源元件或塑封器件后,将多块基板进行堆叠组装,采用基板功能区外侧加工的悬空互连引线作为基板信号引出线路,最后将堆叠体依次进行环氧灌封、切割、切割体表面金属化和金属化层表面激光刻线,最终在三维基板堆叠体侧面实现侧向立体互连,从而实现将多个基板和不同元件集成封装成单个三维度封装的系统集成模块电路的目的,本方法能够实现叠层层数可达到4层以上的,基板层间线间距为250μm的高密度层间布线,从而实现基于叠层基板的系统集成模块的侧向立体互连。该专利申请虽然也对互联基板进行了叠层,但不能同时兼容裸芯片叠层和互联基板叠层,仍存在存储空间小,体积大的问题。

技术实现思路

1、为了克服上述现有技术中存在的问题,本发明的目的在于提供一种存储器的多层级三维封装结构及制作方法,采用裸芯片叠层,兼容互连基板叠层封装技术,从而解决存储器模块的大容量小体积的技术问题。

2、为实现上述目的,本发明采用的技术方案是:

3、一种存储器的多层级三维封装结构,包括:

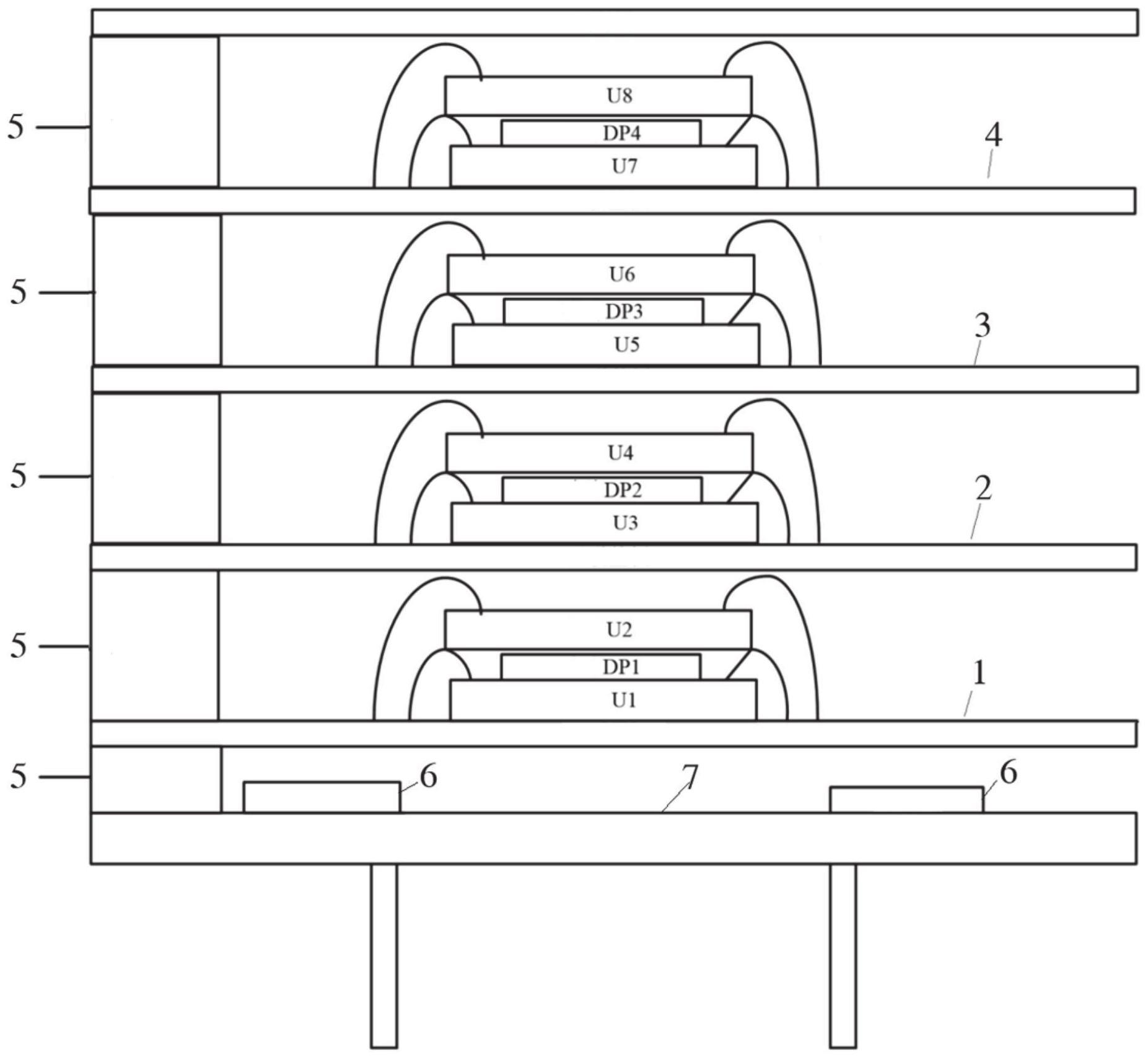

4、多个层状排列的互联基板,每两个互联基板之间通过层间垫板连接;每个互联基板上均粘接有一个底部芯片,所述底部芯片通过硅片连接有顶部芯片;每个互联基板上的底部芯片的引脚和顶部芯片的引脚均通过键合丝引至互联基板上,并从所述互联基板的两侧引出,所述互联基板两侧的引出线为飞线;多个所述互联基板之间的飞线之间通过镀层相互连接,且多个所述互联基板的飞线均连接有外引线;

5、其中,所述互联基板采用bt板;每个所述互联基板同侧的多个飞线之间均为梳齿状排布结构。

6、可选的,所述镀层为镀金层。

7、可选的,所述互联基板包括第一互联基板,所述第一互联基板上粘接有第一芯片u1,所述第一芯片u1的另一面粘接有第一硅片dp1,所述第一硅片dp1的另一面粘接有第二芯片u2,所述第一互联基板的上层通过层间垫板连接有第二互联基板,所述第二互联基板上粘接有第三芯片u3,所述第三芯片u3的另一面粘接有第二硅片dp2,所述第二硅片dp2的另一面粘接有第四芯片u2。

8、可选的,所述第二互联基板的上层通过层间垫板连接有第三互联基板,所述第三互联基板上粘接有第五芯片u5,所述第五芯片u5的另一面粘接有第三硅片dp3,所述第三硅片dp3的另一面粘接有第六芯片u6。

9、可选的,所述第三互联基板的上层通过层间垫板连接有第四互联基板,所述第四互联基板上粘接有第七芯片u7,所述第七芯片u7的另一面粘接有第四硅片dp4,所述第四硅片dp4的另一面粘接有第八芯片u8。

10、可选的,所述第四互联基板的上层通过层间垫板连接有顶挡板。

11、可选的,所述第一互联基板的下层通过层间垫板连接有底板,所述外引线设置在所述底板上。

12、所述的一种存储器的多层级三维封装结构的互联基板的飞线制作方法,包括以下步骤:

13、s1:将互联基板上需加工为飞线的区域部分加厚;

14、s2:通过酸性蚀刻液蚀在互联基板上刻出飞线需要开槽的位置;

15、s3:在开槽的位置进行定深铣;

16、s4:在开槽的位置进行激光刻蚀,得到互联基板的飞线。

17、所述的一种存储器的多层级三维封装结构的制作方法,包括以下步骤:

18、s1:堆叠互联基板,通过注胶将多个互联基板固定成一个整体;

19、s2:将多个互联基板切割成需要的尺寸;

20、s3:将切割好的多个互联基板通过镀层连接;

21、s4:制作互联基板的飞线。

22、可选的,所述的一种存储器的多层级三维封装结构的制作方法的步骤s1中,在堆叠互联基板之前,先在键合丝四周采用围堰胶制作围堰墙,再对键合丝进行滴胶保护。

23、与现有技术相比,本发明具有以下有益效果:

24、本发明的一种存储器的多层级三维封装结构,采用裸芯片叠层,兼容互连基板叠层封装技术,通过将互联基板叠层,并在互联基板上对芯片叠层,完成多个存储器裸芯片的多层级三维封装。采用bt材质的基板,能够满足多层级芯片堆叠导致的高布线密度。采用高密度悬空引线的基板能够从上下左右四个面引出线,这样不仅能够使互联基板用于存储器,还能用于任何系统的集成模块。这种裸芯片和互联基板的多层级三维封装结构,能够扩展适用范围,能够高密度布线,小体积组装微系统类产品,解决了存储器模块的大容量小体积问题,同时也解决了扩充大容量存储单元的问题。

25、本发明的存储器的多层级三维封装结构的互联基板的飞线制作方法,通过加厚飞线所在区域、定深铣以及激光刻蚀,使bt材质的基板能够被加工为梳齿装结构,避免线条过细导致的强度不足。

26、本发明的存储器的多层级三维封装结构的制作方法,由于键合丝密度高,通过围堰墙和滴胶保护键合丝,滴胶保护键合丝可以提高这种封装工艺的可靠性,并降低堆叠难度。

技术特征:

1.一种存储器的多层级三维封装结构,其特征在于,包括:

2.根据权利要求1所述的一种存储器的多层级三维封装结构,其特征在于,所述镀层为镀金层。

3.根据权利要求1所述的一种存储器的多层级三维封装结构,其特征在于,所述互联基板包括第一互联基板(1),所述第一互联基板(1)上粘接有第一芯片u1,所述第一芯片u1的另一面粘接有第一硅片dp1,所述第一硅片dp1的另一面粘接有第二芯片u2,所述第一互联基板(1)的上层通过层间垫板(5)连接有第二互联基板(2),所述第二互联基板(2)上粘接有第三芯片u3,所述第三芯片u3的另一面粘接有第二硅片dp2,所述第二硅片dp2的另一面粘接有第四芯片u2。

4.根据权利要求3所述的一种存储器的多层级三维封装结构,其特征在于,所述第二互联基板(2)的上层通过层间垫板(5)连接有第三互联基板(3),所述第三互联基板(3)上粘接有第五芯片u5,所述第五芯片u5的另一面粘接有第三硅片dp3,所述第三硅片dp3的另一面粘接有第六芯片u6。

5.根据权利要求4所述的一种存储器的多层级三维封装结构,其特征在于,所述第三互联基板(3)的上层通过层间垫板(5)连接有第四互联基板(4),所述第四互联基板(4)上粘接有第七芯片u7,所述第七芯片u7的另一面粘接有第四硅片dp4,所述第四硅片dp4的另一面粘接有第八芯片u8。

6.根据权利要求5所述的一种存储器的多层级三维封装结构,其特征在于,所述第四互联基板(4)的上层通过层间垫板(5)连接有顶挡板。

7.根据权利要求3所述的一种存储器的多层级三维封装结构,其特征在于,所述第一互联基板(1)的下层通过层间垫板(5)连接有底板(7),所述外引线(6)设置在所述底板(7)上。

8.权利要求1-7任一项所述的一种存储器的多层级三维封装结构的互联基板的飞线制作方法,其特征在于,包括以下步骤:

9.权利要求1-7任一项所述的一种存储器的多层级三维封装结构的制作方法,其特征在于,包括以下步骤:

10.根据权利要求9所述的一种存储器的多层级三维封装结构的制作方法,其特征在于,步骤s1中,在堆叠互联基板之前,先在键合丝四周采用围堰胶制作围堰墙,再对键合丝进行滴胶保护。

技术总结

本发明公开了一种存储器的多层级三维封装结构及制作方法,每两个互联基板之间通过层间垫板连接;每个互联基板上均粘接有一个底部芯片,底部芯片通过硅片连接有顶部芯片;每个互联基板上的底部芯片的引脚和顶部芯片的引脚均通过键合丝引至互联基板上,多个互联基板之间的飞线之间通过镀层相互连接,且多个互联基板的飞线均连接有外引线,互联基板采用BT板;每个互联基板同侧的多个飞线之间均为梳齿状排布结构。本发明采用裸芯片叠层,兼容互连基板叠层封装技术,通过将互联基板叠层,并在互联基板上对芯片叠层,完成多个存储器裸芯片的多层级三维封装,能够高密度布线,解决了存储器模块的大容量小体积的问题。

技术研发人员:李晗,黄桂龙,余欢,王超

受保护的技术使用者:西安微电子技术研究所

技术研发日:

技术公布日:2024/1/16

- 还没有人留言评论。精彩留言会获得点赞!