多芯片SiC功率模块动态均流的布局布线优化方法及系统

本发明属于集成电路,尤其涉及一种多芯片sic功率模块动态均流的布局布线优化方法。

背景技术:

1、随着电动汽车等电气化交通工具的广泛应用,电力电子变换器正朝着轻型化、小型化、高可靠性方向发展。目前,传统si芯片已趋近材料的理论极限,难以满足未来需求。作为宽禁带半导体的代表,sic芯片凭借其更优越的电热性能,正逐步取代si芯片。然而,目前sic芯片的制造工艺仍不成熟,限制了单个芯片的有效面积与电流容量,因此通常将多个芯片并联封装来获得大电流功率模块,以满足大功率场合的应用。多芯片sic功率模块内部不合理的布局布线设计将造成寄生参数失配现象,影响并联芯片之间的动态电流分配,而电流分配不均衡又将进一步导致功率损耗与芯片结温不一致,这意味着并联芯片的性能退化速率和热-机械应力不均衡,最终导致功率模块的可靠性和工作寿命大幅降低。因此,抑制多芯片sic功率模块的动态电流不均衡至关重要。

2、目前,针对引线键合式多芯片sic功率模块的动态均流问题,通常采用三类方法进行优化:增加功率端子数量、调整dbc基板铜图案与芯片布局、优化键合线连接点位置。其中,增加功率端子数量的方法在改善均流的同时,将加剧多电流回路之间的磁耦合,不利于发挥sic芯片高开关速度的优势。此外,现有调整dbc基板铜图案与芯片布局的方法通常采用椭圆或环形结构布局来保证每个并联芯片的功率回路对称,然而该类布局降低了基板铜面积的利用率,导致功率模块的尺寸和制造成本增加,并不实用。目前关于优化键合线连接点位置的方法通常针对芯片键合线的长度和角度进行调控,该方法可以通过相对小范围的布线调整换取相对大程度的动态电流均衡,但对于特定的功率模块未必存在最优解且尚无一套精确调控键合线长度和角度的方法。

3、通过上述分析,现有技术存在的问题及缺陷为:

4、(1)现有增加功率端子数量的方法,将加剧多电流回路之间的磁耦合,不利于发挥sic芯片高开关速度的优势。此外,当并联芯片数量较多时,功率端子数量也会相应增多,不易于功率模块的封装集成及后续并联使用。

5、(2)现有调整dbc基板铜图案与芯片布局的方法常采用椭圆或环形结构,该类布局降低了基板铜面积的利用率,增加了功率模块的尺寸与制造成本,难以实际应用。

6、(3)现有优化键合线连接点位置的方法对于特定的功率模块未必存在最优解,且尚无一套精确调控并联芯片键合线长度和角度的方法。

7、(4)现有技术通常仅针对布局或仅针对布线进行优化,仍缺少一套完整的多芯片sic功率模块布局设计与布线优化方案。

技术实现思路

1、针对现有技术在改善多芯片sic功率模块动态均流性能中存在的问题,本发明提供了一种多芯片sic功率模块动态均流的布局布线优化方法。

2、本发明是这样实现的,一种多芯片sic功率模块动态均流的布局布线优化方法,多芯片sic功率模块动态均流的布局布线优化方法包括:

3、s101,针对功率模块基板铜图案与芯片布局,提出三条设计原则与四步设计流程,在实现布局优化的同时为后续的布线优化提供条件;

4、s102,优化芯片键合线的连接点位置,对并联sic mosfet芯片功率源极键合线的长度与角度进行精确调控;

5、进一步,三条设计原则包括:

6、第一条原则:并联sic芯片在dbc基板中紧密排布,同时尽量缩短换流回路面积,减小回路寄生电感,在不影响功率模块高开关性能的前提下,实现动态均流;

7、第二条原则:降低甚至消除动态均流等式计算值edj对并联sic芯片动态均流的影响,实现dbc基板中栅极驱动回路与功率回路之间均匀耦合或是完全解耦;具体即为,各并联sic芯片的edj远小于epj,且并联芯片之间的edj差异可以忽略不计;

8、第三条原则:提高调整并联sic mosfet芯片功率源极键合线的自由度,为后续优化功率源极键合线的长度和角度提供条件;具体即为,适当扩大与功率源极键合线相连的铜图案面积,其中与上桥芯片对应的是交流输出区铜图案,与下桥芯片对应的是负母线区铜图案。

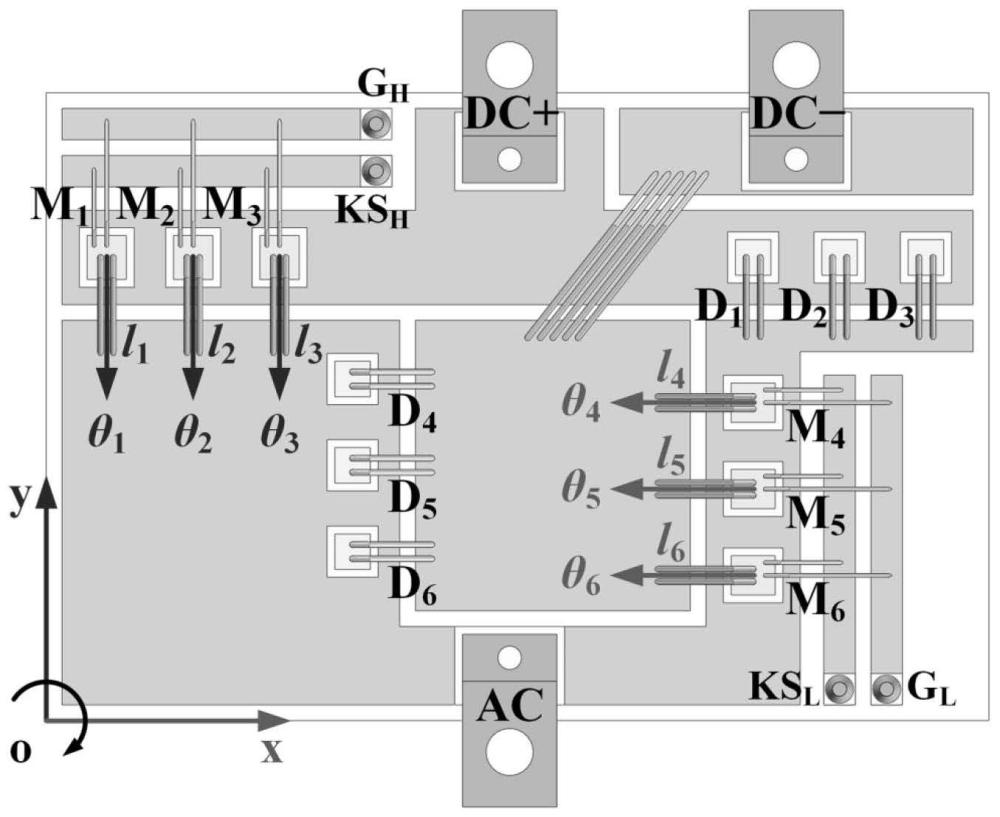

9、进一步,为满足三条设计原则,在dbc基板尺寸、功率/驱动端子尺寸、键合线直径及高度、芯片各电极的并联键合线数量及间距、并联芯片数量均不变的前提下,提出了多芯片sic功率模块基板铜图案与芯片布局设计流程如下:

10、s201:确定功率/驱动端子的数量及分布位置。对于半桥功率模块,通常选用单端结构,即正母线端子、负母线端子和交流输出端子各一个;同时,功率/驱动端子应优先分布于dbc基板的外沿位置,并且正、负母线端子之间不应相距过远,以便于功率模块并联扩容或外接去耦电容;

11、s202:确定并联sic mosfet芯片和并联sic sbd芯片的排列方式及分布位置。将多个sic mosfet芯片和多个sic sbd芯片分别以组的形式各自独立排列,同时利用p-cell和n-cell换流概念,将上桥mosfet芯片和下桥sbd芯片靠近放置,下桥mosfet芯片和上桥sbd芯片靠近放置,从而可以实现第一条设计原则,即在改善动态均流性能的同时尽可能减小回路寄生电感;

12、s203:确定并联sic mosfet芯片功率源极、栅极、开尔文源极键合线的走线方向。当栅极、开尔文源极键合线与功率源极键合线走向相同时,栅极驱动回路与功率回路之间的磁耦合较严重,导致edj较大;而当栅极、开尔文源极键合线与功率源极键合线走向相反时,edj相对较小,因此可以满足第二条设计原则;

13、s204:确定各区铜图案的分布位置及尺寸。根据功率/驱动端子的分布位置与数量来划分各区铜图案,包括正母线区dc+、负母线区dc-、交流输出区ac、上桥/下桥栅极驱动区gh/gl与开尔文源极驱动区ksh/ksl铜图案;此外,还应适当扩大与并联sic mosfet芯片功率源极键合线相连的铜图案面积,即交流输出区与负母线区铜图案的面积,以此来满足第三条设计原则。

14、进一步,调整并联芯片键合线连接点位置的具体优化流程如下:

15、s301:响应面建模与数值拟合,采用响应面建模法构建并联sic mosfet芯片功率源极键合线长度lj与角度θj这两种设计参数与动态均流等式计算值epj这一响应量之间的关系;

16、s302:功率源极键合线非线性约束优化,以布局优化后的dbc基板为研究对象,建立求取最优解时的约束条件;

17、s303:根据解得的各并联sic mosfet芯片功率源极键合线的长度lj与角度θj,对布局优化后的dbc基板进行键合线调整。

18、进一步,s301具体包括:对于每个并联芯片,采用ansys q3d仿真软件提取其部分自感值ldj,以及抽样提取其具有不同长度lj和角度θj功率源极键合线时的部分自感值lsj和部分互感值mdsj,并将这些部分电感值用于计算动态均流等式epj;然后,通过数值拟合建立每个sic mosfet芯片的响应面模型,得到功率源极键合线长度lj、角度θj与动态均流等式计算值epj之间的具体函数关系。

19、进一步,s302具体包括:并联sic mosfet芯片功率源极键合线与铜图案的连接点不可超出铜图案的范围,也不可跨越或是相交于任意芯片,且不同芯片的功率源极键合线不可相交;在此约束的基础上,对满足并联芯片epj相等的功率源极键合线长度lj和角度θj进行求解,若得到多组满足约束条件的解,则选取其中令epj最小的一组解,确保在实现动态均流的同时,最小化回路寄生电感。

20、本发明的另一目的在于提供一种应用所述的多芯片sic功率模块动态均流的布局布线优化方法的多芯片sic功率模块动态均流的布局布线优化系统,多芯片sic功率模块动态均流的布局布线优化系统包括:

21、布局设计原则开发模块,用于开发多芯片sic功率模块基板铜图案与芯片布局优化的三条设计原则;

22、dbc基板铜图案与芯片布局设计模块,用于在dbc基板尺寸、功率/驱动端子尺寸、键合线直径及高度、芯片各电极的并联键合线数量及间距、并联芯片数量均不变的前提下,根据提出的设计流程,设计多芯片sic功率模块基板铜图案与芯片布局;

23、键合线连接点位置优化模块,用于精确调整并联芯片键合线的连接点位置。

24、本发明的另一目的在于提供一种计算机设备,计算机设备包括存储器和处理器,存储器存储有计算机程序,计算机程序被处理器执行时,使得处理器执行所述的多芯片sic功率模块动态均流的布局布线优化方法的步骤。

25、本发明的另一目的在于提供一种计算机可读存储介质,存储有计算机程序,计算机程序被处理器执行时,使得处理器执行所述的多芯片sic功率模块动态均流的布局布线优化方法的步骤。

26、本发明的另一目的在于提供一种信息数据处理终端,信息数据处理终端用于实现所述的多芯片sic功率模块动态均流的布局布线优化系统。

27、结合上述的技术方案和解决的技术问题,本发明所要保护的技术方案所具备的优点及积极效果为:

28、第一,本发明提出了一套完整的多芯片sic功率模块动态均流的布局布线优化方法,其具有如下特点:

29、(1)本发明将“调整dbc基板铜图案与芯片布局”和“优化键合线连接点位置”两种方法相结合,充分利用各自的优势区间来改善动态均流性能,扩大了对任意多芯片sic功率模块的普适性。

30、(2)本发明提出了基板铜图案与芯片布局优化的设计原则与流程,根据设计流程,可以得到具有寄生电感小、栅极驱动回路与功率回路基本解耦等优点的功率模块布局,显著提高后续布线优化的自由度。

31、(3)本发明提出了一种调整并联芯片键合线连接点位置的方案,该方案结合响应面建模法和动态均流等式,精确调控sic mosfet芯片功率源极键合线的长度与角度,提高了布线优化的精度。

32、(4)本发明所提出的布局布线优化方法是一套完整的改善多芯片sic功率模块动态均流性能的方案,涵盖了从基板布局到键合线布线整个设计流程。

33、第二,本发明提出的多芯片sic功率模块动态均流的布局布线优化方法首先针对dbc基板铜图案与芯片布局进行优化,通过提出的三条设计原则与四步设计流程可以得到具有寄生电感小、栅极驱动回路与功率回路基本解耦等优点的功率模块布局。然后,以该布局为研究对象,建立响应面模型坐标系和非线性约束条件,精确调控并联sic mosfet芯片功率源极键合线的长度与角度,完成布线优化。仿真与实验结果均表明,经过初步的dbc基板铜图案与芯片布局优化后,并联芯片间仍存在较明显的动态电流不均衡现象,而经过进一步的布线调整后,则可以实现良好的动态均流性能。

34、第三,本发明的技术方案是否解决了人们一直渴望解决、但始终未能获得成功的技术难题:

35、本发明提出了一套完整的多芯片sic功率模块动态均流的布局布线优化方法,该方法结合了“调整dbc基板铜图案与芯片布局”和“优化键合线连接点位置”两种方案,并充分利用各自的优势区间来改善动态均流性能。针对dbc基板铜图案与芯片布局优化,提出了三条设计原则与四步设计流程,在完成布局设计的同时为后续的布线优化提供条件。针对布线优化,建立响应面模型与非线性约束条件,精确调控并联sic mosfet芯片功率源极键合线的长度与角度。这一整套动态均流优化方案可以适用于任意并联芯片数量的sic功率模块。

36、第四,以下是每个步骤具体取得的显著技术进步的说明:

37、第一条原则:并联sic芯片在dbc基板中紧密排布,同时尽量缩短换流回路面积,减小回路寄生电感,在不影响功率模块高开关性能的前提下,实现动态均流:

38、1.紧密排布芯片:通过紧密排布并联sic芯片,可以减小芯片之间的寄生电阻和寄生电感差异,改善功率模块的动态均流性能。

39、2.缩短换流回路面积:通过缩短换流回路面积,减小回路寄生电感,抑制功率模块的开关过冲和电磁干扰,提高可靠性。

40、第二条原则:降低甚至消除动态均流等式计算值edj对并联sic芯片动态均流的影响,实现dbc基板中栅极驱动回路与功率回路之间均匀耦合或是完全解耦;具体即为,各并联sic芯片的edj远小于epj,且并联芯片之间的edj差异可以忽略不计:

41、1.栅极驱动回路与功率回路解耦:对并联sic mosfet芯片功率源极、栅极、开尔文源极键合线进行相反方向布线,降低并联芯片的edj值,实现栅极驱动回路与功率回路的均匀耦合或完全解耦。

42、第三条原则:提高调整并联sic mosfet芯片功率源极键合线的自由度,为后续优化功率源极键合线的长度和角度提供条件;具体即为,适当扩大与功率源极键合线相连的铜图案面积,其中与上桥芯片对应的是交流输出区铜图案,与下桥芯片对应的是负母线区铜图案。

43、1.扩大铜图案面积:通过扩大与功率源极键合线相连的交流输出区和负母线区的铜图案面积,提高调整芯片键合线长度和角度的自由度,优化布线设计。

44、以上技术进步是根据问题描述进行推断和解释的,实际的技术进步可能会因具体实施方案和设计细节的不同而有所变化。

- 还没有人留言评论。精彩留言会获得点赞!