封装结构及封装方法与流程

本发明涉及半导体集成电路领域,尤其涉及一种封装结构及封装方法。

背景技术:

1、芯片封装是电子芯片制造中的一个重要领域,它涉及将电子器件(如集成电路、晶体管、传感器等)封装在封装材料中,封装技术的主要目标和功能包括:第一,保护元器件,以防止物理损伤、干燥、湿气和其他环境因素对元器件的影响,延长元器件的使用寿命和可靠性。第二,电气连接,封装提供了连接电子元件与外部电路的方式,通常通过引脚、焊接或其他电连接方法来实现。第三,机械支持,确保pcb在安装和使用过程中保持正确的位置和结构。第四,散热,有助于将产生的热量传递到周围环境中,以防止散热过热。

2、为了提高封装结构中的半导体组件的容量,减小封装结构的面积,通常做法是将多个芯片堆叠放置在一起,以在有限的空间内提高性能、功效和功能。通常多个芯片通过daf等胶膜叠加在一起,并通过引线将芯片单元与外部电路相连接。

3、堆叠芯片中,为了方便芯片与封装基板之间通过引线连接,多个芯片通常呈阶梯式堆叠设置,但这种形式的封装结构有待改进改进。

技术实现思路

1、本发明解决的问题是提供一种封装结构及封装方法,以提高封装结构的性能。

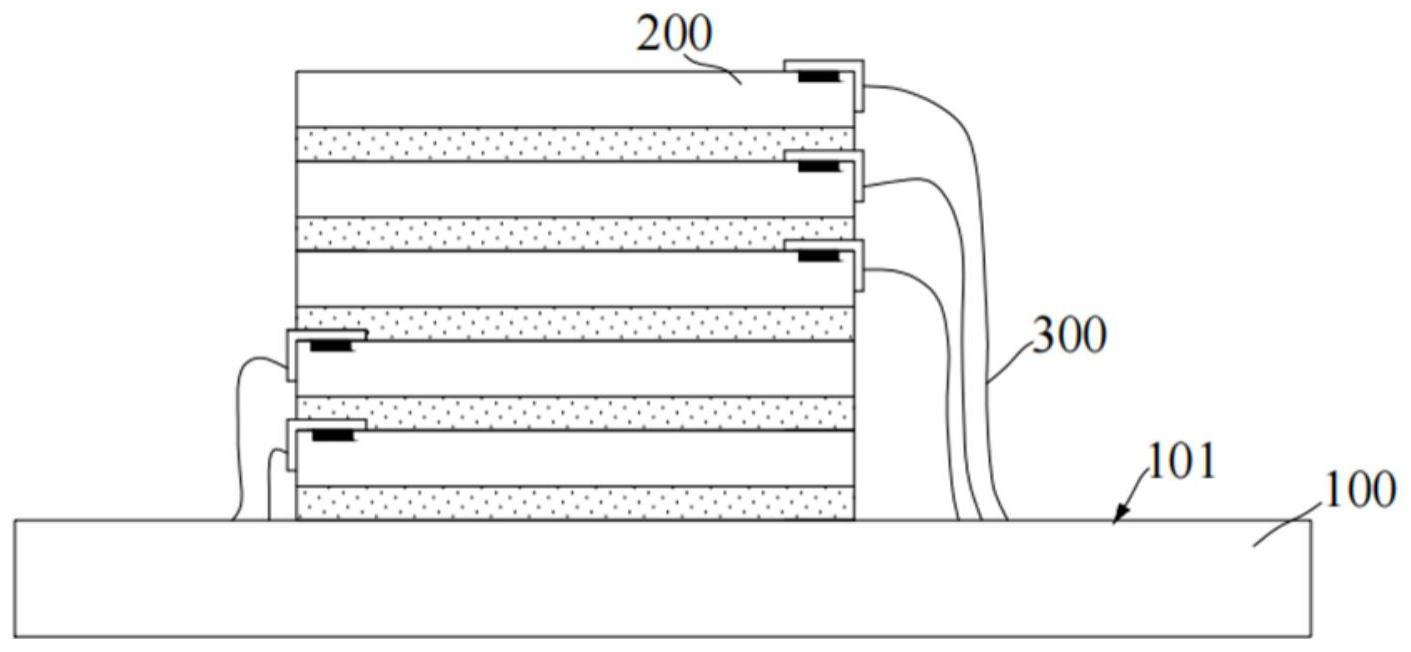

2、为解决上述问题,本发明提供了一种封装结构,包括:封装基板;多个芯片结构堆叠设置在所述封装基板上,所述芯片结构包括:芯片,所述芯片背离所述封装基板的一侧具有电连接端;电连接结构,贴附在所述电连接端和所述芯片侧壁上,用于将所述电连接端引接至所述芯片侧壁;引线,将所述封装基板和芯片侧壁的所述电连接结构连接。

3、可选的,多个所述芯片结构的一个或多个侧壁在垂直封装基板的方向上相齐平。

4、可选的,所述电连接结构包括:第一连接部,位于所述芯片背离所述封装基板的一侧,且与所述电连接端连接;第二连接部,与所述第一连接部连接,且位于所述芯片侧壁。

5、可选的,所述电连接结构暴露的面积为1600um2至40000um2。

6、可选的,所述第一连接部所在平面和第二连接部所在平面相垂直。

7、可选的,所述第一连接部和第二连接部相连处为连接线,沿垂直所述连接线方向,所述电连接结构的剖面呈l型。

8、可选的,所述封装结构还包括:导电胶,位于所述第一连接部和所述电连接端之间,用于将所述电连接结构和电连接端连接。

9、可选的,所述导电胶的材料包括:导电颗粒或导电填料,所述导电颗粒或导电填料包括银导电胶、铜导电胶、铜氧化物导电胶或碳纳米管导电胶;基胶或粘合剂,所述基胶或粘合剂包括环氧树脂、丙烯酸酯或硅基材料。

10、可选的,不同所述芯片结构中的所述电连接端位于堆叠设置的多个所述芯片结构的同一侧;所述电连接结构和引线位于堆叠设置的多个所述芯片结构的同一侧。

11、可选的,所述电连接结构的材料包括:金、银和铜中的一种或多种。

12、可选的,所述电连接结构的厚度小于80um。

13、可选的,所述芯片结构形成有所述电连接端的面为芯片结构正面,芯片结构中与芯片结构正面相背的面为芯片结构背面;所述芯片结构还包括:胶膜,位于所述芯片结构背面;所述芯片结构通过所述胶膜贴附在所述封装基板上,或者贴附在其他芯片结构的所述芯片结构正面。

14、相应地,本发明实施例还提供了一种封装方法,包括:提供封装基板;在所述封装基板上进行多次的芯片结构形成步骤,且使多个芯片结构堆叠设置,所述芯片结构形成步骤包括:提供芯片,所述芯片背离所述封装基板的一侧具有电连接端;在所述电连接端和所述芯片侧壁贴附电连接结构,所述电连接结构用于将所述电连接端引接至所述芯片侧壁;形成多个芯片结构后,形成连接所述封装基板和芯片结构侧壁上的所述电连接结构的引线。

15、可选的,在所述封装基板上进行多次的芯片结构形成步骤中,多个所述芯片结构的一个或多个侧壁在垂直封装基板的方向上相齐平。

16、可选的,所述电连接结构包括第一连接部和第二连接部;在所述电连接端上贴附电连接结构的步骤包括:将所述第一连接部贴附在芯片背离所述封装基板的一侧,且与所述电连接端连接;将所述第二连接部贴附在所述芯片侧壁。

17、可选的,在所述电连接端上贴附电连接结构的步骤中,所述第一连接部通过导电胶与所述电连接端连接。

18、可选的,所述导电胶的材料包括:导电颗粒或导电填料,所述导电颗粒或导电填料包括银导电胶、铜导电胶、铜氧化物导电胶或碳纳米管导电胶;基胶或粘合剂,所述基胶或粘合剂包括环氧树脂、丙烯酸酯或硅基材料。

19、可选的,在所述封装基板上进行多次的芯片结构形成步骤的步骤中,不同所述芯片结构中的所述电连接端位于堆叠设置的多个所述芯片结构的同一侧,所述电连接结构位于堆叠设置的多个所述芯片结构的同一侧;形成引线的步骤中,所述引线位于堆叠设置的多个所述芯片结构的同一侧。

20、可选的,提供芯片的步骤中,所述芯片背离所述电连接端的一侧形成有胶膜;在所述封装基板上进行多次的芯片结构形成步骤中,最靠近所述封装基板的芯片结构通过所述胶膜贴附在所述封装基板上;在所述封装基板上进行多次的芯片结构形成步骤中,远离所述封装基板的芯片结构通过胶膜贴附在靠近所述封装基板的芯片结构上。

21、与现有技术相比,本发明的技术方案具有以下优点:

22、本发明实施例提供的所述封装结构中的多个芯片结构堆叠设置在封装基板上,芯片结构中的芯片背离所述封装基板的一侧具有电连接端,电连接结构贴附在所述电连接端和所述芯片侧壁上,用于将所述电连接端引接至所述芯片侧壁,所述电连接结构与电连接端相比具有更大的面积,且电连接结构位于所述芯片侧壁的部分增加了散热途径,因此封装结构具有良好散热能力。

23、可选方案中,多个所述芯片结构的一个或多个侧壁在垂直封装基板的方向上相齐平。本发明实施例中的引线与芯片侧壁的所述电连接结构连接,使得多个芯片结构在堆叠设置的情况下,多个所述芯片结构的一个或多个侧壁在垂直封装基板的方向上能够处于相齐平的状态,缩小了封装结构在垂直于所述芯片侧壁方向的尺寸,引线与芯片结构侧壁上的电连接结构连接,引线不位于堆叠设置的芯片结构的顶部,引线采用这种结构也可以减小封装结构的高度。此外,与多个堆叠的芯片结构侧壁不齐平时,芯片结构的电连接端下方没有支撑,且电连接端的引线的键合方向垂直于芯片结构表面的情况相比,本发明实施例在形成引线的过程中,引线的作用力垂直于芯片侧壁方向,形成引线的过程中芯片结构不容易出现震颤,降低芯片结构受损的概率,有利于提高封装结构的可靠性。

24、本发明实施例提供的封装方法中,在所述封装基板上进行多次的芯片结构形成步骤,芯片结构中的芯片背离所述封装基板的一侧具有电连接端,电连接结构贴附在所述电连接端和所述芯片侧壁上,用于将所述电连接端引接至所述芯片侧壁,所述电连接结构与电连接端相比具有更大的面积,且电连接结构位于所述芯片侧壁的部分增加了散热途径,因此封装结构具有良好散热能力。

25、可选方案中,在所述封装基板上进行多次的芯片结构形成步骤中,多个所述芯片结构的一个或多个侧壁在垂直封装基板的方向上相齐平。使得形成引线的过程中,引线能够与芯片侧壁上的电连接结构连接,有利于使多个芯片结构在堆叠设置的情况下,多个所述芯片结构的侧壁在垂直封装基板的方向上能够处于齐平状态,缩小了封装结构在垂直于所述芯片侧壁方向的尺寸,引线与芯片结构侧壁上的电连接结构连接,引线不形成在堆叠设置的芯片结构的顶部,采用这种打线方式也可以减小封装结构的高度。此外,与多个堆叠的芯片结构侧壁不齐平时,芯片结构的电连接端下方没有支撑,且电连接端的引线的键合方向垂直于芯片结构表面的情况相比,本发明实施例在形成引线的过程中,引线的作用力垂直于芯片侧壁方向,形成引线的过程中芯片结构不容易出现震颤,降低芯片结构受损的概率,有利于提高封装结构的可靠性。

- 还没有人留言评论。精彩留言会获得点赞!