一种沟槽型碳化硅MOSFET及其制作工艺的制作方法

本发明涉及半导体器件,更具体地说,本发明涉及一种沟槽型碳化硅mosfet及其制作工艺。

背景技术:

1、沟槽型mosfet作为一种垂直结构器件,拥有开关速度快、频率性能好、输入阻抗高、驱动功率小、温度特性好、无二次击穿问题等优点,已经在稳压器、电源管理模块、机电控制、显示控制、汽车电子等领域得到了广泛的应用。mosfet的源极和漏极之间存在电路通道,随着漏极端子的电压的增加, mosfet的漏极和基板的耗尽区会因为反向偏置而增加,从而导致电路通道宽度减小,限制电荷流动,进而导致电流减小,直至达到饱和电流,通常我们采用调整阈值电压的方式,增加电路通道的宽度,进而调整通过电路通道的饱和电流大小。但是这样需要栅极端子的电源可控才行,如何在不调整阈值电压的情况下获得更大的饱和电流,并且生产能满足该条件的mosfet是本发明要解决的技术问题。因此,有必要提出一种沟槽型碳化硅mosfet及其制作工艺,以至少部分地解决现有技术中存在的问题。

技术实现思路

1、在

技术实现要素:

部分中引入了一系列简化形式的概念,这将在具体实施方式部分中进一步详细说明。本发明的发明内容部分并不意味着要试图限定出所要求保护的技术方案的关键特征和必要技术特征,更不意味着试图确定所要求保护的技术方案的保护范围。

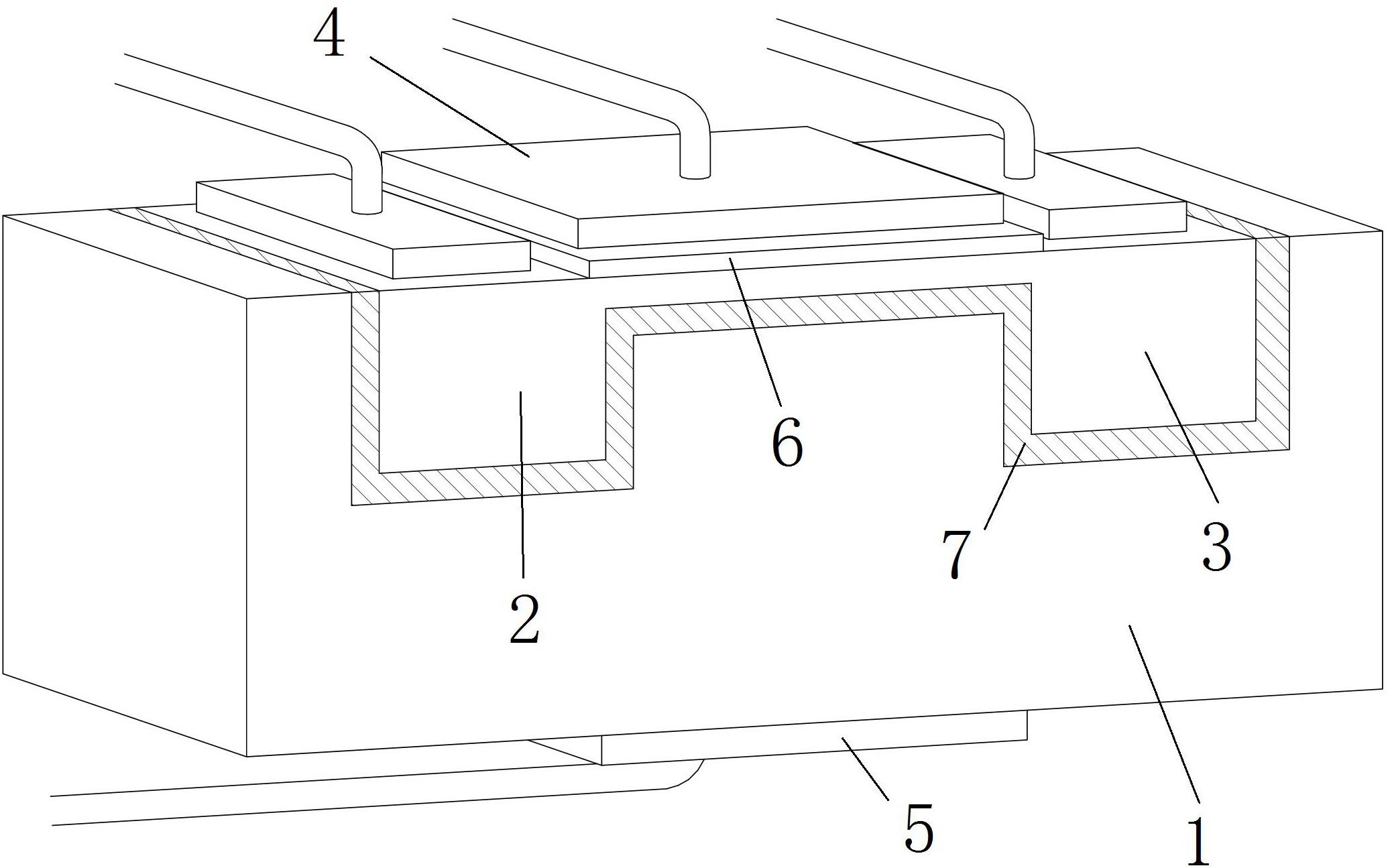

2、为至少部分地解决上述问题,本发明提供了一种沟槽型碳化硅mosfet,包括:基板,所述基板的顶部设置有用于安装源极端子的源极沟槽,和用于安装漏极端子的漏极沟槽,所述源极端子的顶部通过栅极端子与所述漏极端子的顶部,所述基板的底部设置有主体端子,

3、当mosfet为耗尽型时,所述基板的顶部还设置有填充导电介质的导电沟,所述源极沟槽和所述漏极沟槽通过所述导电沟连通,所述栅极端子与所述源极端子、所述漏极端子均与所述导电沟连接;

4、当mosfet为增强型时,所述源极沟槽和所述漏极沟槽之间被所述基板隔开,所述源极端子通过所述栅极端子与所述漏极端子连接;

5、所述源极沟槽和所述漏极沟槽上均设置有外延区域。

6、优选的是,所述源极沟槽为竖直槽,所述源极沟槽靠近所述漏极沟槽的侧壁上设置有外延区域,所述外延区域由所述源极沟槽向所述漏极沟槽方向延伸。

7、优选的是,所述漏极沟槽为竖直槽,所述漏极沟槽靠近所述源极沟槽的侧壁上设置有外延区域,所述外延区域由所述漏极沟槽向所述源极沟槽方向延伸。

8、优选的是,所述源极端子和所述漏极端子之间设置有介电层,所述栅极端子设置在所述介电层的上方。

9、一种沟槽型碳化硅mosfet的制作工艺,步骤如下:

10、s1:通过湿法刻蚀设备,对涂胶后的基板进行刻蚀,形成源极沟槽和漏极沟槽;

11、s2:将湿法刻蚀后的基板放在干法刻蚀设备内,并通过夹持在基板上的定位组件与干法刻蚀设备内的固定组件连接、定位;

12、s3:通过干法刻蚀设备对源极沟槽和漏极沟槽进行再加工,形成带有外延区域的源极沟槽和带有外延区域的漏极沟槽;

13、s4:向源极沟槽和漏极沟槽内注入离子、沉积源极端子和漏极端子。

14、优选的是,步骤s1中,通过湿法刻蚀设备制作的源极沟槽和漏极沟槽为v形槽。

15、优选的是,步骤s2中,夹持在基板上的定位组件由固定板和设置在固定板上的定位矩阵组成,固定板的一面与基板进行夹持、固定,另一面通过所述定位矩阵与干法刻蚀设备上的固定组件连接、定位,所述定位矩阵由若干个四棱锥组成。

16、优选的是,干法刻蚀设备内的所述固定组件由定位层和固定层组成,所述定位层设置在所述固定层的上方,所述定位层的顶面设置有与所述定位矩阵相适应的定位槽矩阵,所述定位槽矩阵由若干个贯穿所述定位层,并延伸至所述固定层内的定位槽组成,所述定位槽的形状与所述定位矩阵上的四棱锥的形状相适应,所述定位层和所述固定层之间设置有定位通道,所述定位槽矩阵内的定位槽均通过所述定位通道连通;

17、所述定位通道内填充有弹性体,

18、或所述定位通道延伸至所述定位层的侧壁,并与抽真空设备连接。

19、优选的是,步骤s3中,干法刻蚀设备对源极沟槽和漏极沟槽进行偏心刻蚀,未被干法刻蚀到的v型部位形成外延区域。

20、优选的是,步骤s4中,向源极沟槽和漏极沟槽内注入离子,定义源、漏区,然后沉积源极金属、漏极金属和栅极端子。

21、相比现有技术,本发明至少包括以下有益效果:

22、本发明由基板、设置在源极沟槽内的源极端子、设置在漏极沟槽内的漏极端子、连接在基板上的主体端子、连接在源极端子和漏极端子之间的介电层,以及连接在介电层上方的栅极端子组成。需要注意的是,源极端子和漏极端子在结构上相同,因此无需特意区分源极端子和漏极端子,即,一个作为源极端子使用,另一个自然而然就作为漏极端子使用。以增强型n通道为例,即源极端子和漏极端子采用n型半导体,基板采用p型半导体。源极端子和主体端子电连接,电源可以连接在漏极端子(与正极连接)和源极端子(与负极连接)之间,此时漏极端子和源极端子之间的电压为vd,因为电源增加了漏极端子的电势,所以会导致漏极端子与基板之间的耗尽区增加,因此电流不会从漏极端子进入到源极端子内,从而使mosfet处于断开状态(常闭),为了能够使电流从漏极端子到达源极端子,就需要再建立一个通道,我们在栅极端子和源极端子之间加设一个电源,正极与栅极端子连接,负极与源极端子连接,此时栅极端子和源极端子之间的电压为vg,因为存在介电层,所以电子无法从基板流向栅极端子,介电层除了可以阻挡电子,还可以增加电子上的电荷(类似于电容器),从而吸引更多电子,因为栅极端子处的基板聚集了大量的自由电子,从而使栅极端子附近的基板变为负或n型半导体,进而在基板内形成将源极端子和漏极端子连接的电路通道(类似于导电沟),以便电流可以从漏极端子流向源端子形成通路,即,开关打开。我们可以通过改变vg来调整栅极端子的电压,从而改变电路通道的厚度,能够形成电路通道的电压,我们称之为阈值电压,当电路通路连通时,mosfet处于欧姆或线性区域,在该区域内,遵循欧姆定律。

23、此时会出现一个问题,即随着电压的增加,漏极端子和基板(电路通道部分)的耗尽区会随着反向偏置而增加,如图3所示,并且电路通道内的耗尽区会由漏极端子向源极端子方向增加,从而减小了通道的宽度,限制电荷流动,导致电流减小(耗尽型通过导电沟改变电流大小的原理相同,只不过耗尽型需要负栅极电压,来实现断路),当电压增加的时候,电路通道会被耗尽区完全封堵,我们称为夹断效应,不过实际应用的时候,电路通道并不会完全封闭,而是会形成恒定的饱和电流,产生饱和电流的电压为饱和电压。为了增加饱和电流的大小,一般采用加大栅极端子的阈值电压,来增加电路通道的宽度,进而增加饱和电流的大小。因为该方法需要改变vg,所以我们提出一种在相同vg下改变饱和电流的实施方式,即,我们在源极沟槽和漏极沟槽上加设了外延区域,如图4所示,通过增加外延区域,缩短漏极沟槽和漏极沟槽在端面上的距离,进而缩短电路通道的长度,在vg相同的情况下,当达到饱和电流的时候,电路通道的最小厚度dh大于常规加工方式加工的mosfet的电路通道的最小厚度dc,如图5所示。从而实现在不改变vg的情况下,能够使生产的mosfet可以通过更大的饱和电流。

24、本发明所述的沟槽型碳化硅mosfet及其制作工艺,本发明的其它优点、目标和特征将部分通过下面的说明体现,部分还将通过对本发明的研究和实践而为本领域的技术人员所理解。

- 还没有人留言评论。精彩留言会获得点赞!