半导体装置的制作方法

本发明涉及半导体器件,尤其是涉及一种半导体装置。

背景技术:

1、rc-igbt(逆导型绝缘栅型双极晶体管reverse conducting-insulated gatebipolar transistor)将igbt(绝缘栅型双极晶体管insulated gate bipolartransistor)和frd(快恢复二极管fast recovery diode)集成到同一颗芯片上,使其同时具有正向导通和逆向导通的特性,具有尺寸小、功率密度高、成本低、可靠性高等诸多优点。

2、在相关技术中,多将igbt和frd集成在器件的元胞区,两个器件共用终端,从而实现集成的目的。但是,由于igbt和frd共用器件的元胞区,该方法中存在的缺点是牺牲了一部分igbt的元胞区,在器件设计的时候,为了达到igbt器件的理论性能,不得不增加器件元胞区域的面积,这样会导致rc-igbt的整体面积增大,散热性能降低,并且成本增加。

技术实现思路

1、本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明的一个目的在于提出一种半导体装置,该半导体装置可以有效利用假栅区域的面积,性能更佳,成本更低。

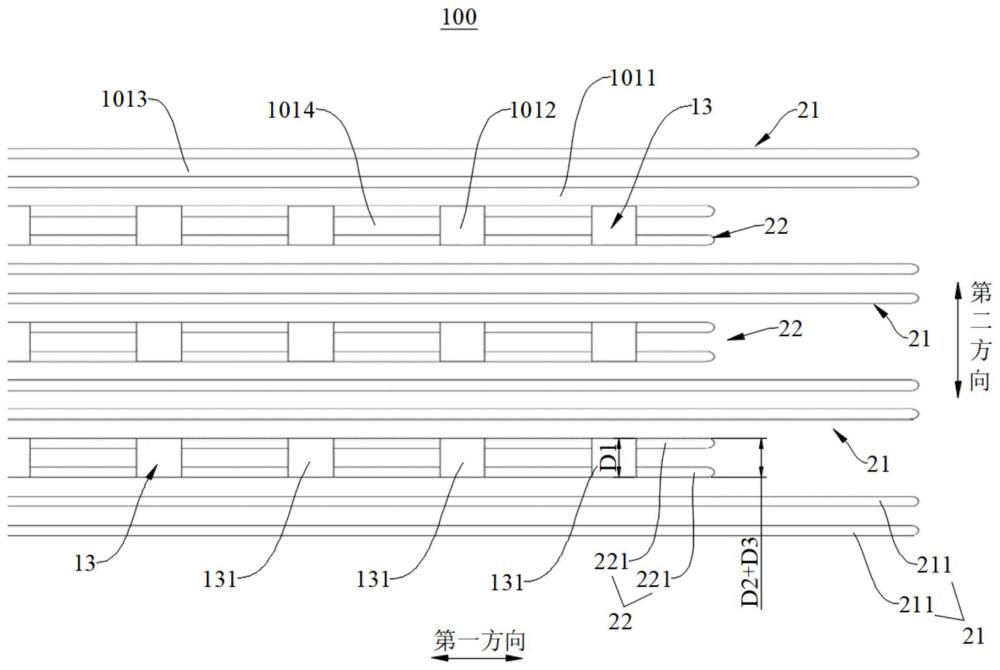

2、根据本发明实施例的半导体装置,包括:第一导电类型的漂移层;沟槽部,所述沟槽部从所述漂移层的上表面向下延伸,所述沟槽部在第一方向上延伸设置且为多个,多个所述沟槽部在第二方向上间隔设置且形成栅极沟槽组和假栅沟槽组,所述栅极沟槽组和所述假栅沟槽组在第二方向上交替设置;第一导电类型的场截止层,所述场截止层设置于所述漂移层的下表面;第二导电类型的集电极层,所述集电极层设置于所述场截止层的下表面,所述集电极层内设置有第一导电类型的第一发射极层,所述第一发射极层与所述假栅沟槽组上下对应。

3、由此,通过使第一发射极层与假栅沟槽组上下对应,这样可以充分利用假栅区域,无需单独设置第二半导体器件类型区域,从而在保证半导体装置同时具有正向导通和逆向导通的特性,以及保证半导体装置的短路能力的前提下,使假栅区域也可以作为第二半导体器件类型区域使用,减小半导体装置的面积,提高半导体装置的工作性能,降低半导体装置的生产成本。

4、在本发明的一些示例中,所述第一发射极层在第一方向上延伸设置。

5、在本发明的一些示例中,所述第一发射极层包括多个子发射极部,多个所述子发射极部在第一方向上间隔设置。

6、在本发明的一些示例中,所述第一发射极层为多个,所述假栅沟槽组为多个,多个所述第一发射极层与多个所述假栅沟槽组一一对应设置。

7、在本发明的一些示例中,所述假栅沟槽组在所述漂移层下表面的投影覆盖所述第一发射极层在所述漂移层下表面的投影。

8、在本发明的一些示例中,所述第一发射极层第一方向上的长度小于所述假栅沟槽组第一方向上的长度。

9、在本发明的一些示例中,所述第一发射极层第二方向上的宽度与所述假栅沟槽组第二方向上的宽度相等。

10、在本发明的一些示例中,所述第一发射极层第二方向上的宽度小于所述假栅沟槽组第二方向上的宽度。

11、在本发明的一些示例中,所述假栅沟槽组包括一个假栅沟槽部,所述第一发射极层第二方向上的宽度小于一个所述假栅沟槽部第二方向的宽度;或所述第一发射极层第二方向上的宽度等于一个所述假栅沟槽部第二方向的宽度。

12、在本发明的一些示例中,所述假栅沟槽组包括至少两个第二方向间隔设置的假栅沟槽部,所述第一发射极层第二方向上的宽度为d1,至少两个所述假栅沟槽部第二方向上的宽度之和为d2,至少两个所述假栅沟槽部第二方向的间隔距离之和为d3,d1、d2和d3满足关系式:d1≤d2+d3。

13、本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

技术特征:

1.一种半导体装置,其特征在于,包括:

2.根据权利要求1所述的半导体装置,其特征在于,所述第一发射极层(13)在第一方向上延伸设置。

3.根据权利要求1所述的半导体装置,其特征在于,所述第一发射极层(13)包括多个子发射极部(131),多个所述子发射极部(131)在第一方向上间隔设置。

4.根据权利要求1所述的半导体装置,其特征在于,所述第一发射极层(13)为多个,所述假栅沟槽组(22)为多个,多个所述第一发射极层(13)与多个所述假栅沟槽组(22)一一对应设置。

5.根据权利要求1所述的半导体装置,其特征在于,所述假栅沟槽组(22)在所述漂移层(10)下表面的投影覆盖所述第一发射极层(13)在所述漂移层(10)下表面的投影。

6.根据权利要求5所述的半导体装置,其特征在于,所述第一发射极层(13)第一方向上的长度小于所述假栅沟槽组(22)第一方向上的长度。

7.根据权利要求5所述的半导体装置,其特征在于,所述第一发射极层(13)第二方向上的宽度与所述假栅沟槽组(22)第二方向上的宽度相等。

8.根据权利要求5所述的半导体装置,其特征在于,所述第一发射极层(13)第二方向上的宽度小于所述假栅沟槽组(22)第二方向上的宽度。

9.根据权利要求5所述的半导体装置,其特征在于,所述假栅沟槽组(22)包括一个假栅沟槽部(221),所述第一发射极层(13)第二方向上的宽度小于一个所述假栅沟槽部(221)第二方向的宽度;或所述第一发射极层(13)第二方向上的宽度等于一个所述假栅沟槽部(221)第二方向的宽度。

10.根据权利要求5所述的半导体装置,其特征在于,所述假栅沟槽组(22)包括至少两个第二方向间隔设置的假栅沟槽部(221),所述第一发射极层(13)第二方向上的宽度为d1,至少两个所述假栅沟槽部(221)第二方向上的宽度之和为d2,至少两个所述假栅沟槽部(221)第二方向的间隔距离之和为d3,d1、d2和d3满足关系式:d1≤d2+d3。

技术总结

本发明公开了一种半导体装置,半导体装置包括:第一导电类型的漂移层;沟槽部,多个沟槽部在第二方向上间隔设置且形成栅极沟槽组和假栅沟槽组,栅极沟槽组和假栅沟槽组在第二方向上交替设置;第一导电类型的场截止层;第二导电类型的集电极层,集电极层设置于场截止层的下表面,集电极层内设置有第一导电类型的第一发射极层,第一发射极层与假栅沟槽组上下对应。由此,通过使第一发射极层与假栅沟槽组上下对应,这样可以充分利用假栅区域,无需单独设置第二半导体器件类型区域,使假栅区域也可以作为第二半导体器件类型区域使用,减小半导体装置的面积,提高半导体装置的工作性能,降低半导体装置的生产成本。

技术研发人员:刘恒,陈道坤,周文杰,张永旺,储金星,杨晶杰,刘子俭

受保护的技术使用者:海信家电集团股份有限公司

技术研发日:

技术公布日:2024/3/5

- 还没有人留言评论。精彩留言会获得点赞!