一种沟槽型MOSFET及其制造方法与流程

本技术涉及半导体,尤其涉及一种沟槽型mosfet及其制造方法。

背景技术:

1、随着集成电路的特征尺寸(即最小尺寸)缩小到22nm,短沟道效应愈发严重,仅依靠提高沟道的掺杂浓度、降低源漏结深和缩小栅氧层厚度等技术来改善传统平面型晶体管结构的短沟道效应遇到了瓶颈。高掺杂的沟道会导致器件阈值电压的大幅增加、增大库伦散射,使载流子迁徙率下降,最终导致器件的速度进一步降低。缩减栅氧层厚度到一定范围后,它便不再是理想的绝缘体,栅极与衬底之间的电子将出现量子化现象,载流子以波的形式绕过栅氧层的势垒形成量子隧穿效应,形成隧穿电流,并在栅极与衬底之间形成漏电流。

2、鳍式场效应晶体管(fin field-effect transistor,finfet)是直接把金属-氧化物-半导体型场效应管(metal-oxide-semiconductor field-effect-transistor,mosfet)中距离栅极一定范围的沟道提取出来,形成凸起的高而薄的鳍,栅极则是三面包裹着沟道。finfet晶体管凸起的沟道区域是一个被三面栅极包裹的鳍状半导体。栅极三面包裹沟道的结构增大了栅与沟道的面积,增强了栅对沟道的控制能力,同时栅极到内部鳍的距离缩小了,从而使栅极可以有效地控制沟道,降低器件关闭时的漏电流,抑制短沟道效应。

3、但是finfet晶体管工艺要求高,难以形成fin形状,并且对于设备精密程度要求也十分严苛,制造成本高昂。

技术实现思路

1、本技术提供了一种沟槽型mosfet及其制造方法,以至少解决现有技术中存在的以上技术问题。

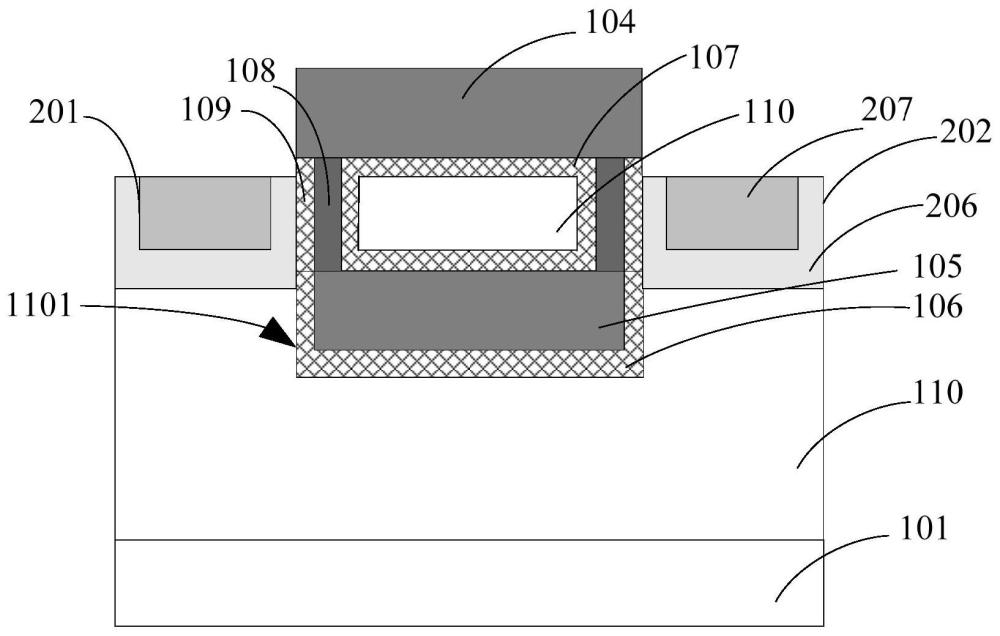

2、根据本技术的第一方面,提供了一种沟槽型mosfet,包括:

3、衬底;

4、外延层,位于所述衬底上表面,所述外延层中具有腔体;

5、栅极导体,所述栅极导体包括上栅极导体及下栅极导体;

6、所述腔体内具有第一介质层及所述下栅极导体,所述腔体内表面覆盖有第一介质层,以将所述下栅极导体与所述外延层隔离;

7、所述上栅极导体位于所述外延层的上表面,所述上栅极导体与所述外延层间设置有第二介质层;

8、栅极连接柱,所述栅极连接柱位于所述上栅极导体与所述下栅极导体间的所述外延层内,所述栅极连接柱穿过所述外延层分别与所述上栅极导体和所述下栅极导体相连,所述栅极连接柱外周向覆盖有第三介质层,以将所述栅极连接柱与所述外延层隔离;

9、源极、漏极,所述源极和漏极分别位于所述栅极导体两侧,并分别与所述上栅极导体与所述下栅极导体相接。

10、在一可实施方式中,所述下栅极导体的上表面不低于所述源极和所述漏极的下表面。

11、在一可实施方式中,所述栅极连接柱设置有两个,两个所述栅极连接柱分别设置在所述外延层的对角处。

12、在一可实施方式中,所述第一介质层、第二介质层、第三介质层的厚度为65埃~75埃。

13、根据本技术的第二方面,提供了一种沟槽型mosfet的制造方法,所述方法包括:

14、形成在衬底上的第一外延层;

15、形成从所述第一外延层上表面延伸至其内部的第一沟槽;

16、形成位于所述第一沟槽内的下栅极导体及第一介质层,所述下栅极导体外覆盖有所述第一介质层,以将所述下栅极导体与所述第一外延层隔离;

17、形成位于所述第一沟槽内的第二外延层,所述第二外延层位于所述第一介质层的上部;

18、形成位于所述第二外延层内的栅极连接柱,所述栅极连接柱的一端与所述下栅极导体相连,所述栅极连接柱外周向覆盖有第三介质层,以将所述栅极连接柱与所述第二外延层隔离;

19、形成位于所述第二外延层上表面的第二介质层及上栅极导体,所述第二介质层将所述上栅极导体与所述第二外延层隔离,所述上栅极导体与所述下栅极导体将所述第二外延层及所述第二介质层夹持在内,所述栅极连接柱向上延伸并与所述上栅极导体相连;

20、形成位于所述上栅极导体与所述下栅极导体两侧的源极与漏极,所述源极与所述漏极均与所述上栅极导体及所述下栅极导体相接。

21、在一可实施方式中,所述形成位于所述第一沟槽内的下栅极导体及第一介质层,包括:

22、形成位于所述第一沟槽内表面的第四介质层,所述第四介质层围绕所述第一沟槽形成第二沟槽;

23、形成位于所述第二沟槽的下栅极导体;

24、形成位于所述第二沟槽内的第五介质层;

25、由所述第一外延层上表面向下去除部分第四介质层及第五介质层,并保留位于所述下栅极导体上表面的第五介质层及位于所述下栅极导体周向和下表面的第四介质层,所述第四介质层和所述第五介质层组合形成所述第一介质层,以将所述下栅极导体与所述第一外延层隔离。

26、在一可实施方式中,所述形成位于所述第一沟槽内的第二外延层,包括:

27、形成位于所述第一沟槽内及所述第一外延层上表面的第二外延层;

28、采用化学机械研磨工艺,对所述第二外延层进行平坦化处理,以使所述第二外延层上表面及第一外延层上表面平齐。

29、在一可实施方式中,所述形成位于所述第二外延层内的栅极连接柱,包括:

30、形成位于所述第二外延层上表面的光刻胶层;

31、形成位于所述光刻胶层上的孔洞位置;

32、沿所述孔洞位置刻蚀所述第二外延层,形成从所述第二外延层上表面延伸至所述下栅极导体的孔洞;

33、形成位于所述孔洞内表面及所述第一外延层和所述第二外延层上表面的第三介质层;

34、去除所述孔洞底面及所述第一外延层和所述第二外延层上表面的所述第三介质层;

35、形成位于所述孔洞内的栅极连接柱,所述栅极连接柱的一端与所述下栅极导体相连。

36、在一可实施方式中,所述形成位于所述第二外延层上表面的第二介质层及上栅极导体,包括:

37、形成位于所述第一外延层上表面和所述第二外延层上表面的第二介质层;

38、形成位于所述第二介质层上表面的上栅极导体;

39、去除所述第一外延层上表面的所述第二介质层及所述上栅极导体,并保留位于所述第二外延层上表面的所述第二介质层及所述上栅极导体。

40、在一可实施方式中,所述形成位于所述上栅极导体与所述下栅极导体两侧的源极与漏极,包括:

41、形成位于所述上栅极导体和所述下栅极导体两侧的第一掺杂类型的阱区;

42、形成位于所述第一掺杂类型的阱区内的第二掺杂类型的掺杂区,以形成所述源极与漏极。

43、本技术的沟槽型mosfet及其制造方法,通过栅极连接柱将上栅极导体与下栅极导体连接成环形栅极结构,环形栅极结构的设计使得源极与漏极之间有三条独立的沟道,可以对源极与漏极之间的载流子进行分流,抑制载流子在沟道的库伦散射,使载流子迁移率提升,进而提高器件速度。另外环形栅极结构提高了栅极对沟道的控制,减小了源极与漏极之间耗尽层宽度,有效抑制源极与漏极串通等短沟道效应。

44、应当理解,本部分所描述的内容并非旨在标识本技术的实施例的关键或重要特征,也不用于限制本技术的范围。本技术的其它特征将通过以下的说明书而变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!