一种基于LTCC的片上变压器结构与制造方法与流程

本发明属于半导体,具体涉及一种基于ltcc的片上变压器结构与制造方法。

背景技术:

1、片上变压器是在具有电压差的两个电子回路之间进行隔离信号传输的系统所需重要集成无源器件之一,在mosfet/igbt门驱动、数据总线隔离等电子应用中被广泛应用。片上变压器具有低功耗、体积小、可集成等优势,基于片上变压器的磁隔数字隔离芯片与传统的隔离器相比,具有隔离强度、体积、传输速度等多方面的优势。片上变压器的耦合系数、品质因子、工作频率等重要参数受到结构尺寸、材料参数等多方面因素的影响,其中关键因素包括绝缘介质层的参数、厚度、金属线圈的尺寸、线圈圈数等。因此,选取合适的生产工艺、材料、结构等,才能实现极佳性能的片上变压器。

2、从结构划分,片上变压器的通常具有绕线型、叠层型、平面型等基本结构,其中绕线型是由mems工艺制成,小型化难度较大;平面型通常具有耦合效率小的问题;叠层型结构能够实现较大的品质因子以及较小的占地面积,但是引入磁芯的工艺通常具有较大的困难。

3、从加工工艺划分,片上变压器通常通过cmos、pcb、mems、ltcc等工艺制备,其中cmos工艺很难实现较大的铜布线厚度,因而品质因子受限;pcb工艺的器件难以承受高温的冲击,在恶劣环境下使用具有较大的不稳定性;mems工艺器件则通常成本较大;ltcc工艺既能实现低成本大规模生产,又具有极高的稳定性。但是目前ltcc工艺制备的片上变压器耦合系数和耦合效率有待提高,以满足隔离芯片性能提升的要求。

技术实现思路

1、本发明的目的是提供一种基于ltcc的片上变压器结构与制造方法,利用磁芯材料、叠层式片上变压器设计、ltcc工艺等技术,能够制备出具有较高耦合系数、较高品质因子的片上变压器,满足隔离芯片等应用要求。

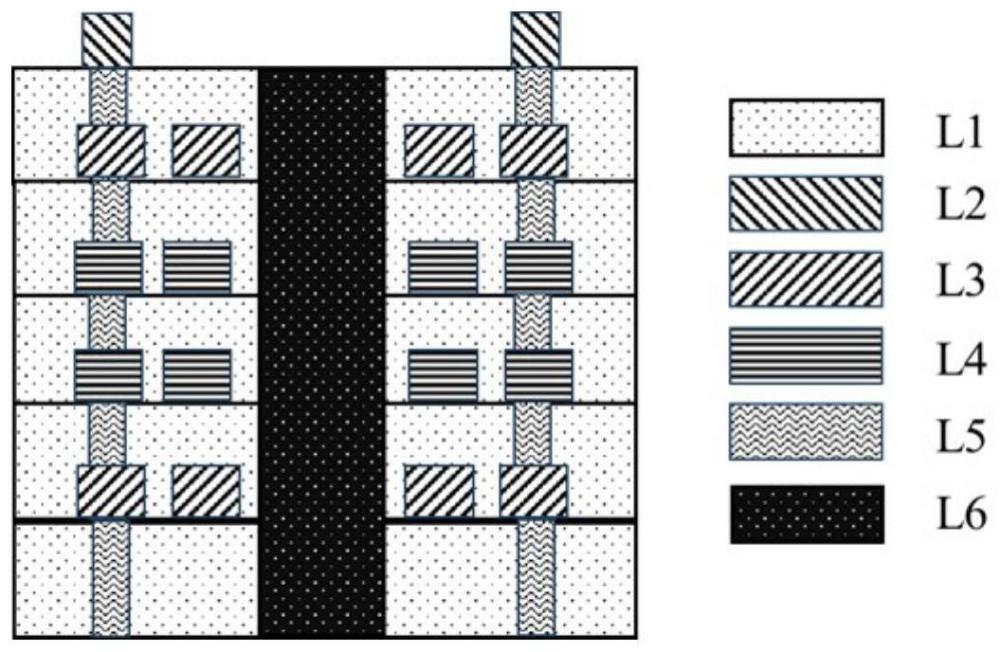

2、为了实现上述目的,本发明所采用的技术方案是:一种基于ltcc的片上变压器,包括由多个单层陶瓷基板叠压而成的多层陶瓷基板结构,所述单层陶瓷基板上填充有导电填充剂,相邻层的单层陶瓷基板通过导电填充剂电性互联;除最上层的单层陶瓷基板外,其余各单层陶瓷基板表面均设置有线圈图案,所述线圈图案为感应线圈图案或屏蔽线圈图案,不同层的线圈图案通过所述的导电填充剂实现电路连通;最上方的单层陶瓷基板上还设置有用于和芯片电性连接的电性端口,电性端口包括输入端口和输出端口,输入端口和最上层的感应线圈图案电性连接,输出端口和最下层的感应线圈图案连接;所述多层陶瓷基板结构上还在所述线圈图案处设置有贯穿各层陶瓷基板的磁芯。

3、两个设置有感应线圈图案的单层陶瓷基板之间存在至少一个设置有屏蔽线圈图案的单层陶瓷基板。

4、所述感应线圈图案为连续的螺旋环路,所述的屏蔽线圈图案为断开的螺旋环路。

5、所述磁芯包括设置在所述线圈图案的内部或边部的一个,或者分布设置在所述线圈图案的内部和/或边部的多个。

6、所述单层陶瓷基板的厚度为10–30微米,精度误差小于1微米。

7、所述单层陶瓷基板的相对磁导率为3-7。

8、一种片上变压器的制备方法,用于制备所述的片上变压器,包括如下步骤:

9、步骤一,制备填充有导电填充剂的单层陶瓷基板;

10、步骤二,在单层陶瓷基板上按照设计的图案制备感应线圈图案或屏蔽线圈图案,感应线圈图案和屏蔽线圈图案均与相应基板上的导电填充剂电性连接;在作为片上变压器最上层的单层陶瓷基板上制备用于和芯片电性连接的电性端口,电性端口与所在基板上的导电填充剂电性连接;

11、步骤三,将步骤二处理后的多个单层陶瓷基板依次叠放并叠压在一起,得到多层陶瓷基板结构;

12、步骤四,在多层陶瓷基板结构上切割出用于填充磁性材料的通孔,再将磁性材料填充到通孔中得到磁芯,所述通孔设置在所述感应线圈图案或屏蔽线圈图案处;

13、步骤五,将已经填充磁性材料后的多层陶瓷基板结构加热烧结,降温后得到所制备的片上变压器。

14、当多层陶瓷基板结构的尺寸能够制备多个片上变压器时,在步骤四制作磁芯后,按照各个片上变压器的尺寸,对多层陶瓷基板结构进行边界切割。

15、所述步骤五的烧结方式采用梯度加热和梯度退温相结合的方式。

16、所述梯度加热的方法是:经过12小时,从室温加热到(500±5)℃,并在该温度条件下稳定2小时后,再经过6小时,缓慢加热至(900±5)℃,稳定1小时后,再经过4小时加热至(1000±5)℃,并保持稳定。

17、所述梯度退温的方法是:经12小时,从加热的最高温度降温到(600±5)℃,并在(600±5)℃条件下稳定2小时后,再经过6小时缓慢降温至室温;梯度加热和梯度退温的总时长为20-40小时。本发明的有益效果是:本发明方案引入了一种高耦合效率带屏蔽层的片上变压器结构,通过合理设计感应线圈图案层来优化初级线圈(最上层的感应线圈)、次级线圈(最下层的感应线圈)等的自感值和品质因子,通过合理设计陶瓷基板厚度来优化互感值和耦合系数,通过引入磁芯材料极大提高片上变压器的耦合系数,进而提高变压器的耦合效率,通过合理设计屏蔽线圈图案来减小感应线圈之间的寄生电容,相比传统的无磁芯片上变压器,本结构具有体积小、抗共模噪声干扰能力强、隔离电压高、耦合效率极大等优势。

18、本发明方案引入了基于ltcc工艺的低成本片上变压器制造方法,相比传统的基于cmos的片上变压器制造方法而言,本流程能够与成熟的ltcc工艺相兼容,具有大规模低成本生产片上变压器的能力,并且利用引线键合的封装方式,较大提高了封装芯片系统的电磁干扰能力,降低相关芯片系统的制造成本,通过三维集成封装方案降低了基于片上变压器芯片的占地面积,适用于后续相关基于电磁感应的隔离型芯片的应用。

19、综上所述,本发明通过结合ltcc和磁芯结构设计的创新思路,能够有效提高耦合系数。相较于现有的方法,该方法具有成本低、小型化、隔离度大、耦合系数大等技术优势,为数字隔离芯片技术的性能提升提供了一种新的解决方案。

技术特征:

1.一种基于ltcc的片上变压器,包括由多个单层陶瓷基板叠压而成的多层陶瓷基板结构,其特征在于:所述单层陶瓷基板上填充有导电填充剂,相邻层的单层陶瓷基板通过导电填充剂电性互联;除最上层的单层陶瓷基板外,其余各单层陶瓷基板表面均设置有线圈图案,所述线圈图案为感应线圈图案或屏蔽线圈图案,不同层的线圈图案通过所述的导电填充剂实现电路连通;最上方的单层陶瓷基板上还设置有用于和芯片电性连接的电性端口,电性端口包括输入端口和输出端口,输入端口和最上层的感应线圈图案电性连接,输出端口和最下层的感应线圈图案连接;所述多层陶瓷基板结构上还在所述线圈图案处设置有贯穿各层陶瓷基板的磁芯。

2.根据权利要求1所述的一种基于ltcc的片上变压器,其特征在于:两个设置有感应线圈图案的单层陶瓷基板之间存在至少一个设置有屏蔽线圈图案的单层陶瓷基板。

3.根据权利要求1或2所述的一种基于ltcc的片上变压器,其特征在于:所述感应线圈图案为连续的螺旋环路,所述的屏蔽线圈图案为断开的螺旋环路。

4.根据权利要求1所述的一种基于ltcc的片上变压器,其特征在于:所述磁芯包括设置在所述线圈图案的内部或边部的一个,或者分布设置在所述线圈图案的内部和/或边部的多个。

5.根据权利要求1所述的一种基于ltcc的片上变压器,其特征在于:所述单层陶瓷基板的厚度为10–30微米,精度误差小于1微米。

6.根据权利要求1所述的一种基于ltcc的片上变压器,其特征在于:所述单层陶瓷基板的相对磁导率为3-7。

7.一种片上变压器的制备方法,用于制备如权利要求1-6任一项所述的片上变压器,包括如下步骤:

8.根据权利要求7所述的一种片上变压器的制备方法,其特征在于:当多层陶瓷基板结构的尺寸能够制备多个片上变压器时,在步骤四制作磁芯后,按照各个片上变压器的尺寸,对多层陶瓷基板结构进行边界切割。

9.根据权利要求7所述的一种片上变压器的制备方法,其特征在于:所述步骤五的烧结方式采用梯度加热和梯度退温相结合的方式。

10.根据权利要求9所述的一种片上变压器的制备方法,其特征在于:所述梯度加热的方法是:经过12小时,从室温加热到(500±5)℃,并在该温度条件下稳定2小时后,再经过6小时,缓慢加热至(900±5)℃,稳定1小时后,再经过4小时加热至(1000±5)℃,并保持稳定。

11.根据权利要求9所述的一种片上变压器的制备方法,其特征在于:所述梯度退温的方法是:经12小时,从加热的最高温度降温到(600±5)℃,并在(600±5)℃条件下稳定2小时后,再经过6小时缓慢降温至室温;梯度加热和梯度退温的总时长为20-40小时。

技术总结

一种基于LTCC的片上变压器,主要由多个单层陶瓷基板叠压而成,单层陶瓷基板上填充有导电填充剂,相邻层的单层陶瓷基板通过导电填充剂电性互联;除最上层的单层陶瓷基板外,其余各单层陶瓷基板表面均设置有线圈图案,线圈图案为感应线圈图案或屏蔽线圈图案,不同层的线圈图案通过导电填充剂实现电路连通;最上方的单层陶瓷基板上还设有用于和芯片电性连接的电性端口,电性端口包括输入端口和输出端口,输入端口和最上层的感应线圈图案电性连接,输出端口和最下层的感应线圈图案连接;所述多层陶瓷基板结构上还在所述线圈图案处设置有贯穿各层陶瓷基板的磁芯。本发明能够制备出具有较高耦合系数、较高品质因子的片上变压器,满足隔离芯片等应用要求。

技术研发人员:罗邺,闫宇,蒲大勇,王晓宇,张琦,戴正飞,李德志

受保护的技术使用者:钱塘科技创新中心

技术研发日:

技术公布日:2024/2/25

- 还没有人留言评论。精彩留言会获得点赞!