一种n层堆叠LDMOS器件及其制备方法与流程

本发明涉及半导体器件,广泛应用于电机驱动器、开关电源和功率放大器的输出级等领域中,具体涉及一种n层堆叠ldmos器件及其制备方法。

背景技术:

1、mosfet功率器件作为半导体器件的核心,相关的专家、学者以及研究者从未中断对其研究,从优化ldmos器件的resurf技术、rebulf技术以及soi结构等,到优化终端结构的扩散保护环技术、场版技术、场限环技术等,都在推动mosfet功率器件的快速发展。虽然这些技术均能够使硅基mosfet功率器件在比导通电阻与击穿电压之间取一个较好的折中值,从而缓解比导通电阻与击穿电压的对立关系,但是硅基mosfet功率器件中比导通电阻与击穿电压的对立关系仍然是阻碍其发展的关键因素。因此,研究具有高耐压与低比导通电阻的mosfet功率器件是十分必要的。

技术实现思路

1、本发明的目的在于提供一n层堆叠ldmos器件。

2、为达此目的,本发明采用以下技术方案:

3、一种n层堆叠ldmos器件,包括基底及sio2层,所述基底包括p型衬底ⅰ,以及由下至上依次交叉堆叠的n型漂移区和p型衬底ⅱ,每层n型漂移区的上表面均设置有p-top区和n-top区,每层p型衬底ⅱ内均设置有p型浮空层,每层p型衬底ⅱ的上表面均设置有p型埋层,p型衬底ⅱ及n型漂移区的两侧均刻蚀有凹槽,第一层n型漂移区与位于最上方的n型漂移区的左上区域均设置有源极p+区和源极n+区,右上区域均设置有漏极n+区,源极p+区和源极n+区均被p-body区包围,所述ldmos器件还包括设置在sio2层内的源极、栅极和漏极,源极的底部紧贴源极p+区、源极n+区设置,栅极的底部紧贴sio2层设置,漏极紧贴漏极n+区的上表面设置。

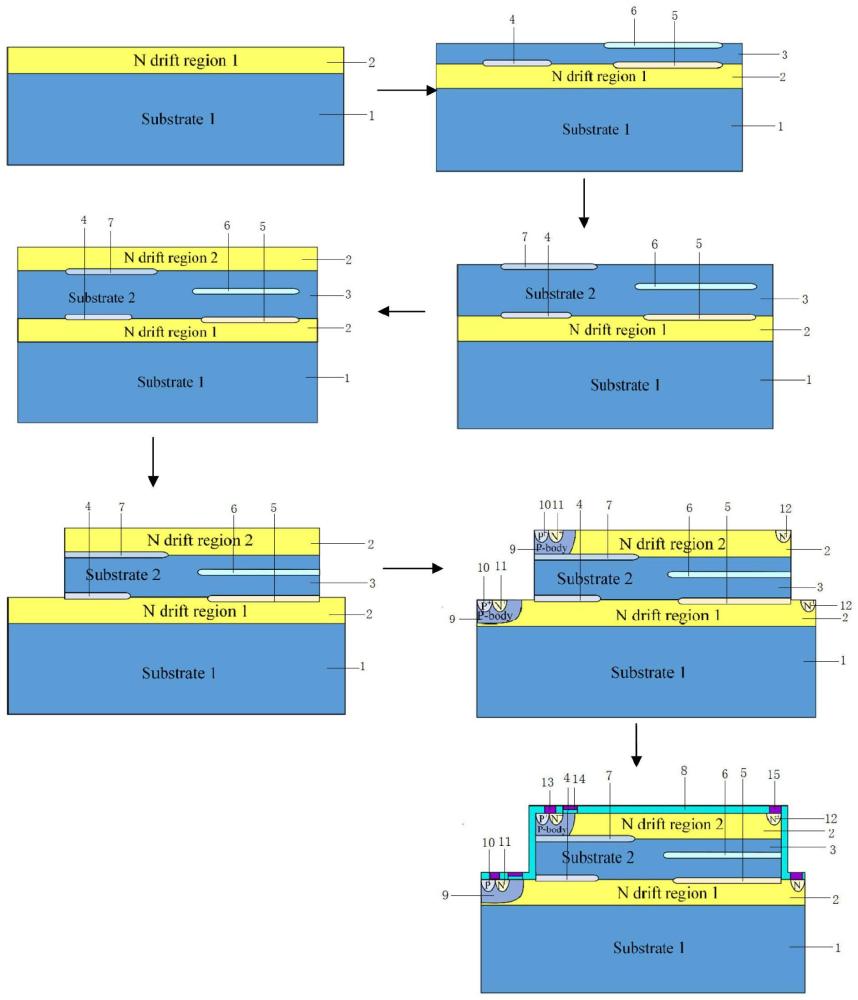

4、本发明的另一个目的是提供上述n层堆叠ldmos器件的制备方法,包括以下步骤:

5、s1,在p型衬底ⅰ的上方外延生长一层n型漂移区;

6、s2,经过两次离子注入与加热扩散,在n型漂移区上分别形成掺杂浓度为8x1016cm-3 的p-top区和和掺杂浓度为5x1016cm-3的n-top区,之后通过外延生长一层掺杂浓度为5x1014cm-3的p型衬底ⅱ,随后通过离子注入和加热扩散,在该层p型衬底ⅱ上形成部分p型浮空层;

7、s3,步骤s2的基础上,继续外延生长p型衬底ⅱ,而后在其上表面通过离子注入与加热扩散形成部分p型埋层;

8、s4,通过外延法在p型衬底ⅱ上再生长一层掺杂浓度为8x1015cm-3的n型漂移区;

9、s5,采用干法刻蚀,在p型衬底ⅱ和第二层n型漂移区的两端刻蚀出两个凹槽,为下一步离子注入做准备;

10、s6,经过多次离子注入与加热扩散,在第一层n型漂移区和第二层n型漂移区的顶端形成源极p+区、源极n+区、p-body区以及漏极n+区;

11、s7,经过高温氧化生长一层sio2,采用干法刻蚀在第一层n型漂移区和第二层n型漂移区的顶端形成ldmos器件的栅极、源极、漏极的图形;经过金属沉积形成器件的栅极、源极及漏极。

12、作为一种具体的实施方式,所述制备过程中,当基底中有多层p型衬底ⅱ及n型漂移区时,在步骤s5中,重复步骤s2至s4的操作,而后再进行凹槽的刻蚀。

13、作为一种具体的实施方式,步骤s2中,通过离子注入硼元素形成p-top区,注入能量为40-80kev,剂量为1-3e15;通过离子注入磷元素形成n-top区,注入能量为80-120kev,剂量为3-5e15,加热扩散的温度为1100-1150℃,时间均为100-200min。

14、作为一种具体的实施方式,p型浮空层和p型埋层均是通过离子注入硼元素形成,注入能量均为30-50kev,剂量为1-5e12,加热扩散的温度均为1100-1150℃,时间均为100-200min。

15、作为一种具体的实施方式,步骤s6中,p-body区和源极p+区采用了硼离子注入,注入能量为50-80kev,剂量为1-3e15;源极n+区、漏极n+区用了磷离子注入,注入能量为80-120kev,剂量为3-5e15,加热扩散的温度均为1150℃,时间为100-150min。

16、作为一种具体的实施方式,sio2层的厚度为5000-10000埃。

17、与现有技术相比,本发明的技术方案具有以下优点:本发明制备得到了一种n层堆叠ldmos器件,通过设置多层p型衬底ⅱ和n型漂移区可有效降低比导通电阻和提高击穿电压,这种结构通过多层衬底的耗尽增加了漂移区的浓度,并且通过增加电流路径的方式大大增加了开态时的导通电流,通过n型区与p型区交替外延实现ldmos器件的堆叠,为堆叠技术提出了新的设计思路。

技术特征:

1.一种n层堆叠ldmos器件,其特征在于,包括基底及sio2层,所述基底包括p型衬底ⅰ,以及由下至上依次交叉堆叠的n型漂移区和p型衬底ⅱ,每层n型漂移区的上表面均设置有p-top区和n-top区,每层p型衬底ⅱ内均设置有p型浮空层,每层p型衬底ⅱ的上表面均设置有p型埋层,p型衬底ⅱ及n型漂移区的两侧均刻蚀有凹槽,第一层n型漂移区与位于最上方的n型漂移区的左上区域均设置有源极p+区和源极n+区,右上区域均设置有漏极n+区,源极p+区和源极n+区均被p-body区包围,所述ldmos器件还包括设置在sio2层内的源极、栅极和漏极,源极的底部紧贴源极p+区、源极n+区设置,栅极的底部紧贴sio2层设置,漏极紧贴漏极n+区的上表面设置。

2.一种如权利要求1所述的n层堆叠ldmos器件的制备方法,其特征在于,包括以下步骤:

3.根据权利要求2所述的一种n层堆叠ldmos器件的制备方法,其特征在于,所述制备过程中,当基底中有多层p型衬底ⅱ及n型漂移区时,在步骤s5中,重复步骤s2至s4的操作,而后再进行凹槽的刻蚀。

4.根据权利要求2所述的一种n层堆叠ldmos器件的制备方法,其特征在于,步骤s2中,通过离子注入硼元素形成p-top区,注入能量为40-80kev,剂量为1-3e15;通过离子注入磷元素形成n-top区,注入能量为80-120kev,剂量为3-5e15,加热扩散的温度为1100-1150℃,时间均为100-200min。

5.根据权利要求2所述的一种n层堆叠ldmos器件的制备方法,其特征在于,p型浮空层和p型埋层均是通过离子注入硼元素形成,注入能量均为30-50kev,剂量为1-5e12,加热扩散的温度均为1100-1150℃,时间均为100-200min。

6.根据权利要求2所述的一种n层堆叠ldmos器件的制备方法,其特征在于,步骤s6中,p-body区和源极p+区采用了硼离子注入,注入能量为50-80kev,剂量为1-3e15;源极n+区、漏极n+区用了磷离子注入,注入能量为80-120kev,剂量为3-5e15,加热扩散的温度均为1150℃,时间为100-150min。

7.根据权利要求2所述的一种n层堆叠ldmos器件的制备方法,其特征在于,sio2层的厚度为5000-10000埃。

技术总结

本发明公开了一种n层堆叠LDMOS器件及其制备方法,该器件包括基底及SiO<subgt;2</subgt;层,基底包括P型衬底Ⅰ,以及由下至上依次交叉堆叠的N型漂移区和P型衬底Ⅱ,每层N型漂移区的上表面均设置有P‑top区和N‑top区,每层P型衬底Ⅱ内设置有P型浮空层、上表面设置有P型埋层,P型衬底Ⅱ及N型漂移区的两侧均刻蚀有凹槽,第一层N型漂移区与位于最上方的N型漂移区的左上区域均设置有源极P+区和源极N+区,右上区域均设置有漏极N+区,源极P+区和源极N+区均被P‑body区包围,LDMOS器件还包括设置在SiO<subgt;2</subgt;层内的源极、栅极和漏极。该器件降低了比导通电阻、提高了击穿电压,同时增加了开态时的导通电流。

技术研发人员:付国振,周炳

受保护的技术使用者:德兴市意发功率半导体有限公司

技术研发日:

技术公布日:2024/2/29

- 还没有人留言评论。精彩留言会获得点赞!