一种浅沟槽隔离结构及制备方法与流程

本申请属于半导体,涉及一种浅沟槽隔离结构及制备方法。

背景技术:

1、在当前的亚微米工艺中,浅沟槽隔离(shallow trench isolation,sti)技术被普遍应用,sti技术缩减了隔离区域的面积,提供了极小的有源区侵入及更平坦的表面。现有技术中在制备浅沟槽隔离结构时,如图1所示,去除牺牲氧化层的过程中刻蚀液会腐蚀与外延层2相接触区域的隔离氧化层6,在隔离氧化层6中形成与外延层2有源区相接触的凹陷区7,一般称为“divot”;如图2所示,于外延层2上形成栅氧层8和栅极多晶硅9,这种“divot”现象会导致晶体管栅极在跨越sti与有源区域时,栅极多晶硅9会填入凹陷区7中,从而在该处产生一个寄生器件(parasitic device),这个寄生器件的开启电压vt比原来设计的正常晶体管vt低很多,在正常晶体管操作时会产生额外的漏电,影响晶体管性能,并且,也会造成晶体管栅极多晶硅刻蚀时更容易出现残留物等缺陷。

2、因此,如何提供一种浅沟槽隔离结构及制备方法,以避免隔离氧化层中出现边缘凹陷,进而避免产生寄生器件,提高晶体管性能,成为本领域技术人员亟待解决的技术问题。

技术实现思路

1、鉴于以上所述现有技术的缺点,本申请的目的在于提供一种浅沟槽隔离结构及制备方法,用于解决现有技术中浅沟槽隔离结构的隔离氧化层中出现边缘凹陷,降低晶体管性能的问题。

2、为实现上述目的及其他相关目的,本申请提供一种浅沟槽隔离结构的制备方法,包括以下步骤:

3、形成位于衬底上表面的外延层;

4、形成位于所述外延层上表面的牺牲氧化层;

5、形成从所述牺牲氧化层的上表面向下延伸至所述外延层中的沟槽;

6、形成位于所述沟槽内的阻挡层和隔离氧化层,其中,所述阻挡层覆盖所述沟槽的内表面,以将所述隔离氧化层与所述外延层隔离;

7、去除所述牺牲氧化层。

8、可选地,形成所述沟槽的方法包括:

9、形成位于所述牺牲氧化层上方的掩膜层,并图形化所述掩膜层,以形成所述沟槽的位置;

10、沿所述沟槽的位置向下刻蚀所述牺牲氧化层和所述外延层以形成所述沟槽,并去除所述掩膜层。

11、可选地,形成位于所述沟槽内的阻挡层及隔离氧化层的步骤包括:

12、形成位于所述沟槽内表面及所述牺牲氧化层上表面的所述阻挡层;

13、形成位于所述沟槽内及所述阻挡层上表面的所述隔离氧化层;

14、去除所述牺牲氧化层上方的所述隔离氧化层及所述阻挡层,以使所述阻挡层的上表面与所述牺牲氧化层的上表面平齐。

15、可选地,采用湿法刻蚀法去除所述牺牲氧化层。

16、可选地,湿法刻蚀去除所述牺牲氧化层的刻蚀液包括hf溶液或boe溶液。

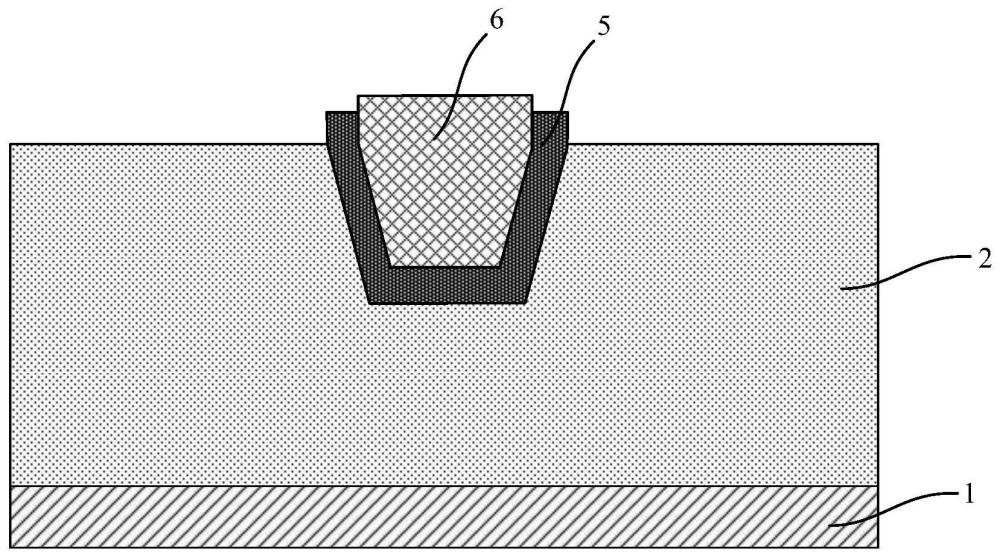

17、可选地,所述牺牲氧化层的厚度范围为所述阻挡层的厚度范围为

18、可选地,所述阻挡层包括氮化硅层或氮氧化硅层。

19、本申请还提供一种浅沟槽隔离结构,包括:

20、衬底;

21、外延层,位于所述衬底的上表面,所述外延层中具有由所述外延层的上表面向下延伸至所述外延层内部的沟槽;

22、阻挡层,位于所述沟槽的内表面,且所述阻挡层凸出于所述外延层的上表面;

23、隔离氧化层,位于所述沟槽中,所述隔离氧化层通过所述阻挡层与所述外延层隔离,且所述隔离氧化层凸出于所述外延层的上表面。

24、可选地,所述阻挡层的厚度范围为

25、可选地,所述阻挡层包括氮化硅层或氮氧化硅层。

26、如上所述,本申请的浅沟槽隔离结构及制备方法中,由于阻挡层的存在,能够阻止湿法刻蚀液对隔离沟槽与外延层有源区交接处的隔离氧化层发生反应,避免隔离氧化层中出现凹陷区,进而避免产生寄生器件,提高晶体管性能。

技术特征:

1.一种浅沟槽隔离结构的制备方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的浅沟槽隔离结构的制备方法,其特征在于,形成所述沟槽的方法包括:

3.根据权利要求1所述的浅沟槽隔离结构的制备方法,其特征在于,形成位于所述沟槽内的阻挡层及隔离氧化层的步骤包括:

4.根据权利要求1所述的浅沟槽隔离结构的制备方法,其特征在于:采用湿法刻蚀法去除所述牺牲氧化层。

5.根据权利要求4所述的浅沟槽隔离结构的制备方法,其特征在于:湿法刻蚀去除所述牺牲氧化层的刻蚀液包括hf溶液或boe溶液。

6.根据权利要求1所述的浅沟槽隔离结构的制备方法,其特征在于:所述牺牲氧化层的厚度范围为所述阻挡层的厚度范围为

7.根据权利要求1所述的浅沟槽隔离结构的制备方法,其特征在于:所述阻挡层包括氮化硅层或氮氧化硅层。

8.一种浅沟槽隔离结构,其特征在于,包括:

9.根据权利要求8所述的浅沟槽隔离结构,其特征在于:所述阻挡层的厚度范围为

10.根据权利要求8所述的浅沟槽隔离结构,其特征在于:所述阻挡层包括氮化硅层或氮氧化硅层。

技术总结

本申请提供一种浅沟槽隔离结构及制备方法,该制备方法包括:形成位于衬底上表面的外延层;形成位于所述外延层上表面的的牺牲氧化层;形成从所述牺牲氧化层的上表面向下延伸至所述外延层中的沟槽;形成位于所述沟槽内的阻挡层和隔离氧化层,其中,所述阻挡层覆盖所述沟槽的内表面,以将所述隔离氧化层与所述外延层隔离;去除所述牺牲氧化层。本申请的浅沟槽隔离结构及制备方法中,由于阻挡层的存在,能够阻止湿法刻蚀液对隔离沟槽与外延层有源区交接处的隔离氧化层发生反应,避免隔离氧化层中出现凹陷区,进而避免产生寄生器件,提高晶体管性能。

技术研发人员:李海锋,周微,郭扬明

受保护的技术使用者:杭州富芯半导体有限公司

技术研发日:

技术公布日:2024/3/21

- 还没有人留言评论。精彩留言会获得点赞!