一种碳化硅MOSFET器件及其制备方法与流程

本发明涉及一种半导体元器件以及其制备方法,尤其涉及一种碳化硅mosfet器件及其制备方法。

背景技术:

1、以碳化硅(silicon carbide,sic)为代表的第三代半导体材料的发展开启了半导体产业的新局面;sic功率器件可同时实现高击穿电压、低导通电阻、高开关速度以及易散热等优异性能,在高能效、高功率、高温电力电子技术中具有明显竞争力,已成为当前功率半导体技术的研究热点。

2、相比于平面栅型sic mosfet器件,沟槽栅型sic mosfet不存在寄生结型场效应晶体管区(junction field electric transistor,jfet),器件导通电阻可明显降低,并且原胞尺寸进一步缩小,可进一步提高器件功率密度,降低系统功耗,性能优势明显与应用前景非常广阔。然而,沟槽型sic mosfet器件由于受沟槽底角处电场聚集效应的影响,极易造成器件过早击穿,甚至烧毁。另外,沟槽底部栅氧内的高电场极易造成栅氧击穿,导致器件失效。因此,如何调制沟槽型sic mosfet器件沟槽底部电场,降低栅氧击穿风险,是沟槽型sicmosfet器件的一个难点与热点问题。在申请号为2021107267653的专利公开文本中公开了一种引入柱区电场调制结构的沟槽型sic mosfet器件,可有效舒缓沟槽底部电场分布,消除电场聚集效应,还可屏蔽栅氧内电场强度,降低栅氧内电场强度,避免栅氧击穿,从而防止器件过早击穿烧毁、提升器件可靠性。然而,引入的柱区结构会与器件原有阱区发生自然耗尽作用,从而恶化器件导通能力。

技术实现思路

1、发明目的:本发明目的是提供一种既能保护沟槽底部与栅氧,又能避免自然耗尽作用的碳化硅mosfet器件;本发明另一目的是提供上述碳化硅mosfet器件的制备方法。

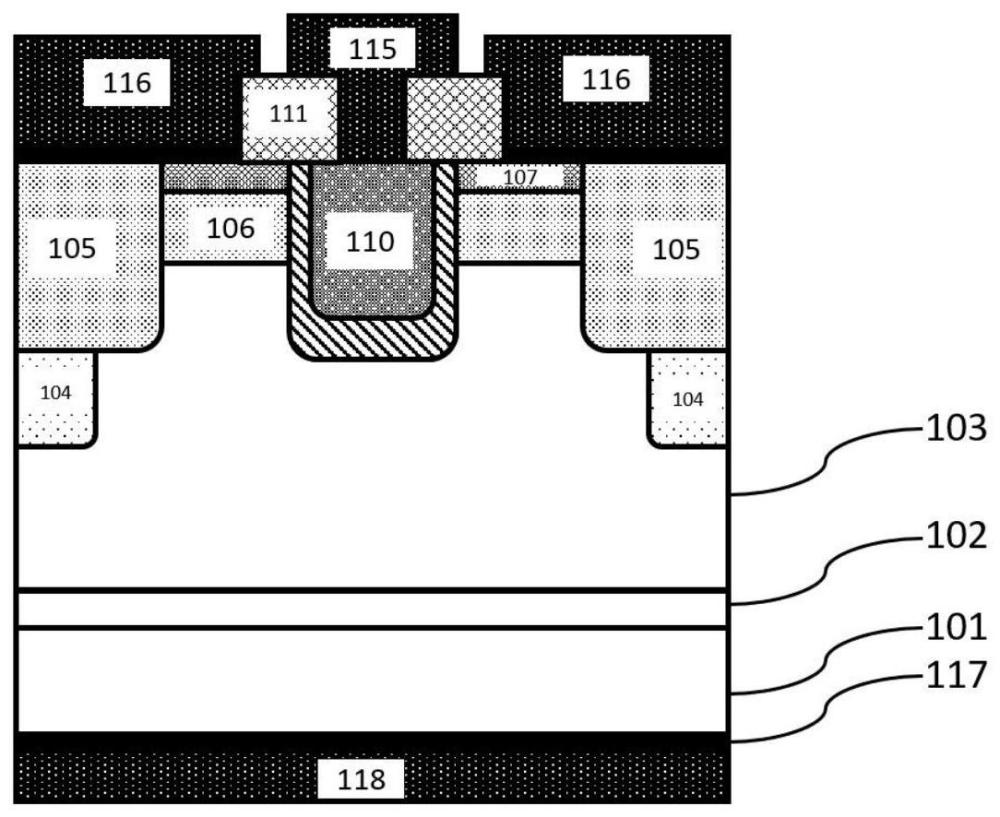

2、技术方案:本发明所述的一种碳化硅mosfet器件,包括:

3、第一掺杂类型的重掺杂的衬底;

4、第一掺杂类型的轻掺杂的外延层,其位于所述衬底的上表面;

5、第二掺杂类型的阶梯层,其对称设置于所述外延层中,所述阶梯层为从下到上宽度依次增大的第二掺杂类型的阶梯区;

6、第二掺杂类型的阱区,其位于所述外延层中,所述阱区设置于阶梯层最上层的阶梯区一侧;

7、第一掺杂类型的源区,其位于所述阱区中;

8、栅沟槽,其位于所述外延层中,所述栅沟槽设置于阱区之间;

9、第一掺杂类型的多晶硅,其填充于内表面设有栅介质层的栅沟槽内;

10、源极欧姆接触层,位于阶梯区的上表面和源区部分上表面;

11、栅极电极,位于所述多晶硅的上表面;

12、源极电极,位于所述源极欧姆接触层的上表面;

13、钝化层,位于多晶硅和源区的部分上表面,且所述钝化层位于栅极电极和源极电极之间;

14、漏极欧姆接触层,位于所述衬底的下表面;

15、漏极电极,位于所述漏极欧姆接触层的下表面。

16、进一步地,所述第二掺杂类型的阶梯层包括第一阶梯区和第二阶梯区;所述第二阶梯区位于第一阶梯区上方,且第二阶梯区宽度大于第一阶梯区的宽度;除此之外,阶梯层可以由第一阶梯区、第二阶梯区、第三阶梯区或者更多的阶梯区组成。

17、阶梯层除作为电场调制结构,作用是在器件工作在阻断状态时,作为器件电场调制结构,可调制器件内部电场分布,可使得最大电场峰值由沟槽底角处拉至电场调制区底部,从而降低沟槽底角处的电场聚集效应。另外,还可屏蔽沟槽底部栅氧内电场强度,从而避免栅氧击穿。另外,由于阶梯层为从下到上宽度依次增大的第二掺杂类型的阶梯区,从而可避免该电场调制结构与阱区的自然耗尽作用,防止器件导通性能恶化,组成阶梯层的阶梯区越多,则防止器件导通性能恶化效果越好。

18、此外,需要说明的是,所述第一阶梯区与第二阶梯区除作为电场调制结构以外,还会作为器件内部的体二极管结构,在器件工作在反向状态时,担负着反向电流传输的作用。

19、进一步地,所述碳化硅mosfet器件还包括缓冲层,所述缓冲层位于所述衬底与所述外延层之间。

20、进一步地,所述第一掺杂类型为n型,所述第二掺杂类型为p型。

21、进一步地,所述第一掺杂类型为p型,所述第二掺杂类型为n型。

22、进一步地,所述第二掺杂类型的第一阶梯区的深度为0.4~1.2um,宽度为0.3~1.0um,掺杂浓度为1e17~1e19cm-3。

23、进一步地,所述第二掺杂类型的第二阶梯区的深度为1.4~3.0um,宽度为0.5~2.0um,掺杂浓度为1e17~1e19cm-3。

24、进一步地,所述第一阶梯区与第二阶梯区的宽度间距为0.2~1.0um。

25、进一步地,所述第二掺杂类型的阱区的深度为0.6~1.0um,掺杂浓度为1e17~1e18cm-3。

26、本发明所述的一种碳化硅mosfet器件的制备方法,包括以下步骤:

27、s1、提供第一掺杂类型的重掺杂的衬底,于所述衬底的上表面形成第一掺杂类型的轻掺杂的外延层;

28、s2、于所述外延层中形成第二掺杂类型的第一阶梯区;

29、s3、于完成所述步骤2得到的外延层中,于所述第二掺杂类型的第一阶梯区上方形成第二掺杂类型的第二阶梯区;

30、s4、于完成所述步骤3得到的外延层中,于所述第二掺杂类型的第二阶梯区之间形成第二掺杂类型的阱区,于所述第二掺杂类型的阱区中形成第一掺杂类型的源区;

31、s5、于完成所述步骤4得到的外延层中形成栅沟槽;

32、s6、于所述栅沟槽内形成栅介质层;

33、s7、于完成所述步骤6得到的栅沟槽内的栅介质层表面填充第一掺杂类型的多晶硅;

34、s8、于完成所述步骤7得到的外延层表面形成钝化层,于所述钝化层中形成源极窗口;

35、s9、于所述源极窗口内形成源极欧姆接触层;

36、s10、于所述钝化层中对应于所述多晶硅区的位置形成栅极窗口;

37、s11、于所述栅极窗口内形成栅极电极,于所述源极欧姆接触层表面形成源极电极;

38、s12、于完成所述步骤11后对所述第一掺杂类型的重掺杂的衬底底部进行减薄;

39、s13、于完成所述步骤12得到的减薄后的衬底的底部表面形成漏极欧姆接触层,于所述漏极欧姆接触层表面形成漏极电极。

40、进一步地,所述步骤2中,于所述外延层中形成第二掺杂类型的第一阶梯区,包括如下步骤:

41、s2.1、于所述外延层的表面形成离子注入掩膜层,该离子注入掩模层由两层介质膜层构成;其中,第一层介质膜层为氮化硅或多晶硅,厚度为0.5~1.5um;第二层介质膜层为氧化硅,厚度为3~5um;

42、s2.2、于所述离子注入掩膜层的上表面涂覆光刻胶,采用曝光、显影及坚膜等光刻工艺对所述光刻胶进行图形化处理,以形成图形化的光刻胶;

43、s2.3、依据所述图形化的光刻胶采用刻蚀工艺对所述离子注入掩膜层进行刻蚀处理以形成离子注入窗口;其中,所述刻蚀工艺对2.1中所述第二层介质膜层全部刻蚀干净,所述刻蚀工艺将自动停止在所述第一层介质层表面;

44、s2.4、去除所述图形化的光刻胶,并保留刻蚀后的离子注入掩膜层;

45、s2.5、依据所述刻蚀后的离子注入掩膜层,对所述外延层进行铝离子注入工艺以形成第一阶梯区。

46、所述第二层介质膜层将作为离子注入阻挡层,用于阻挡注入离子以防止离子注入进所述外延层中。所述第一层介质膜层有两方面作用。该层作用一是用于步骤2.3中所述刻蚀工艺的刻蚀终止层,即所述刻蚀工艺将所述第二层介质膜层刻蚀干净后,刻蚀至所述第一层介质膜层时,由于刻蚀工艺无法对第一层介质膜层进行刻蚀,刻蚀工艺将自动终止;该层作用二是用于步骤2.5中对所述外延层进行铝离子注入工艺时的离子注入屏蔽层,即通过特定厚度的第二层介质膜层用于屏蔽注入的离子,从而调控注入到外延层内部离子的运动轨迹与分布情况,以形成所需的第一阶梯区。

47、进一步地,所述步骤3中,于完成所述步骤2得到的外延层中,于所述第二掺杂类型的第一阶梯区上方形成第二掺杂类型的第二阶梯区,包括如下步骤:

48、s3.1、于完成所述步骤2.5后在所述刻蚀后的离子注入掩膜层表面再形成一层用于形成第二阶梯区的离子注入掩膜层,厚度为0.2~1.0um;

49、s3.2、采用刻蚀工艺对所述第二阶梯区的离子注入掩膜层进行刻蚀处理以形成第二阶梯区的离子注入窗口;

50、s3.3、依据所述形成的第二阶梯区的离子注入窗口,对所述外延层进行铝离子注入工艺以形成第二阶梯区。

51、所述步骤3利用的是自对准工艺,即于完成所述步骤2.5后在所述刻蚀后的离子注入掩膜层表面再形成一层用于形成第二阶梯区的离子注入掩膜层;采用刻蚀工艺对所述第二阶梯区的离子注入掩膜层进行刻蚀处理以形成第二阶梯区的离子注入窗口。利用自对准工艺可有效保证第二阶梯区与第一阶梯区左右间距对称,还可通过调节用于形成第二阶梯区的离子注入掩膜层的厚度来自动调节第二阶梯区与第一阶梯区的间距。

52、除本专利中所描述的第一阶梯区与第二阶梯区结构以外,还可重复所述步骤3,只需调控优化所述阶梯区的宽度,还可形成具有三个阶梯区或更多个阶梯区的电场调制结构。

53、进一步地,所述步骤6中,于所述栅沟槽内形成栅介质层,包括如下步骤:

54、s6.1、在所述栅沟槽表面利用热氧化工艺(thermal oxidation,to)氧化生长一层二氧化硅层,二氧化硅层厚度为10~20nm;

55、s6.2、在完成所述步骤6.1后,在所述热氧化工艺形成的二氧化硅层表面,利用低压化学气相沉积工艺(low pressure chemical vapor deposition,lpcvd)或高温氧化工艺(high temperature oxidation,hto)再生长一层二氧化硅层,二氧化硅层厚度为30~60nm;

56、s6.3、在完成所述步骤6.2后,对所述两层氧化硅层进行退火工艺处理,退火温度为1100~1300℃,退火时间为30~60min;形成栅沟槽内表面的栅介质层;所述栅介质层由所述步骤6.1与步骤6.2形成的两层二氧化硅层组成。

57、所述步骤6.1中的热氧化工艺的氧化温度为1100~1300℃,氧化气体可以为o2,还可为h2/o2混合气体或含有h2o的o2,其中氧化气体为o2为干法氧化工艺,氧化气体为h2/o2混合气体或含有h2o的o2为湿法氧化工艺。

58、所述步骤6.3中对所述两层氧化硅层进行退火工艺处理有两个目的;目的一是为了对氧化层进行增密以提高膜层的耐压强度;目的二是为了优化修饰氧化硅层与外延层两者之间的界面以提高界面特性。

59、进一步地,所述步骤12中,于完成所述步骤11后对所述第一掺杂类型的重掺杂的衬底底部进行减薄,厚度减薄至120~180um。

60、有益效果:和现有技术相比,本发明具有以下显著的优点:

61、1、本发明碳化硅mosfet器件现有结构中引入阶梯区作为电场调制结构,该结构可有效消除沟槽底角处电场聚集效应,屏蔽栅氧内电场强度,避免栅氧击穿,从而防止器件过早击穿烧毁、提升器件可靠性;同时还可有效避免电场调制结构与阱区的自然耗尽作用,从而防止器件导通性能恶化。

62、2、本发明器件的制备方法简单,效果显著,可实现高性能、批量化碳化硅mosfet器件制备及生产,具有巨大的市场潜力与广泛的应用前景。

- 还没有人留言评论。精彩留言会获得点赞!