基板的对位方法与流程

本发明实施例涉及集成电路制造,尤其涉及一种基板的对位方法。

背景技术:

1、对位标记(业内又称:mark)设置于基板,具体是基板用于设置膜层的侧面,且往往位于基板侧面的角部和/或边缘。对位标记用于各膜层的图案与基板对位,避免膜层的图案在设置过程中偏移基板。

2、现有的基板对位方法,即:每新设一膜层时通过光学识别设备对对位标记进行识别并抓取(抓取,即获得对位标记的对位位置);根据与对位标记对应的对位位置,在绝缘层上形成新设膜层的图案,以避免图案在设置过程中偏移基板。

3、然而,绝缘层设置于基板后,绝缘层会对对位标记形成遮盖。随着膜层的增多,绝缘层遮盖对位标记的遮盖区增厚,对位标记相对光学识别设备的清晰度降低,光学识别设备对对位标记的抓取难度增大,抓取精度低(抓取精度,表征抓取确定的对位标记的对位位置与对位标记的实际位置之间的偏差;抓取精度低即为偏差大),造成新设膜层的图案与基板偏离。并且,膜层越多,新设膜层的图案与基板之间的累计偏离误差越大。

技术实现思路

1、本发明实施例提供一种基板的对位方法,以解决现有的基板对位方法下,随着膜层的增多,绝缘层遮盖对位标记的遮盖区增厚,对位标记相对光学识别设备的清晰度降低,光学识别设备对对位标记的抓取难度增大,抓取准确率低、造成新设膜层的图案与基板偏离的问题。并且,膜层越多,新设膜层的图案与基板之间的累计偏离误差越大的问题。

2、为了解决上述技术问题,本发明是这样实现的:

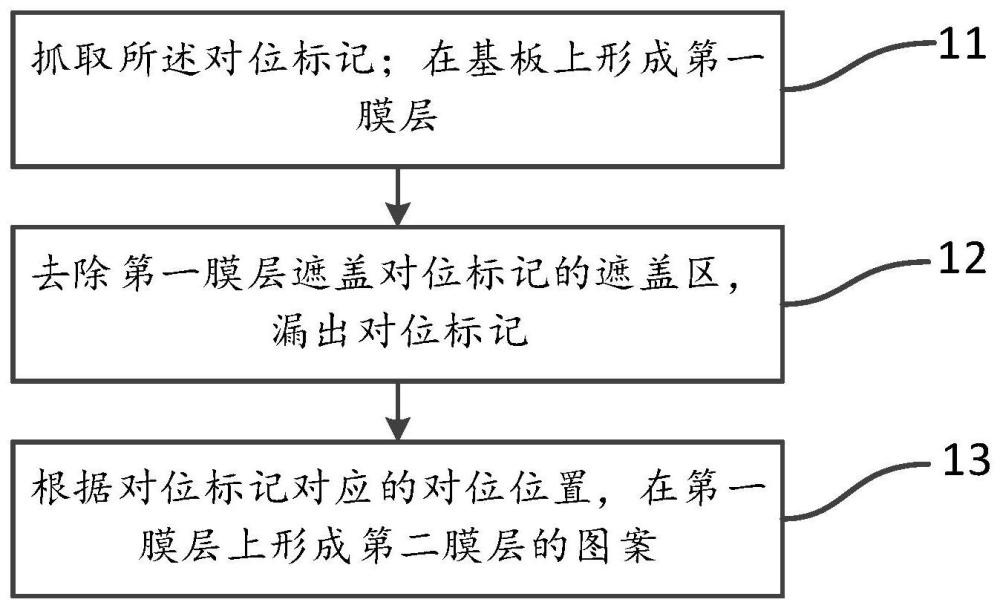

3、第一方面,本发明实施例提供了一种基板的对位方法,所述基板具有至少两个对位标记,所述对位方法包括:

4、抓取所述对位标记;在所述基板上形成第一膜层;

5、去除所述第一膜层遮盖所述对位标记的遮盖区,漏出所述对位标记;

6、根据所述对位标记对应的对位位置,在所述第一膜层上形成第二膜层的图案。

7、可选地,

8、所述第一膜层包括:味之素堆积膜abf膜层;

9、去除所述第一膜层遮盖所述对位标记的遮盖区的步骤,包括:

10、去除所述abf膜层遮盖所述对位标记的遮盖区。

11、可选地,

12、采用二氧化碳激光器去除所述遮盖区。

13、可选地,

14、采用曝光机抓取所述对位标记。

15、可选地,

16、所述对位标记在所述基板上的正投影呈圆形。

17、可选地,

18、所述对位标记呈自边缘朝所述基板的厚度方向凹陷的凹台状。

19、可选地,

20、所述对位标记具有反光标记部,所述反光标记部设于所述对位标记的边缘。

21、可选地,

22、反光标记部包括:第一图形及第二图形;

23、所述第一图形与所述第二图形由反光率不同的材料形成。

24、可选地,

25、抓取所述对位标记的步骤,包括:

26、对所述基板进行照射,根据所述基板的反射光确定所述对位标记。

27、可选地,

28、所述对位标记在所述基板上的正投影呈“十”字形;和/或,

29、所述对位标记在所述基板上的正投影呈“米”字形;和/或,

30、所述对位标记在所述基板上的正投影呈矩形;和/或,

31、所述对位标记在所述基板上的正投影呈三角形。

32、本发明实施例中,通过抓取所述对位标记;在所述基板上形成第一膜层;去除所述第一膜层遮盖所述对位标记的遮盖区,漏出所述对位标记;根据所述对位标记对应的对位位置,在所述第一膜层上形成第二膜层的图案,能够有效避免由绝缘层遮盖对位标记带来的对位标记的抓取精度低的问题,以及避免对位标记抓取精度低带来的新设膜层的图案与基板偏离且膜层越多累计偏离误差越大的问题,提升基板良率。

技术特征:

1.一种基板的对位方法,其特征在于,所述基板具有至少两个对位标记,所述对位方法包括:

2.根据权利要求1所述的基板的对位方法,其特征在于:

3.根据权利要求1所述的基板的对位方法,其特征在于:

4.根据权利要求1所述的基板的对位方法,其特征在于:

5.根据权利要求1所述的基板的对位方法,其特征在于:

6.根据权利要求5所述的基板的对位方法,其特征在于:

7.根据权利要求1所述的基板的对位方法,其特征在于:

8.根据权利要求7所述的基板的对位方法,其特征在于:

9.根据权利要求6至8中任一项所述的基板的对位方法,其特征在于:

10.根据权利要求1所述的基板的对位方法,其特征在于:

技术总结

本发明提供一种基板的对位方法,包括:抓取所述对位标记;在所述基板上形成第一膜层;去除所述第一膜层遮盖所述对位标记的遮盖区,漏出所述对位标记;根据所述对位标记对应的对位位置,在所述第一膜层上形成第二膜层的图案。本发明能够有效避免由绝缘层遮盖对位标记带来的对位标记的抓取精度低的问题,以及避免对位标记抓取精度低带来的新设膜层的图案与基板偏离且膜层越多累计偏离误差越大的问题,提升基板良率。

技术研发人员:刘星华

受保护的技术使用者:成都奕成集成电路有限公司

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!