一种CMOS器件及其制作方法与流程

本技术属于半导体工艺和器件,涉及一种cmos器件及其制作方法。

背景技术:

1、集成电路是具有晶体管、电阻、电容和电感等元件通过布线互连在一起的微型电子器件,在集成电路的组成部分中,电阻是集成电路设计中的不可或缺的组成部分,其在电路设计中主要起到限流、降压、分流及分压等作用,电阻稳定性将直接影响到集成电路中电压的稳定与电路功耗性能。在目前的芯片制作技术中,cmos集成电路的电阻实现方式包括以下几种:多晶硅电阻、阱电阻、mos管电阻以及电容电阻等,其中,多晶硅电阻由于制作方法与cmos工艺完全兼容、制作过程简单且应用方便而被广泛采用。

2、通常情况下,多晶硅的最大电阻率为100ω,芯片的设计规则决定了多晶硅电阻宽度的最小值,使得具有高阻值的多晶硅电阻需要很大的尺寸,而芯片面积的限制又使得大尺寸的多晶硅电阻很难实现,因此通过对多晶硅电阻进行掺杂以获得高阻值多晶硅电阻(high resistance poly,简称hrp),即在制作得到未掺杂的多晶硅电阻块之后,对形成的未掺杂多晶硅电阻区域处进行离子注入以基于离子注入的浓度调节改变hrp阻值,从而达到电路所需hrp的电阻阻值,但是,在实际应用中发现该方法用于制作hrp的制作成本较高且制作得到的hrp的阻值重复性和稳定性较差,在一定程度上限制了hrp在cmos集成电路中的应用。

3、因此,如何提供一种cmos器件及其制作方法,以控制cmos器件中hrp的制作成本及提升hrp的阻值稳定性,成为本领域技术人员亟待解决的一个重要技术问题。

4、应该注意,上面对技术背景的介绍只是为了方便对本技术的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本技术的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本技术的目的在于提供一种cmos器件及其制作方法,用于解决现有技术中对多晶硅进行掺杂以获得hrp的制作方法中存在的制作成本较高及hrp阻值稳定性有待改善的问题。

2、为实现上述目的及其他相关目的,本技术提供一种cmos器件的制作方法,包括以下步骤:

3、形成位于衬底的上表面的第一介质层;

4、形成位于所述第一介质层的上表面的多晶硅层;

5、形成自所述多晶硅层上表面开口并向下延伸的沟槽,所述沟槽至少贯穿所述多晶硅层并部分保留所述多晶硅层以形成多晶硅凸起,所述多晶硅凸起的两侧均具有所述沟槽;

6、形成位于所述沟槽的内表面的第二介质层,位于所述沟槽的底部两侧的所述第一介质层与所述第二介质层共同构成介质层;

7、采用第一离子注入工艺,形成位于所述沟槽底部的所述衬底内的第一源区及第一漏区,并基于所述多晶硅凸起形成电阻层。

8、可选地,所述第一离子注入工艺包括第一道离子注入及第二道离子注入,所述第一道离子注入的注入参数与所述第二道离子注入的注入参数相同或不同,所述注入参数包括能量、浓度及物质中的至少一种。

9、可选地,还包括采用第二离子注入工艺以调整所述电阻层的阻值至预设范围的步骤,所述第二离子注入工艺与所述第一离子注入工艺的离子掺杂类型相同,所述第二离子注入工艺包括第三道离子注入,所述第三道离子注入的能量小于所述第一道离子注入的能量及所述第二道离子注入的能量。

10、可选地,所述介质层的厚度范围为

11、可选地,所述第一道离子注入的注入物质包括b及bf2中的至少一种,所述第一道离子注入的能量范围为10kev~30kev,所述第一道离子注入的浓度范围为2e14 cm-3~2e15cm-3;所述第二道离子注入的注入物质包括b及bf2中的至少一种,所述第二道离子注入的能量范围为10kev~30kev,所述第二道离子注入的浓度范围为2e15 cm-3~1e16 cm-3;所述第三道离子注入的注入物质均包括b及bf2中的至少一种,所述第三道离子注入的能量范围为5kev~20kev,第三道离子注入的浓度范围为1e14 cm-3~1e15 cm-3。

12、可选地,还包括采用第三离子注入工艺形成位于所述衬底内的第二源区及第二漏区的步骤,所述第三离子注入工艺与所述第一离子注入工艺的离子掺杂类型不同。

13、可选地,所述第三离子注入工艺包括第四道离子注入及第五道离子注入,所述第四道离子注入的注入能量大于或等于所述第五道离子注入的注入能量。

14、可选地,所述第四道离子注入的注入物质均包括p及as中的至少一种,其中,所述第四道离子注入的能量范围为20kev~40kev,所述第四道离子注入的浓度范围为2e13cm-3~1e14 cm-3;所述第五道离子注入的注入物质包括p及as中的至少一种,所述第五道离子注入的能量范围为20kev~40kev,所述第五道离子注入的浓度范围为2e15 cm-3~1e16cm-3。

15、可选地,形成位于所述沟槽的内表面的第二介质层包括以下步骤:

16、形成位于所述沟槽的内表面及所述多晶硅凸起的上表面的介质材料层;

17、去除所述介质材料层位于所述多晶硅凸起的上表面的部分,保留下来的所述介质材料层构成所述第二介质层。

18、可选地,还包括进行电阻层关键尺寸的split实验的步骤,进行所述电阻层关键尺寸的split实验的步骤至少在形成所述多晶硅凸起的步骤之前进行,所述split实验基于rs=ρl/w进行,其中,rs为所述电阻层的方块电阻,ρ为所述电阻层的电阻率;l为所述电阻层的长度;w为所述电阻层的宽度。

19、本技术还提供一种cmos器件,包括:

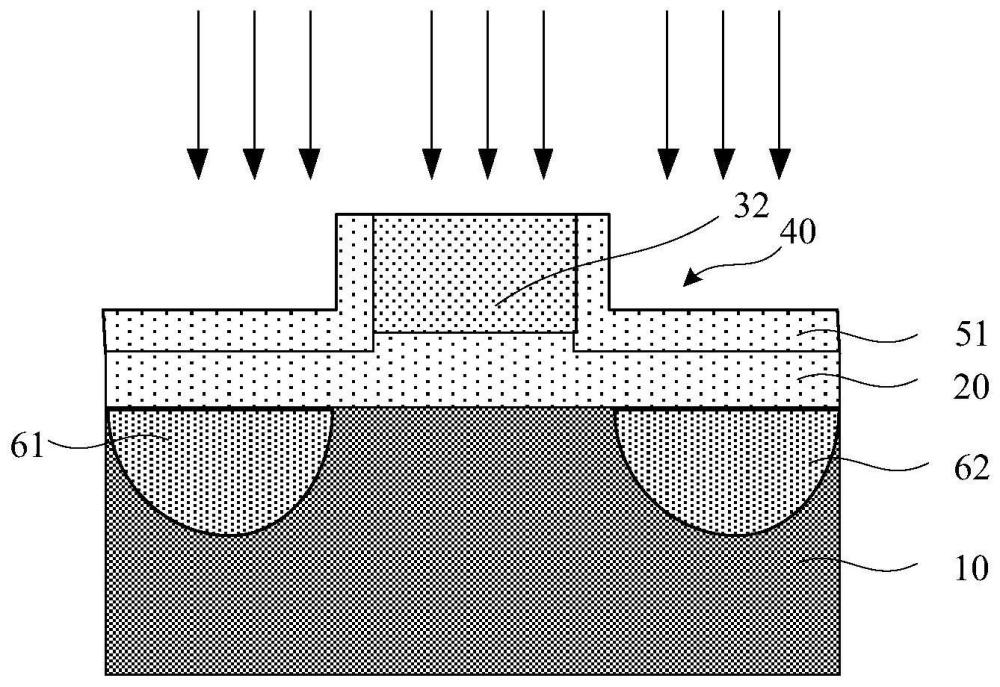

20、衬底;

21、第一介质层,位于所述衬底的上表面;

22、多晶硅层,位于所述第一介质层的上表面;

23、沟槽,自所述多晶硅层上表面开口并向下延伸,所述沟槽至少贯穿所述多晶硅层并部分保留所述多晶硅层以形成多晶硅凸起,所述多晶硅凸起的两侧均具有所述沟槽;

24、第二介质层,位于所述沟槽的内表面,位于所述沟槽的底部两侧的所述第一介质层与所述第二介质层共同构成介质层;

25、第一源区、第一漏区及电阻层,均采用第一离子注入工艺形成,其中,所述第一源区及所述第一漏区均位于所述沟槽底部的所述衬底内,所述电阻层基于所述多晶硅凸起形成。

26、如上所述,本技术的cmos器件的制作方法,将对多晶硅凸起进行离子注入以形成电阻层的步骤与cmos器件中pmos的源漏注入或nmos的源漏注入同步进行,减少一次mask工艺,有效降低器件制作成本,进一步地对离子注入时的工艺步骤及工艺参数进行调整,能够保证cmos中pmos或nmos晶体管的工作性能的同时对电阻层的阻值进行精准调控,以实现电阻层的阻值均匀稳定性和重复性。本技术的cmos器件,具有阻值稳定性和均匀重复性较佳的电阻层,整体制作工艺简单且制作成本较低,具有较强的市场应用前景。

- 还没有人留言评论。精彩留言会获得点赞!