半导体结构及其形成方法

本发明涉及半导体制造工艺,具体涉及一种半导体结构及其形成方法。

背景技术:

1、随着半导体技术的不断发展,集成电路特征尺寸持续微缩,传统三栅或双栅的鳍式场效应晶体管(finfet)在3nm以下节点受到限制,与主流后高介电常数金属栅鳍式场效应晶体管工艺兼容的纳米环栅晶体管(gaafet)将是实现尺寸微缩的下一代关键结构。纳米环栅晶体管(gaafet)中的内侧墙(inner spacer)的结构、形貌与材料对器件与电路的性能有重要影响。内侧墙有效隔离源漏与栅极,并获得最佳的综合性能(包括有效驱动电流,有效寄生电容等)。

2、然而,现有技术中,内侧墙的结构有待进一步改善。

技术实现思路

1、本发明解决的技术问题是,提出一种半导体结构及其形成方法,对内侧墙结构进行回刻蚀处理,增大沟道层与源漏外延层的接触面积,降低源漏外延层错位生长的产生,提升载流子迁移率,提升半导体器件性能。

2、为解决上述技术问题,本发明实施例提供一种半导体结构的形成方法,包括:提供衬底;在所述衬底表面形成初始沟道结构,所述初始沟道结构包括若干层重叠的初始沟道层以及位于相邻两层所述初始沟道层之间的牺牲层;形成横跨所述初始沟道结构的伪栅极结构,所述伪栅极结构位于所述初始沟道结构的部分侧壁表面和顶部表面;在所述伪栅极结构两侧的初始沟道结构内形成源漏开口,所述初始沟道层形成沟道层,所述源漏开口暴露出所述沟道层侧壁和所述牺牲层侧壁;对所述源漏开口暴露出的所述牺牲层进行回刻蚀,使所述牺牲层侧壁相对于所述源漏开口暴露出的沟道层侧壁凹陷,在相邻两层沟道层之间形成隔离凹槽;在所述隔离凹槽内形成隔离层,所述隔离层表面相对于所述源漏开口暴露出的沟道层侧壁凹陷;在形成所述隔离层之后,在所述源漏开口内形成源漏掺杂层。

3、可选的,还包括:在形成所述源漏掺杂层之后,在所述源漏掺杂层上形成第一介质层;在形成所述第一介质层之后,去除所述伪栅极结构,形成栅极开口;在去除所述伪栅极结构后,去除所述牺牲层,形成栅极沟槽;在所述栅极开口和所述栅极沟槽内形成栅极结构。

4、可选的,所述伪栅极结构包括伪栅氧化层和位于所述伪栅氧化层表面的伪栅层;所述伪栅层的材料包括多晶硅。

5、可选的,所述初始沟道结构的形成方法包括:提供初始衬底,在所述初始衬底表面形成初始复合层,所述初始复合层包括若干层重叠的沟道材料层以及位于相邻两层所述沟道材料层之间的牺牲材料层;在所述初始复合层表面形成第一掩膜层;以所述第一掩膜层为掩膜,对所述初始复合层和所述初始衬底进行多重图形化处理,形成衬底以及位于所述衬底表面的初始沟道结构。

6、可选的,在形成所述伪栅极结构之后,在形成所述源漏开口之前,还包括:在所述伪栅极结构侧壁形成侧墙。

7、可选的,所述隔离层的形成方法包括:在所述衬底表面、所述隔离凹槽内、所述侧墙表面以及所述伪栅极结构顶部表面形成隔离材料层;对所述隔离材料层进行刻蚀处理直至所述隔离材料层的侧壁齐平于所述沟道层的侧壁,形成初始隔离层;对所述初始隔离层进行回刻蚀,直至所述初始隔离层表面相对于所述源漏开口暴露出的沟道层侧壁凹陷,形成所述隔离层。

8、可选的,所述回刻蚀的方法包括:各向异性干法刻蚀、各向同性干法刻蚀或湿法刻蚀中一种或多种的组合。

9、可选的,所述干法刻蚀的刻蚀气体包括:氟基气体或氯基气体中一种或多种的组合。

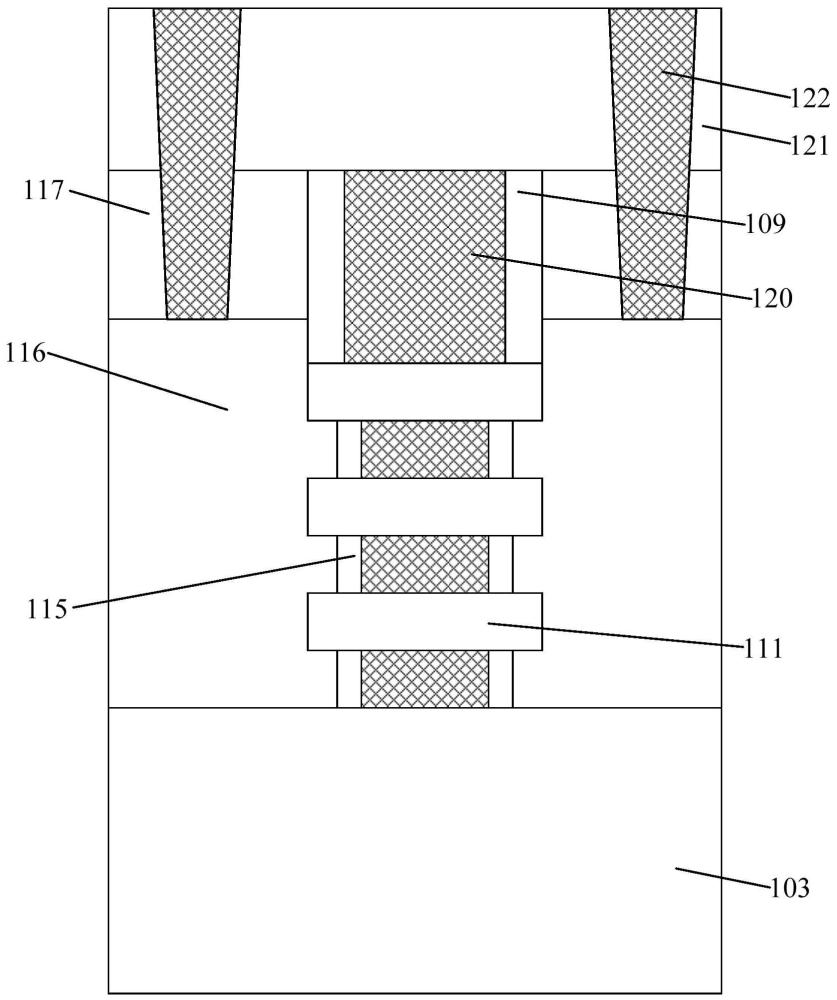

10、可选的,所述回刻蚀的刻蚀深度范围为:1nm~25nm。

11、可选的,所述隔离层的厚度范围为:1nm~30nm。

12、可选的,所述衬底包括基底以及位于所述基底上的底部结构,所述初始沟道结构位于所述底部结构上;在所述基底上形成隔离结构。

13、可选的,在形成所述栅极结构之后,在所述栅极结构表面形成第二介质层;在所述第二介质层内形成导电插塞。

14、可选的,当所述沟道层的导电类型为p型时,所述源漏掺杂层的材料为硅锗;当所述沟道层的导电类型为n型时,所述源漏掺杂层的材料为硅。

15、相应的,本发明实施例提供一种半导体结构,包括:衬底;位于所述衬底表面的沟道结构,所述沟道结构包括若干层重叠的沟道层,相邻沟道层之间具有栅极沟槽;横跨于所述沟道结构侧壁和顶部表面的栅极结构,且所述栅极结构包括位于所述栅极沟槽内的第一结构;位于所述栅极结构两侧的沟道结构内的源漏开口,所述源漏开口暴露出的沟道层侧壁相对于所述第一结构侧壁突出;位于所述第一结构侧壁表面的隔离层,所述隔离层表面相对于所述源漏开口暴露出的沟道层侧壁凹陷;位于所述源漏开口内的源漏掺杂层。

16、可选的,所述第一结构侧壁到源漏开口暴露出的沟道层侧壁的距离范围为:1nm~30nm。

17、可选的,所述隔离层的厚度范围为:1nm~30nm。

18、可选的,所述隔离层表面到源漏开口暴露出的沟道层侧壁的距离范围为:1nm~25nm。

19、可选的,所述隔离层的材料包括:氮化硅、氧化硅、硅碳氮、碳氧氮硅、碳氧化硅以及氮氧化硅。

20、可选的,所述栅极结构包括:栅介质层、位于所述栅介质层表面的高介电材料层、位于所述高介电材料层上的势垒层以及位于所述势垒层表面的功函数层。

21、可选的,还包括:位于所述源漏掺杂层表面的介质层;位于所述介质层内的导电插塞;所述导电插塞的材料包括钨。

22、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

23、本发明技术方案的半导体结构中,所述隔离层表面相对于所述源漏开口暴露出的沟道层侧壁凹陷,增大了所述沟道层暴露出的表面积,使得所述源漏掺杂层与所述沟道层的接触面积增大,降低了源漏掺杂层错位生长的产生,提升了半导体器件性能。

24、本发明技术方案的半导体结构的形成方法中,所述隔离层表面相对于所述源漏开口暴露出的沟道层侧壁凹陷,增大了所述沟道层暴露出的表面积,从而增大了源漏掺杂层与所述沟道层的接触面积,降低了源漏掺杂层错位生长的产生,提升了半导体器件性能。

技术特征:

1.一种半导体结构,其特征在于,包括:

2.如权利要求1所述的半导体结构,其特征在于,所述第一结构侧壁到源漏开口暴露出的沟道层侧壁的距离范围为:1nm~30nm。

3.如权利要求1所述的半导体结构,其特征在于,所述隔离层的厚度范围为:1nm~30nm。

4.如权利要求1所述的半导体结构,其特征在于,所述隔离层表面到源漏开口暴露出的沟道层侧壁的距离范围为:1nm~25nm。

5.如权利要求1所述的半导体结构,其特征在于,所述隔离层的材料包括:氮化硅、氧化硅、硅碳氮、碳氧氮硅、碳氧化硅以及氮氧化硅。

6.如权利要求1所述的半导体结构,其特征在于,所述栅极结构包括:栅介质层、位于所述栅介质层表面的高介电材料层、位于所述高介电材料层上的势垒层以及位于所述势垒层表面的功函数层。

7.如权利要求1所述的半导体结构,其特征在于,还包括:位于所述源漏掺杂层表面的介质层;位于所述介质层内的导电插塞;所述导电插塞的材料包括钨。

8.一种半导体结构的形成方法,其特征在于,包括:

9.如权利要求8所述的半导体结构的形成方法,其特征在于,还包括:在形成所述源漏掺杂层之后,在所述源漏掺杂层上形成第一介质层;在形成所述第一介质层之后,去除所述伪栅极结构,形成栅极开口;在去除所述伪栅极结构后,去除所述牺牲层,形成栅极沟槽;在所述栅极开口和所述栅极沟槽内形成栅极结构。

10.如权利要求8所述的半导体结构的形成方法,其特征在于,所述伪栅极结构包括伪栅氧化层和位于所述伪栅氧化层表面的伪栅层;所述伪栅层的材料包括多晶硅。

11.如权利要求8所述的半导体结构的形成方法,其特征在于,所述初始沟道结构的形成方法包括:提供初始衬底,在所述初始衬底表面形成初始复合层,所述初始复合层包括若干层重叠的沟道材料层以及位于相邻两层所述沟道材料层之间的牺牲材料层;在所述初始复合层表面形成第一掩膜层;以所述第一掩膜层为掩膜,对所述初始复合层和所述初始衬底进行多重图形化处理,形成衬底以及位于所述衬底表面的初始沟道结构。

12.如权利要求8所述的半导体结构的形成方法,其特征在于,在形成所述伪栅极结构之后,在形成所述源漏开口之前,还包括:在所述伪栅极结构侧壁形成侧墙。

13.如权利要求12所述的半导体结构的形成方法,其特征在于,所述隔离层的形成方法包括:在所述衬底表面、所述隔离凹槽内、所述侧墙表面以及所述伪栅极结构顶部表面形成隔离材料层;对所述隔离材料层进行刻蚀处理直至所述隔离材料层的侧壁齐平于所述沟道层的侧壁,形成初始隔离层;对所述初始隔离层进行回刻蚀,直至所述初始隔离层表面相对于所述源漏开口暴露出的沟道层侧壁凹陷,形成所述隔离层。

14.如权利要求13所述的半导体结构的形成方法,其特征在于,所述回刻蚀的方法包括:各向异性干法刻蚀、各向同性干法刻蚀或湿法刻蚀中一种或多种的组合。

15.如权利要求14所述的半导体结构的形成方法,其特征在于,所述干法刻蚀的刻蚀气体包括:氟基气体或氯基气体中一种或多种的组合。

16.如权利要求13所述的半导体结构的形成方法,其特征在于,所述回刻蚀的刻蚀深度范围为:1nm~25nm。

17.如权利要求8所述的半导体结构的形成方法,其特征在于,所述隔离层的厚度范围为:1nm~30nm。

18.如权利要求8所述的半导体结构的形成方法,其特征在于,所述衬底包括基底以及位于所述基底上的底部结构,所述初始沟道结构位于所述底部结构上;在所述基底上形成隔离结构。

19.如权利要求9所述的半导体结构的形成方法,其特征在于,在形成所述栅极结构之后,在所述栅极结构表面形成第二介质层;在所述第二介质层内形成导电插塞。

20.如权利要求8所述的半导体结构的形成方法,其特征在于,当所述沟道层的导电类型为p型时,所述源漏掺杂层的材料为硅锗;当所述沟道层的导电类型为n型时,所述源漏掺杂层的材料为硅。

技术总结

一种半导体结构及其形成方法,方法包括:在衬底表面形成初始沟道结构,包括若干层重叠的初始沟道层以及位于相邻两层初始沟道层之间的牺牲层;形成横跨初始沟道结构的伪栅极结构;在伪栅极结构两侧的初始沟道结构内形成源漏开口,初始沟道层形成沟道层,源漏开口暴露出沟道层侧壁和牺牲层侧壁;对源漏开口暴露出的牺牲层回刻蚀,使牺牲层侧壁相对于源漏开口暴露出的沟道层侧壁凹陷,在相邻两层沟道层之间形成隔离凹槽;在隔离凹槽内形成隔离层,隔离层表面相对于源漏开口暴露出的沟道层侧壁凹陷;在源漏开口内形成源漏掺杂层。隔离层表面相对于源漏开口暴露出的沟道层侧壁凹陷,增大沟道层暴露的面积,降低源漏掺杂层错位生长产生,提升器件性能。

技术研发人员:殷华湘,曹磊,李庆坤,张青竹

受保护的技术使用者:中国科学院微电子研究所

技术研发日:

技术公布日:2024/4/17

- 还没有人留言评论。精彩留言会获得点赞!