一种芯片封装结构的制作方法

本技术涉及半导体封装,特别涉及一种芯片封装结构。

背景技术:

1、针对存在高频信号、内置天线以及复杂外围电路的芯片项目,一般会采用基板封装方案,基板的标准制程一般没有挖槽工艺,而基板板材的隔离性能又偏弱,很难实现性能符合标准要求的电气隔离;另外,基板上均匀铺地会直接影响芯片的隔离性能,但不均匀铺地又会导致基板翘曲的问题,给封装带来了工艺可行性风险和封装可靠性风险。因此,传统的基板封装方案很难满足既有复杂电路设计需求,又有隔离耐压要求的芯片封装需求。

2、目前的隔离器件,为了能够实现符合标准要求的隔离性能,一般采用框架+wirebonding的传统封装方案。该方案通过在芯片和基板之间添加隔离层来实现电气隔离,从而保证信号的稳定性和可靠性。但是,由于wire bonding连接方式存在一定的电阻和感抗,所以在高频信号传输过程中,会产生较大的能量损耗和信号失真问题,导致信号质量下降。同时,复杂外围电路的结构也会使得隔离层难以布置,从而进一步限制了传统封装方案的应用范围。该方案无法满足高频信号和内置天线等设计要求。

技术实现思路

1、本实用新型所要解决的技术问题是:提供一种芯片封装结构。

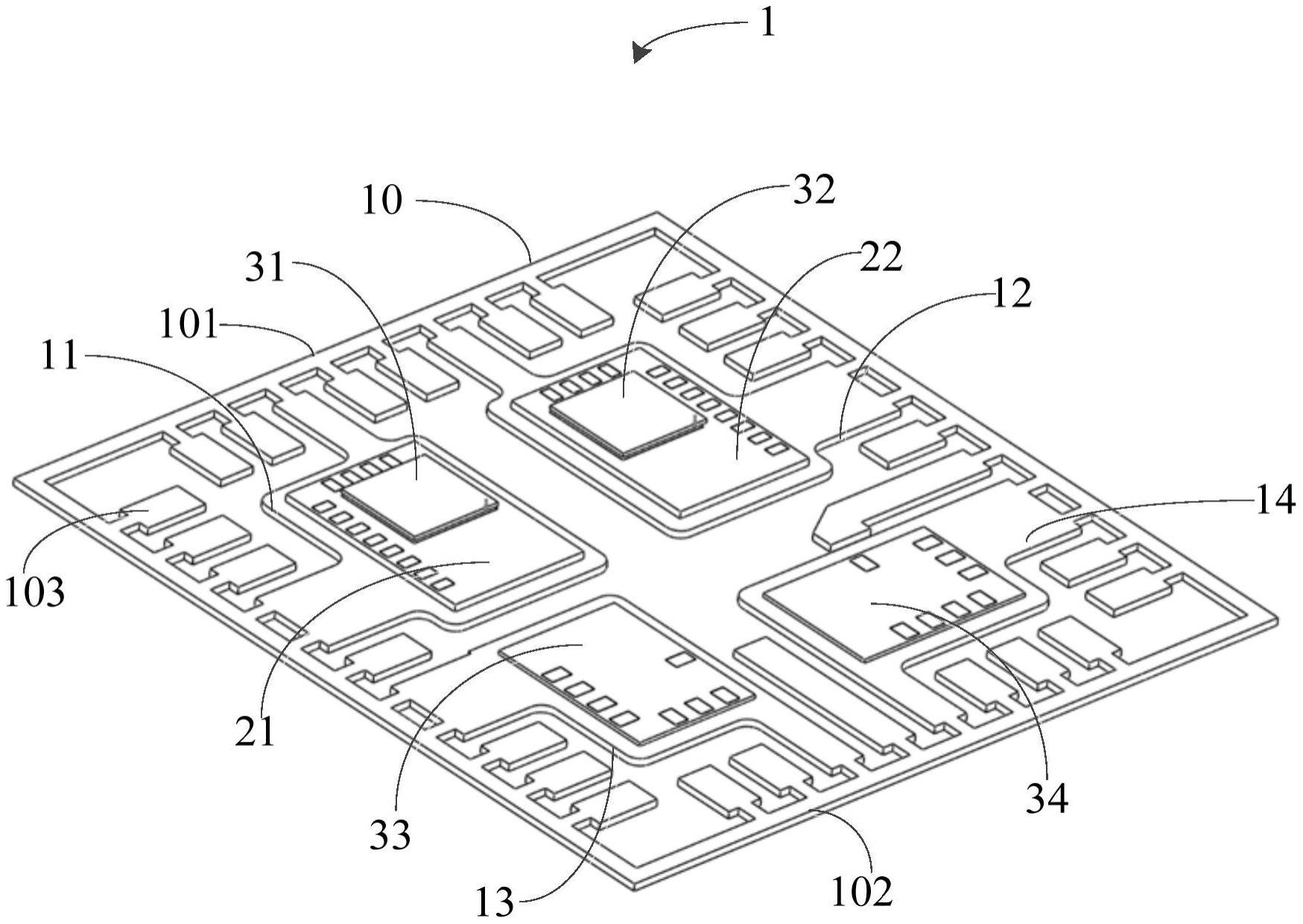

2、为解决上述技术问题,本实用新型采用的一个技术方案是:一种芯片封装结构,包括:隔离框架、第一基岛、第二基岛、第三基岛、第四基岛、第一基板、第二基板、第一芯片、第二芯片、第三芯片、第四芯片;所述隔离框架的侧边框内侧分布若干个框架焊盘;所述第一基岛、第二基岛、第三基岛以及第四基岛,矩阵分布在所述隔离框架形成的封闭区域内,且彼此不连接,并通过与对应的框架焊盘焊接,从而与所述隔离框架焊接;所述第一基板设置在所述第一基岛上,并通过第一焊线与对应的框架焊盘连接;所述第一芯片倒装设置在所述第一基板上;所述第二基板设置在所述第二基岛上,并通过第二焊线与对应的框架焊盘连接;所述第二芯片倒装设置在所述第二基板上;所述第三芯片正装设置在所述第三基岛上,并通过第三焊线与对应的框架焊盘连接;所述第四芯片正装设置在所述第四基岛上,并通过第四焊线与对应的框架焊盘连接;所述塑封体,设置在所述隔离框架形成的空间内部,包裹所述第一芯片、第二芯片、第三芯片、第四芯片以及若干个框架焊盘。

3、其中,所述框架焊盘的一端与所述隔离框架固定连接,另一端为悬空自由端;所述第一基岛、第二基岛、第三基岛以及第四基岛均通过对应的框架焊盘的自由端焊接,从而与所述隔离框架焊接。

4、其中,所述第一基岛、第二基岛并排设置在所述隔离框架形成的封闭区域内,且均与所述隔离框架的第一侧边框相邻;所述第三基岛、第四基岛并排设置在所述隔离框架形成的封闭区域内,且均与所述隔离框架的第二侧边框相邻;其中,所述隔离框架的第一侧边框和第二侧边框为相对的两条边框。

5、其中,所述第一基板上还设置若干个第一基板焊盘,用于通过第一焊线与对应的框架焊盘焊接;所述第二基板上还设置若干个第二基板焊盘,用于通过第二焊线与对应的框架焊盘焊接。

6、其中,沿着所述隔离框架内侧边缘,且远离所述框架焊盘自由端的位置,设置切筋线,用于在完成芯片封装的封装体上,沿着所述切筋线,通过切筋工艺切割出单独的倒装芯片封装体和正装芯片封装体。

7、其中,所述第一基板、第二基板上,集成天线、高频走线和复杂外围电路。

8、其中,所述第三芯片、第四芯片均为低速信号及电源电路。

9、本实用新型的有益效果在于:本实用新型提供的芯片封装结构,通过在设置第一基板的第一基岛上倒装设置第一芯片,在设置第二基板的第二基岛上倒装设置第二芯片,在第三基岛上正装设置第三芯片以及在第四基岛上正装设置第四芯片,从而将正装芯片、倒装芯片进行物理隔离;进一步地,通过塑封、切筋等传统封装工序,实现上述各个基岛隔离框架单元的完全电气隔离。利用本实用新型,对于电路简单或信号要求较低的晶片采用直接wire bonding的方式连接可以降低封装成本,又可以满足产品天线、高频信号以及复杂外围走线设计的要求,实现增强型隔离器件要求的完全电气隔离性能;进一步地,封装体内分布的用于放置基板和芯片的基岛、以及基板和芯片等主要部件的数量,没有限制,可以根据电路设计进行修改,使本实用新型的封装体具备了良好的扩展性。

技术特征:

1.一种芯片封装结构,其特征在于,包括:隔离框架、第一基岛、第二基岛、第三基岛、第四基岛、第一基板、第二基板、第一芯片、第二芯片、第三芯片、第四芯片以及塑封体;

2.根据权利要求1所述的一种芯片封装结构,其特征在于,所述框架焊盘的一端与所述隔离框架固定连接,另一端为悬空自由端;所述第一基岛、第二基岛、第三基岛以及第四基岛均通过对应的框架焊盘的自由端焊接,从而与所述隔离框架焊接。

3.根据权利要求1所述的一种芯片封装结构,其特征在于,所述第一基岛、第二基岛并排设置在所述隔离框架形成的封闭区域内,且均与所述隔离框架的第一侧边框相邻;所述第三基岛、第四基岛并排设置在所述隔离框架形成的封闭区域内,且均与所述隔离框架的第二侧边框相邻;其中,所述隔离框架的第一侧边框和第二侧边框为相对的两条边框。

4.根据权利要求1所述的一种芯片封装结构,其特征在于,所述第一基板上还设置若干个第一基板焊盘,用于通过第一焊线与对应的框架焊盘焊接;

5.根据权利要求2所述的一种芯片封装结构,其特征在于,沿着所述隔离框架内侧边缘,且远离所述框架焊盘自由端的位置,设置切筋线,用于在完成芯片封装的封装体上,沿着所述切筋线,通过切筋工艺切割出单独的倒装芯片封装体和正装芯片封装体。

6.根据权利要求1所述的一种芯片封装结构,其特征在于,所述第一基板、第二基板上,集成天线、高频走线和复杂外围电路。

7.根据权利要求1所述的一种芯片封装结构,其特征在于,所述第三芯片、第四芯片均为低速信号及电源电路。

技术总结

本技术公开了一种芯片封装结构,包括:隔离框架,第一、二三、四基岛,第一、二基板,第一、二、三、四芯片;第一、二、三、四基岛矩阵分布在隔离框架形成的封闭区域内且彼此不连接,并通过设置在隔离框架侧边框内侧的若干个框架焊盘与隔离框架焊接;第一、二基板分别设置在第一、二基岛上,并通过第一、二焊线与框架焊盘连接;第一、二芯片分别倒装设置在第一、二基板上;第三、四芯片分别正装设置在第三、四基岛上,并通过第三、四焊线与框架焊盘连接;塑封体设置在隔离框架形成的空间内部,包裹所述第一、二、三、四芯片及若干个框架焊盘。本技术通过在独立的基岛上设置倒装、正装芯片,并通过塑封、切筋实现完全电气隔离。

技术研发人员:李成,张亚运

受保护的技术使用者:德氪微电子(深圳)有限公司

技术研发日:20230613

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!