半导体器件及其形成方法与流程

本发明涉及半导体,尤其涉及一种半导体器件及其形成方法。

背景技术:

1、射频前端模块通常包括功率放大器(power amplifier,简称pa)、低噪声放大器(low noise amplifier,简称lna)、开关(switch)以及滤波器(filter)。功率放大器通常包括异质结双极型晶体管(hetero-junction bipolar transistor,hbt),异质结双极型晶体管(hetero-junction bipolar transistor,简称hbt)是由发射区(emitter)、基区(base)和集电区(collect)组成的晶体管,发射区采用轻掺杂的宽带隙,基区采用重掺杂的窄带隙,发射效率由禁带能差决定,主要功能为电流增益,如增益集电区电流或增益基区电流,异质结双极型晶体管器件有性能稳定、高速度及高频率等特点。异质结双极型晶体管技术已成为射频集成电路市场的主流技术之一,并对现代通信技术的发展产生了深远的影响。

2、目前的异质结双极型晶体管主要为砷化镓器件,然而在异质结双极型晶体管的工作过程中,砷化镓的散热效果较差,进而影响异质结双极型晶体管的性能。

技术实现思路

1、本发明解决的技术问题是提供一种半导体器件及其形成方法,以改善晶体管器件的性能以及提高集成度。

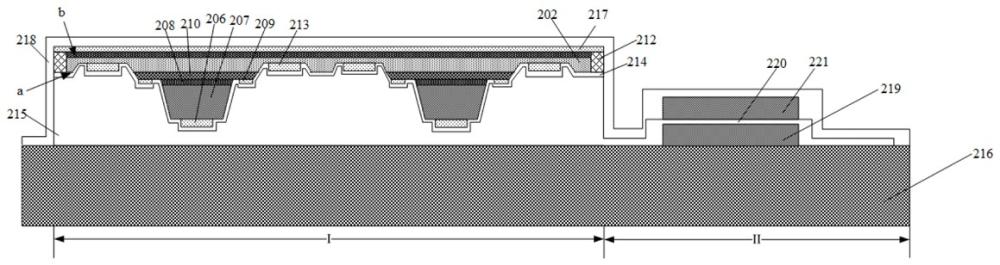

2、为解决上述技术问题,本发明实施例提供一种半导体器件,包括:第一衬底,所述第一衬底包括有源区;接合于所述有源区表面的晶体管器件,所述晶体管器件包括:发射层、基层和集电层,所述发射层包括相对的第一侧和第二侧,所述基层位于所述第一侧,所述集电层位于所述第一侧,所述基层位于所述集电层与所述发射层之间,所述第一衬底位于所述第一侧,所述第一衬底与所述发射层位于所述基层和所述集电层两侧,所述发射层、所述基层和集电层在所述第一衬底上的投影面积沿第二侧至第一侧的方向递减。

3、可选的,所述第一衬底的导热系数大于所述集电层、所述基层以及所述发射层的导热系数。

4、可选的,所述第一衬底的材料包括硅、碳化硅、氮化镓。

5、可选的,所述发射层的材料包括砷化铟镓;所述基层的材料包括砷化镓或砷化铟镓;所述集电层的材料包括砷化镓或铝镓砷。

6、可选的,所述晶体管器件还包括:位于发射层第二侧的第一阻挡层。

7、可选的,所述第一阻挡层的材料包括本征态的磷化铟镓。

8、可选的,还包括:位于所述晶体管器件与所述第一衬底之间的第一介质层,所述第一介质层覆盖所述晶体管器件,且所述晶体管器件通过所述第一介质层与所述第一衬底相接合。

9、可选的,还包括:位于集电层表面的第一接触层;位于基层表面的第二接触层,所述第二接触层与所述集电层相互分立;位于发射层表面的第三接触层。

10、可选的,所述发射层的表面具有凹槽,所述凹槽位于所述第一侧,第三接触层位于所述凹槽内。

11、可选的,所述发射层内具有隔离区,所述隔离区内具有掺杂离子,或,所述隔离区是通过对所述发射层进行刻蚀处理形成的隔离开口。

12、可选的,还包括:贯穿所述第一衬底的若干导电插塞结构,所述导电插塞结构分别与所述集电层、基层和发射层电连接。

13、可选的,还包括:贯穿所述第一衬底的第一导电插塞,所述第一导电插塞与所述集电层电连接;第二导电插塞,所述第二导电插塞与所述基层电连接,所述第二导电插塞与所述第一导电插塞位于所述集电层的两侧;第三导电插塞,所述第三导电插塞与所述发射层电连接,所述第三导电插塞与所述第一导电插塞位于所述集电层的两侧。

14、相应的,本发明技术方案还提供一种半导体器件的形成方法,包括:提供第一衬底,所述第一衬底包括有源区;提供第二衬底;在所述第二衬底表面形成若干晶体管器件,所述晶体管器件包括发射层、基层和集电层,所述发射层位于所述第二衬底上,所述发射层包括相对的第一侧和第二侧,所述第二衬底位于所述第二侧,所述基层和所述集电层位于所述第一侧,所述基层位于所述集电层与所述发射层之间;使所述发射层的第一侧面向所述第一衬底表面,将所述第一衬底和所述晶体管器件进行接合,所述第一衬底位于所述第一侧,所述第一衬底与所述发射层位于所述基层和所述集电层两侧,所述发射层、所述基层和集电层在所述第一衬底上的投影面积沿第二侧至第一侧的方向递减;将所述第一衬底和所述晶体管器件进行接合之后,去除所述第二衬底。

15、可选的,所述第一衬底的导热系数大于所述第二衬底的导热系数;所述第一衬底的材料包括硅、碳化硅或氮化镓;所述第二衬底的材料包括砷化镓。

16、可选的,所述晶体管器件的形成方法包括:在第二衬底上形成发射层;在所述发射层的第一侧形成初始基层;在所述初始基层上形成初始集电层;对所述初始集电层进行刻蚀,暴露出部分所述初始基层表面,形成集电层;对所述初始基层进行刻蚀,暴露出部分发射层表面,形成基层。

17、可选的,还包括:形成第一介质层,所述第一介质层覆盖所述晶体管器件,且所述第一介质层用于与所述第一衬底相接合。

18、可选的,还包括:对所述发射层进行掺杂处理或刻蚀处理,在所述发射层内形成隔离区。

19、可选的,所述晶体管器件的形成方法还包括:在所述第二衬底和发射层之间形成第一阻挡层。

20、可选的,所述第二衬底的刻蚀速率与所述第一阻挡层的刻蚀速率之比的范围为:10:1至20:1。

21、可选的,所述晶体管器件的形成方法还包括:在所述集电层与所述基层之间形成第二阻挡层,所述第二阻挡层暴露出部分所述基层表面。

22、可选的,还包括:在所述集电层的表面形成第一接触层;在所述基层的表面形成第二接触层;在所述发射层的表面形成第三接触层。

23、可选的,形成所述第三接触层的方法包括:对所述发射层暴露出的部分表面进行刻蚀,形成凹槽;在所述凹槽内形成所述第三接触层。

24、可选的,还包括:形成贯穿所述第一衬底的若干导电插塞结构,且所述导电插塞结构分别与所述集电层、基层和发射层电连接。

25、可选的,还包括:形成贯穿于所述第一衬底的第一导电插塞,所述第一导电插塞与所述集电层电连接;形成第二导电插塞,所述第二导电插塞与所述基层电连接,所述第二导电插塞与所述第一导电插塞位于所述集电层的两侧;形成第三导电插塞,所述第三导电插塞与所述发射层电连接,所述第三导电插塞与所述第一导电插塞位于所述集电层的两侧。

26、与现有技术相比,本发明实施例的技术方案具有以下有益效果:

27、本发明技术方案提供的半导体器件中,所述晶体管器件接合至第一衬底上,发射层位于顶层,发射层、基层和集电层的面积递减,通过减小集电层的面积以减小基极-集电极电容cbc,进而提高了晶体管的截止频率ft与最大振荡频率fm,提高了晶体管的高频性能。此外,晶体管器件面向第一衬底接合,集电层靠近第一衬底,进一步提升晶体管器件的散热效果以及工作性能。

28、进一步,本发明技术方案中,第一衬底为导热系数高的材料,使得晶体管器件在工作过程中的散热效果提升,进而提升晶体管器件的性能,且晶体管器件能够与低噪声放大器、开关以及滤波器一起制成在第一衬底上,进而提高了射频集成电路的集成度。

29、进一步,本发明技术方案中,所述第一阻挡层位于所述发射层表面,以保护所述晶体管器件在工艺形成过程中不被损坏,进而保证晶体管器件结构的器件完整性;且所述第一阻挡层的材料的晶格与所述晶体管器件的材料的晶格相匹配,因此在所述第一阻挡层上能够生长形成所述晶体管器件的外延层,提高形成所述晶体管器件的质量。

30、进一步,本发明技术方案中,所述导电插塞结构的材料包括铝和铜,降低了工艺材料成本,且铝和铜不易扩散至第一衬底,保证了第一衬底的散热性能,进而保证了晶体管器件结构的散热性能以及工作性能。

31、进一步,本发明技术方案,通过将所述第三接触层设置在发射层的凹槽中,使得所述第三接触层能够接触到所述发射层掺杂浓度较高的区域,避免与空间电荷区的接触,保证了所述晶体管器件的工作性能。

32、进一步,本发明技术方案中,发射层位于器件顶层,且所述发射层的厚度小于所述集电层的厚度,相较于集电层在器件顶层,本方案中在发射层中形成的凹槽的深度小,即需要预留的尺寸更小,进而减小了所述晶体管器件在平行于第一衬底表面方向的尺寸,提高所述晶体管器件的集成度。

33、本发明技术方案提供的晶体管器件的形成方法中,在第二衬底上形成晶体管器件时,发射层位于底层,将晶体管器件接合至第一衬底上后,发射层位于顶层,发射层、基层和集电层的面积递减,通过减小集电层的面积以减小基极-集电极电容cbc,进而提高了晶体管的截止频率ft与最大振荡频率fm,提高了晶体管的高频性能。此外,晶体管器件面向第一衬底接合,集电层靠近第一衬底,进一步提升晶体管器件的散热效果以及工作性能;在第二衬底上形成晶体管器件后再将晶体管器件转移到第一衬底上,提高了晶体管器件的制备工艺的可操作性,避免了第一衬底的尺寸与第二衬底尺寸不匹配,导致接合转移后用于形成晶体管器件的外延层的边缘超出第一衬底,而无法对位于第一衬底上的外延层进行刻蚀作业形成晶体管器件的问题,增加了工艺的选择,适用于不同尺寸的衬底之间的晶体管器件转移,适用范围广。

34、进一步,本发明技术方案,第二衬底的材料包括砷化镓,因此第二衬底的材料与所述晶体管器件的材料的晶格匹配,即在第二衬底上易生长形成晶体管器件,形成的晶体管器件性能好且不易脱落。

35、进一步,本发明技术方案中的第一衬底为导热系数高的材料,使得晶体管器件在工作过程中的散热效果提升,进而提升晶体管器件结构的性能,且第一衬底的材料包括硅,即晶体管器件位于所述硅衬底上,因此能够与低噪声放大器、开关以及滤波器一起制成在第一衬底上,进而提高了射频集成电路的集成度。

36、进一步,本发明技术方案中,在所述第二衬底表面形成所述第一阻挡层,且第一阻挡层的刻蚀速率小于所述第二衬底的刻蚀速率,使得在刻蚀去除第二衬底时刻蚀停止于第一阻挡层,保护与其相邻的发射层,以保护所述晶体管器件不被损坏,进而保证晶体管器件的性能;且所述第一阻挡层的材料的晶格与所述晶体管器件的材料的晶格相匹配,因此在所述第一阻挡层上能够生长形成所述晶体管器件的外延层,避免外延层与第二衬底之间的脱落,提高所述晶体管器件的质量。

37、进一步,本发明技术方案,通过在发射层中形成所述凹槽,使得后续形成的第三接触层能够接触到所述发射层掺杂浓度较高的区域,避免与空间电荷区的接触,保证了所述晶体管器件的工作性能。

38、进一步,本发明技术方案中,在将所述第一衬底和所述晶体管器件进行接合之前,发射层位于基层和集电层的底部,且发射层的厚度小于所述集电层,相较于集电层位于基层和发射层的底部,本方案中在发射层中形成的凹槽的深度小,即需要预留的尺寸更小,进而减小了所述晶体管器件在平行于第一衬底表面方向的尺寸,提高所述晶体管器件的集成度。

39、进一步,本发明技术方案中,所述导电插塞结构的材料包括铝和铜,降低了工艺材料成本,且铝和铜不易扩散至第一衬底,保证了第一衬底的散热性能,进而保证了晶体管器件的散热性能以及工作性能。

- 还没有人留言评论。精彩留言会获得点赞!