半导体器件的制作方法

本申请涉及把半导体,特别是涉及一种非均匀sic sj-jbsfet器件。

背景技术:

1、作为一种用于功率器件的半导体材料,4h-sic引起了人们的极大兴趣与在相同额定电压下设计的硅基器件相比,sic的高电击穿强度使其漂移层大大变薄,从而使其具有更高的优点。然而,sic的宽带隙和更大的pn结内置电位也导致mosfet寄生体二极管的较高的接入电压。si mosfet的典型体二极管插入电压仅为0.7v,而sic mosfet的典型体二极管插入电压接近3v。当mosfet在死区关闭时,高插入电压会产生更大的功率损失。mosfet寄生体二极管的接通过程中还会遇到少数载流子的注入,这会增加反向恢复电流、时间和开关功率损失。

技术实现思路

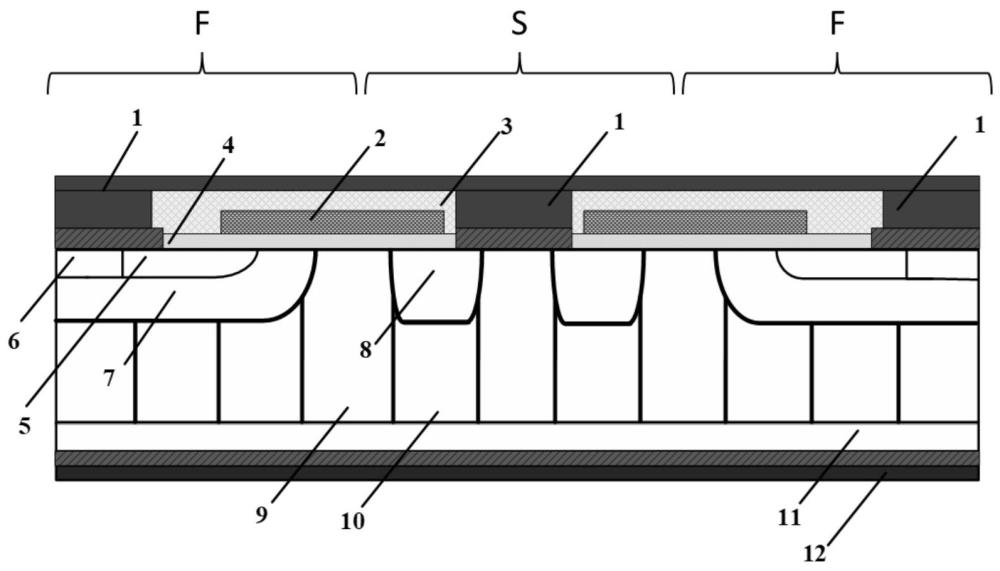

1、为了解决上述问题,本申请公开了一种半导体器件。所述半导体器件可以包括:底面漏极结构;漂移区,其设置在所述底面漏极结构之上;以及表面结构,其设置在所述漂移区之上;其中,所述漂移区包括水平方向上依次交替设置的第一掺杂柱层和第二掺杂柱层,且所述漂移区在水平方向上被划分为位于两端的两个第一区域以及位于中部的第二区域;所述第一区域内设置有第一掺杂区、第二掺杂区和第三掺杂区;所述第一掺杂区与所述第二掺杂区在水平方向上相接触,所述第三掺杂区位于所述第一掺杂区与所述第二掺杂区的下方,且在垂直方向上与所述第一掺杂区与所述第二掺杂区相接触;所述第二区域内设置有第四掺杂区,所述第四掺杂区位于所述第二掺杂柱层上且与所述第一掺杂柱层相接触。

2、根据本申请的一些实施例,所述底面漏极结构包括漏极以及层叠于漏极之上的n型碳化硅衬底。

3、根据本申请的一些实施例,所述第三掺杂区的一端向外延伸并与所述第一掺杂区的一端在水平方向上相接触。

4、根据本申请的一些实施例,所述表面结构包括复数个互连的源极金属电极以及多晶硅栅极,所述源极金属电极以及所述多晶硅栅极之间通过层间介质层进行隔离。

5、根据本申请的一些实施例,所述第一掺杂区包括n型源区,所述第二掺杂区包括p型源区,所述第三掺杂区包括p型基区;位于所述第一区域上方的源极金属电极与所述n型源区和所述p型源区接触形成欧姆接触。

6、根据本申请的一些实施例,所述第三掺杂区浓度掺杂浓度低于第二掺杂区。

7、根据本申请的一些实施例,所述多晶硅栅极通过栅氧化层与所述漂移区隔离。

8、根据本申请的一些实施例,所述第一掺杂柱层包括n型掺杂柱层,所述第二掺杂柱层包括p型掺杂柱层,所述n型掺杂柱层和所述p型掺杂柱层交替设置构成超结结构。

9、根据本申请的一些实施例,所述第四掺杂区包括深p注入区;位于所述第二区域上方的源极金属电极与所述深p注入区接触形成欧姆接触,与所述第一掺杂柱层接触形成肖特基接触。

10、根据本申请的一些实施例,所述第四掺杂区的掺杂浓度大于所述第二掺杂柱层的掺杂浓度。

11、本申请所披露的半导体器件,可以是一种新型非均匀sic sj-jbsfet器件,相比于传统的sic mosfet,在jfet区集成了一个jbs二极管,降低了反向导通损耗和反向恢复时间,提高了器件的性能。深p+注入区的位置置于多晶硅栅极之下,减小了反向传输电容的大小,即进一步减小器件的开关损耗,也提高了器件的可靠性。同时,因为集成jbs二极管带来的元胞面积增大的负面影响,通过设计非均匀的超结(sj)结构,降低了器件的漂移区电阻,进而减小了器件整体导通电阻。非均匀的依次交替设置的第一掺杂柱n-层和第二掺杂柱p-层,保证了器件的正常导通特性,不影响器件的可靠性。

技术特征:

1.一种半导体器件,其特征在于,所述半导体器件包括:

2.根据权利要求1所述的半导体器件,其特征在于,所述底面漏极结构包括漏极以及层叠于漏极之上的n型碳化硅衬底。

3.根据权利要求1所述的半导体器件,其特征在于,所述第三掺杂区的一端向外延伸并与所述第一掺杂区的一端在水平方向上相接触。

4.根据权利要求1所述的半导体器件,其特征在于,所述表面结构包括复数个互连的源极金属电极以及多晶硅栅极,所述源极金属电极以及所述多晶硅栅极之间通过层间介质层进行隔离。

5.根据权利要求4所述的半导体器件,其特征在于,所述第一掺杂区包括n型源区,所述第二掺杂区包括p型源区,所述第三掺杂区包括p型基区;位于所述第一区域上方的源极金属电极与所述n型源区和所述p型源区接触形成欧姆接触。

6.根据权利要求5所述的半导体器件,其特征在于,所述第三掺杂区浓度掺杂浓度低于第二掺杂区。

7.根据权利要求4所述的半导体器件,其特征在于,所述多晶硅栅极通过栅氧化层与所述漂移区隔离。

8.根据权利要求4所述的半导体器件,其特征在于,所述第一掺杂柱层包括n型掺杂柱层,所述第二掺杂柱层包括p型掺杂柱层,所述n型掺杂柱层和所述p型掺杂柱层交替设置构成超结结构。

9.根据权利要求8所述的半导体器件,其特征在于,所述第四掺杂区包括深p注入区;位于所述第二区域上方的源极金属电极与所述深p注入区接触形成欧姆接触,与所述第一掺杂柱层接触形成肖特基接触。

10.根据权利要求9所述的半导体器件,其特征在于,所述第四掺杂区的掺杂浓度大于所述第二掺杂柱层的掺杂浓度。

技术总结

本申请公开一种半导体器件。所述半导体器件包括:底面漏极结构;漂移区,其设置在所述底面漏极结构之上;以及表面结构,其设置在所述漂移区之上;其中,所述漂移区包括水平方向上依次交替设置的第一掺杂柱层和第二掺杂柱层,且所述漂移区在水平方向上被划分为位于两端的两个第一区域以及位于中部的第二区域;所述第一区域内设置有第一掺杂区、第二掺杂区和第三掺杂区;所述第一掺杂区与所述第二掺杂区在水平方向上相接触,所述第三掺杂区位于所述第一掺杂区与所述第二掺杂区的下方,且在垂直方向上与所述第一掺杂区与所述第二掺杂区相接触;所述第二区域内设置有第四掺杂区,所述第四掺杂区位于所述第二掺杂柱层上且与所述第一掺杂柱层相接触。

技术研发人员:夏玉山

受保护的技术使用者:希科半导体科技(苏州)有限公司

技术研发日:

技术公布日:2024/3/4

- 还没有人留言评论。精彩留言会获得点赞!