一种背接触电池及其制造方法与流程

本发明涉及光伏,尤其涉及一种背接触电池及其制造方法。

背景技术:

1、背接触电池是指电池片的向光面无电极,正、负电极均设置在电池片背光面一侧的太阳能电池,从而可以减少电极对电池片的遮挡,增加电池片的短路电流,提高电池片的能量转化效率。

2、但是,现有的背接触电池中背光面一侧的光线利用率降低,不利于提升背接触电池的光电转换效率。

技术实现思路

1、本发明的目的在于提供一种背接触电池及其制造方法,用于增大背接触电池中背光面一侧的光线利用率,利于提升背接触电池的光电转换效率。

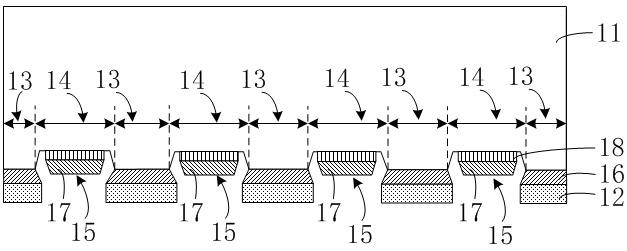

2、为了实现上述目的,第一方面,本发明提供了一种背接触电池,该背接触电池包括:硅基底、以及形成在硅基底背光面一侧的部分区域上的第一掺杂半导体层。其中,硅基底的背光面中与第一掺杂半导体层对应的区域为第一区域,其余区域为第二区域。第一区域和第二区域交替分布。第二区域上形成有相对于第一区域的表面向硅基底内凹入的凹槽结构。第一掺杂半导体层与第二区域相邻的端部悬空设置。

3、采用上述技术方案的情况下,在本发明提供的背接触电池处于工作状态下,光线沿向光面至背光面的方向,由向光面一侧折射至硅基底内。硅基底在吸收了光子能量后可以产生电子和空穴。并且,电子和空穴分别朝向第一掺杂半导体层和部分第二区域的方向运动,最终被相应电极导出,形成光电流。而上述进入至硅基底内的光线,并非完全能够被硅基底吸收利用,存在部分光线由硅基底的背光面一侧折射出去。在此情况下,位于硅基底背光面一侧的第一掺杂半导体层,其与第二区域相邻的端部悬空设置。此时,由硅基底的背光面一侧折射出去的部分光线可以在第一掺杂半导体层与第二区域相邻、且悬空设置的端部的反射作用下重新回到硅基底内并被硅基底吸收利用,从而可以增大背接触电池对光线的利用率,利于提升背接触电池的光电转换效率。

4、另外,本发明提供的背接触电池中,硅基底的背光面具有的第二区域上形成有相对于第一区域的表面向硅基底内凹入的凹槽结构,使得第一区域的表面和第二区域的表面能够沿硅基底的厚度错开,利于将共同位于硅基底背光面一侧、且导电类型相反的第一掺杂半导体层与位于第二区域内的相应掺杂区(或形成在第二区域上的第二掺杂半导体层)沿硅基底厚度方向至少部分错开,降低背光面一侧的漏电风险,提高背接触电池的电学可靠性。

5、作为一种可能的实现方案,上述凹槽结构的深度大于等于200nm、且小于等于2500nm。

6、采用上述技术方案的情况下,在实际的制造过程中,在硅基底背光面一侧的第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构后,可以使得第一掺杂半导体层与第二区域相邻的端部悬空设置。基于此,凹槽结构的深度在上述范围内,可以防止因深度较小使得第一掺杂半导体层与第二区域相邻的端部对应的悬设高度较小而导致该端部对光线的反射作用较弱,利于使得更多的光线可以在第一掺杂半导体层与第二区域相邻的端部的反射作用下重新回到硅基底内,确保背接触电池具有较高的光线利用率;还可以防止该凹槽较小而导致共同位于硅基底背光面一侧、且导电类型相反的第一掺杂半导体层与位于第二区域内的相应掺杂区(或形成在第二区域上的第二掺杂半导体层)沿硅基底厚度方向错开的程度较小,进一步降低背光面一侧的漏电风险。另外,还可以防止因凹槽结构的深度较大使得第一掺杂半导体层的端部在受到刻蚀硅基底的刻蚀液的影响而导致端部悬设在第二区域上的长度变小,确保更多的光线可以在第一掺杂半导体层与第二区域相邻、且长度相对较大的端部的反射作用下重新回到硅基底内;还可以防止因上述凹槽结构深度较大而需要使用厚度较大的硅基底,从而可以降低背接触电池的制造成本的同时,利于实现背接触电池的薄片化生产。

7、作为一种可能的实现方案,沿第一区域和第二区域的排布方向,第一掺杂半导体层中悬空设置的端部的长度大于0、且小于等于3000nm。

8、采用上述技术方案的情况下,可以理解的是,第一掺杂半导体层中悬空设置的端部越长,其在第二区域上的覆盖长度越大。而背接触电池的背光面一侧设置有导电类型相反的两个掺杂区,因此沿第一区域和第二区域的排布方向,第一掺杂半导体层中悬空设置的端部的长度在上述范围内,可以防止因第一掺杂半导体层中悬空设置的端部长度较大使得第一掺杂半导体层与位于第二区域内的相应掺杂区(或形成在第二区域上的第二掺杂半导体层)的间距较小而容易导致漏电,确保背接触电池具有较高的电学可靠性。另外,当第一掺杂半导体层中悬空设置的端部的长度大于0、且小于等于3000nm时,该悬空设置的端部的长度具有较大的可选范围,利于降低制造具有固定长度值的第一掺杂半导体层的难度,同时还可以提高本发明提供的背接触电池在不同应用场景下的适用性。

9、作为一种可能的实现方案,上述凹槽结构的侧壁中至少部分表面相对于水平面倾斜设置,以使凹槽结构的至少部分区域的横截面积沿向光面至背光面的方向逐渐增大。在此情况下,凹槽结构的槽底面积小于槽口面积,利于沿第一区域和第二区域的排布方向,增大第一掺杂半导体层与自身导电类型相反、且位于第二区域内的相应掺杂区(或形成在第二区域上的第二掺杂半导体层)的间距,降低背接触电池背光面一侧的漏电风险,确保背接触电池具有较高的电学可靠性。另外,凹槽结构的侧壁中与平面倾斜设置的部分也利于对光线进行反射,进一步降低光线由背接触电池的背光面一侧折射出去的概率,进而利于提高背接触电池的光电转换效率。

10、作为一种可能的实现方案,上述凹槽结构的侧壁中,靠近槽口的部分表面与水平面垂直设置。在此情况下,为本发明提供的背接触电池中,凹槽结构的形貌提供了另一种可能的实现方案,利于提高本发明提供的背接触电池在不同应用场景下的适用性。

11、作为一种可能的实现方案,上述凹槽结构的侧壁中相对于水平面倾斜设置的部分与水平面之间的夹角大于等于52°、且小于等于58°。

12、采用上述技术方案的情况下,凹槽结构的侧壁中相对于水平面倾斜设置的部分与水平面之间的夹角在上述范围内,可以防止该夹角较大或较小使得凹槽结构的侧壁中相对于水平面倾斜设置的部分将光线反射回硅基底内的作用较弱,确保更多光线更够在凹槽结构的侧壁中相对于水平面倾斜设置的部分的较大反射作用下重新回到硅基底内并被硅基底重新利用,进一步提高背接触电池对光线的利用率。

13、作为一种可能的实现方案,上述凹槽结构的侧壁中,靠近槽口的部分表面与靠近槽底的部分表面之间具有与水平面平行设置的平面。在此情况下,可以使得凹槽结构的侧壁中具有至少与水平面相对设置角度不同的两种表面,利于凹槽结构的侧壁中不同部分对光线进行不同角度的反射,进而利于使得更多的光线可以在凹槽结构的侧壁的反射作用下回到硅基底内并被硅基底重新利用。

14、作为一种可能的实现方案,沿第一区域和第二区域的排布方向,凹槽结构的侧壁中与水平面平行设置的平面的长度大于0、且小于2μm。

15、采用上述技术方案的情况下,在一定范围内,沿第一区域和第二区域的排布方向,凹槽结构的侧壁中与水平面平行设置的平面的长度与凹槽结构对应的刻蚀时间成正比。基于此,凹槽结构的侧壁中与水平面平行设置的平面的长度在上述范围内,可以防止该长度较大而导致凹槽结构对应的刻蚀时间较长,确保凹槽结构形成后第一掺杂半导体层与第二区域相邻且悬空设置的端部具有一定的长度,

16、作为一种可能的实现方案,沿第一区域和第二区域的排布方向,凹槽结构的侧壁中与水平面平行设置的平面和凹槽结构的槽口的最小距离大于0、且小于1μm。在此情况下,可以防止凹槽结构的侧壁中与水平面平行设置的平面和凹槽结构的槽口沿第一区域和第二区域的排布方向的间距较大而导致该平面与第一掺杂半导体层中悬空设置的端部之间的反射配合效果较差,确保有更多的光线可以在该平面与悬空设置的端部的共同作用下反射回硅基底内,进一步提高背接触电池的光效利用率。

17、作为一种可能的实现方案,上述凹槽结构的槽底的至少部分表面为绒面。在此情况下,因绒面具有凹凸不平的表面特征,因此当凹槽结构的槽底的全部表面为绒面时,可以增大形成在凹槽结构槽底的相应掺杂区(或第二掺杂半导体层)的表面积,进而增大相应掺杂区(或第二掺杂半导体层)与电极的接触面积,降低接触电阻,利于提高背接触电池的光电转换效率。另外,凹槽结构的槽底暴露在层叠设置的第二钝化层和第二掺杂半导体层之外的部分表面为绒面时,可以使得该部分表面具有一定的陷光效果,使得更多光线由凹槽结构的槽底透射至硅基底内。同时,第二钝化层形成在槽底的平面部分上,可以提高第二钝化层对该部分表面的钝化效果,提高背接触电池的光电转换效率。

18、作为一种可能的实现方案,上述背接触电池还包括位于硅基底具有的第一区域和第一掺杂半导体层之间的第一钝化层。

19、采用上述技术方案的情况下,第一钝化层和第一掺杂半导体层可以构成选择性接触结构,以实现对硅基底背光面上相应区域进行化学钝化、且实现对相应导电类型的载流子的选择性收集,降低背光面一侧的载流子复合速率,利于提高背接触电池的光电转换效率。

20、作为一种可能的实现方案,上述背接触电池还包括形成在凹槽结构的槽底上的第二掺杂半导体层,第二掺杂半导体层的导电类型与第一掺杂半导体层的导电类型相反。

21、作为一种可能的实现方案,在背接触电池包括第一钝化层、且第一钝化层为隧穿钝化层的情况下,第一掺杂半导体层为掺杂多晶硅层。

22、作为一种可能的实现方案,在背接触电池包括第二掺杂半导体层的情况下,背接触电池还包括位于硅基底和第二掺杂半导体层之间的第二钝化层。

23、作为一种可能的实现方案,在背接触电池包括第二掺杂半导体层的情况下,沿第一区域和第二区域的排布方向,第一掺杂半导体层和第二掺杂半导体的间距大于等于20μm、且小于等于110μm。

24、采用上述技术方案的情况下,导电类型相反的第一掺杂半导体层和第二掺杂半导体层的间距在上述范围内,可以防止因上述间距较小而导致第一掺杂半导体层和第二掺杂半导体层之间产生漏电,确保背接触电池具有较高的电学可靠性。另外,还可以防止因上述间距较大而导致背光面一侧的载流子无法及时被第一掺杂半导体层和第二掺杂半导体层收集并被相应电极导出,进一步降低背光面一侧的载流子复合速率。

25、作为一种可能的实现方案,上述第二钝化层为隧穿钝化层,第二掺杂半导体层为掺杂多晶硅层。

26、第二方面,本发明还提供了一种背接触电池的制造方法,该背接触电池的制造方法包括:首先,提供一硅基底。接下来,在硅基底的背光面上形成整层设置的掺杂半导体材料层、以及位于部分掺杂半导体材料层上的掩膜层。接着,在掩膜层的掩膜作用下,选择性刻蚀掺杂半导体材料层,以使掺杂半导体材料层的剩余部分形成第一掺杂半导体层。硅基底的背光面中与第一掺杂半导体层对应的区域为第一区域,其余区域为第二区域。第一区域和第二区域交替分布。接下来,在掩膜层的掩膜作用下,在第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构,以及使第一掺杂半导体层与第二区域相邻的端部悬空设置。

27、作为一种可能的实现方案,上述第一掺杂半导体层的材料包括硅。并且,在硅基底上形成掺杂半导体材料层、以及位于部分掺杂半导体材料层上的掩膜层,包括:在硅基底的背光面上形成整层设置的本征半导体材料层。接着,对本征半导体材料层进行掺杂处理,以使本征半导体材料层形成掺杂半导体材料层,以及在掺杂半导体材料层上形成整层设置的掺杂硅玻璃层。然后,采用激光刻蚀工艺,对部分掺杂硅玻璃层进行热处理,以使掺杂硅玻璃层未经热处理的部分形成掩膜层。然后,去除掺杂硅玻璃层经热处理的部分。

28、采用上述技术方案的情况下,当第一掺杂半导体层的材料包括硅时,用于制造掺杂半导体材料层的本征半导体材料层的材料也包括硅。基于此,对本征半导体材料层进行掺杂处理后,不仅能够获得掺杂半导体材料层,还能够在掺杂半导体材料层上形成整层设置的掺杂硅玻璃层。然后,采用激光刻蚀工艺,对部分掺杂硅玻璃层进行热处理。此时,掺杂硅玻璃层内被激光处理的部分的致密性变差,其容易被去除。而掺杂硅玻璃层内未被激光处理的部分的致密性较高,其不容易被去除,从而在热处理后使得掺杂硅玻璃层不同部分具有不同的刻蚀选择比,获得对掺杂半导体材料层进行图案化处理的掩膜层,无须为了获得上述掩膜层而额外形成其它掩膜材料、以及形成其它掩膜沉积工序,利于降低背接触电池的制造成本,且简化背接触电池的制造流程。

29、作为一种可能的实现方案,采用湿化学工艺,并在掩膜层的掩膜作用下,在第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构。湿化学工艺的工艺温度大于等于65℃、且小于等于85℃,和/或,湿化学工艺的工艺时间大于等于50s、且小于等于500s。

30、采用上述技术方案的情况下,湿化学工艺的工艺温度和工艺时间均会影响通过湿化学工艺所形成的凹槽结构的规格、以及第一掺杂半导体层中悬空设置的端部的规格。基于此,湿化学工艺的工艺温度在上述范围内,可以防止因工艺温度较小而导致凹槽结构的深度、第一掺杂半导体层中悬空设置的端部的悬设高度和长度均较小。另外,还可以防止因工艺温度较大而导致凹槽结构的深度较大。其中,防止凹槽结构的深度、第一掺杂半导体层中悬空设置的端部的悬设高度和长度均较小,以及防止凹槽结构的深度较大的有益效果可以参考前文。其次,工艺时间在上述范围内的有益效果与工艺温度大于等于65℃、且小于等于85℃的有益效果相似,此处不再赘述。

31、作为一种可能的实现方案,提供一硅基底后,在硅基底的背光面上形成整层设置的掺杂半导体材料层、以及位于部分掺杂半导体材料层上的掩膜层前,背接触电池的制造方法还包括:在硅基底的背光面上形成整层设置的第一钝化材料层。并且,在掩膜层的掩膜作用下,选择性刻蚀掺杂半导体材料层后,在掩膜层的掩膜作用下,在第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构前,背接触电池的制造方法还包括:在掩膜层的掩膜作用下,选择性刻蚀第一钝化材料层,以使第一钝化材料层的剩余部分形成第一钝化层。

32、作为一种可能的实现方案,在掩膜层的掩膜作用下,在第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构的同时,对凹槽结构的槽底进行制绒处理,以使凹槽结构的槽底形成绒面。

33、作为一种可能的实现方案,在掩膜层的掩膜作用下,在第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构后,背接触电池的制造方法还包括:在凹槽结构的槽底形成第二掺杂半导体层。

34、作为一种可能的实现方案,在掩膜层的掩膜作用下,在第二区域上形成相对于第一区域的表面向硅基底内凹入的凹槽结构后,在凹槽结构的槽底形成第二掺杂半导体层前,背接触电池的制造方法还包括:在凹槽结构的槽底形成第二钝化层。

35、作为一种可能的实现方案,在掩膜层的掩膜作用下,在第二区域上形成的凹槽结构的槽底为平面。并且,在凹槽结构的槽底形成第二掺杂半导体层后,对凹槽结构的槽底暴露在第二掺杂半导体层之外的部分进行制绒处理。

36、本发明中第二方面及其各种实现方式中的有益效果,可以参考第一方面及其各种实现方式中的有益效果分析,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!