电容结构及电容结构的制作方法与流程

本发明属于半导体,具体涉及一种电容结构及电容结构的制作方法。

背景技术:

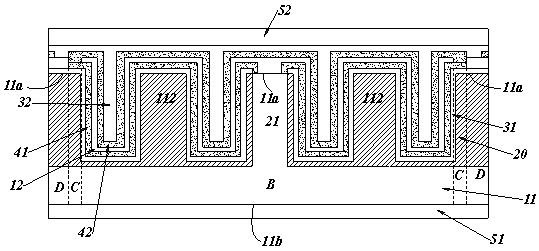

1、参考图1和图2所示,针对多层dtc(深沟槽)电容的异面电极引出,常规技术是通过在芯片边缘引出电极保护环a-seal ring。电极保护环a-seal ring的根本作用是界定出芯片区域且防止芯片在切割时造成机械损伤。通过电极保护环a-seal ring为中间媒介,将多晶硅层ps1与芯片衬底以及位于芯片背面的下电极m2连通。而芯片中心区域则直接引出n++层和多晶硅层ps2的电极至正面形成上电极m1,m1与电极保护环a-seal ring最终处于同一平面。其中,图1和图2中倾斜阴影处均为绝缘层。

2、为了在芯片正面的中心区域直接引出n++层和多晶硅层ps2,需要在多晶硅层ps1以及介质层d1和介质层d2上开设有多个通孔,而该设置则大大降低了作为电极层的多晶硅层ps1与多晶硅层ps2与介质层d1和介质层d2之间的接触面积,影响了电容密度。

3、而且,由于电极保护环a的存在,会导致有较大esr(等效串联电阻)和esl(等效串联电感);由于电极保护环a的存在,也会占据芯片正面的表面面积,牺牲部分的电容密度;且电极保护环a的设计在打线时很容易因为打线偏差造成对位不准,进而导致电极保护环a-seal ring和芯片正面电极的上电极m1短接,使得上电极m1和下电极m2连接短路而导致器件失效。

4、公开于该背景技术部分的信息仅仅旨在增加对本发明的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现思路

1、本发明的目的在于提供一种电容结构及电容结构的制作方法,其能够通过相邻介质层相连通的方式增加了介质层(第一介质层和第二介质层)和电极层(第一导电层和第三导电层、第二导电层和衬底)的接触面积,同时又避免了采用电极保护环的方式进行其中一个电极层的引出,大幅度的减小esr(等效串联电阻)和esl(等效串联电感),且不同的电极位于不同的表面,也不会造成后续打线时短路进而导致器件失效的问题。

2、为了实现上述目的,本发明一具体实施例提供的了一种电容结构,包括具有间隔设置的钝化区的衬底以及依次形成于所述衬底表面的第一导电层、第一介质层、第二导电层、第二介质层以及第三导电层,其中,所述第二导电层与所述衬底在相邻钝化区之间的非钝化区域内相连通以形成第一电极层,所述第一导电层与所述第三导电层相连通以形成第二电极层,所述第一介质层与所述第二介质层相连通且所述第一介质层与所述钝化区相接触以隔离所述第一电极层和所述第二电极层;所述衬底背离所述钝化区的表面形成有第一电极;所述第三导电层的表面形成有第二电极。

3、在本发明的一个或多个实施例中,所述衬底包括第一区域、第二区域以及第三区域,所述第二区域包围所述第一区域设置,所述第三区域包围所述第二区域设置;

4、相邻所述钝化区之间的非钝化区域位于所述第一区域内,所述第二导电层与所述衬底在所述第一区域内相连通设置,所述第一介质层与所述钝化区在所述第一区域内相接触设置;

5、所述第一介质层与所述第二介质层在所述第二区域内相连通设置;

6、所述第一导电层与所述第三导电层在所述第三区域内相连通设置。

7、在本发明的一个或多个实施例中,所述衬底具有相对设置的第一表面和第二表面,所述钝化区自第一表面向第二表面延伸,所述第一表面上于钝化区内形成有沟槽,所述沟槽中具有由部分衬底构成的若干分立的柱状结构。

8、在本发明的一个或多个实施例中,所述第一导电层、第一介质层、第二导电层、第二介质层以及第三导电层均覆盖或部分覆盖所述衬底的第一表面、所述沟槽的内壁以及所述柱状结构的外表面。

9、在本发明的一个或多个实施例中,所述第一导电层形成于所述衬底的第一表面、所述沟槽的内壁以及所述柱状结构的外表面上,所述第一导电层上开设有与所述非钝化区域对应的第一窗口,所述第一窗口暴露出所述非钝化区域的衬底以及部分所述钝化区的衬底。

10、在本发明的一个或多个实施例中,所述第一介质层形成于所述第一导电层的表面且于所述第一窗口处与所述钝化区相接触以隔离所述衬底和所述第一导电层,其中,所述第一窗口和所述非钝化区域仍暴露出部分所述非钝化区域的衬底;所述第一介质层上开设有第二窗口,所述第二窗口暴露出部分所述第一导电层。

11、在本发明的一个或多个实施例中,所述第二窗口位于所述衬底边缘的第一表面处,所述第二窗口内填充有与所述第一导电层连通的导电材料。

12、在本发明的一个或多个实施例中,所述第二导电层形成于所述第一介质层的表面以及形成于所述第一窗口以及所述非钝化区域内以与所述衬底相连通形成所述第一电极层,所述第二导电层上开设有第三窗口,所述第三窗口暴露出部分所述第一介质层。

13、在本发明的一个或多个实施例中,所述第三窗口位于所述衬底边缘的第一表面处,且被所述第二窗口包围设置。

14、在本发明的一个或多个实施例中,所述第二介质层形成于所述第二导电层的表面且于所述第三窗口处与所述第一介质层相连通以隔离所述第一导电层和所述第二导电层,所述第二介质层上开设有与所述第二窗口对应的第四窗口。

15、在本发明的一个或多个实施例中,所述第三导电层形成于所述第二介质层的表面以及形成于所述第四窗口内且通过所述第二窗口内的导电材料与所述第一导电层相连通以形成所述第二电极层。

16、在本发明的一个或多个实施例中,所述衬底为p型重掺杂衬底。

17、在本发明的一个或多个实施例中,所述钝化区为n型扩散区。

18、在本发明的一个或多个实施例中,所述第一导电层为n型重掺杂多晶硅层或ald沉积的tin。

19、在本发明的一个或多个实施例中,所述第一介质层为sin、sio2、ono或者high k材料。

20、在本发明的一个或多个实施例中,所述第二导电层为多晶硅层或ald沉积的tin。

21、在本发明的一个或多个实施例中,所述第二介质层为sin、sio2、ono或者high k材料。

22、在本发明的一个或多个实施例中,所述第三导电层为多晶硅层或ald沉积的tin。

23、本发明一具体实施例还提供的了一种电容结构的制作方法,包括:

24、提供衬底,所述衬底具有相对设置的第一表面和第二表面;

25、在所述衬底的第一表面形成间隔设置的钝化区,相邻所述钝化区之间具有暴露所述衬底的非钝化区域;

26、在所述第一表面的钝化区内形成沟槽,所述沟槽中具有由部分衬底构成的若干分立的柱状结构;

27、在所述衬底的第一表面、所述沟槽的内壁以及所述柱状结构的外表面上形成第一导电层,所述第一导电层于所述衬底的非钝化区域处暴露出部分所述衬底;

28、在所述第一导电层的表面形成第一介质层,所述第一介质层在所述非钝化区域与所述钝化区相接触,共同作用以隔离所述第一导电层和所述衬底;

29、在所述第一介质层的表面形成连通所述衬底的第二导电层;

30、在所述第二导电层的表面形成与所述第一介质层相连通的第二介质层,所述第二介质层和所述第一介质层共同作用以隔离所述第二导电层和所述第一导电层;

31、在所述第二介质层的表面形成与所述第一导电层相连通的第三导电层;

32、在所述衬底的第二表面上形成第一电极;

33、在所述第三导电层的表面形成第二电极。

34、在本发明的一个或多个实施例中,在所述第一导电层的表面形成与所述钝化区相接触的第一介质层,包括:

35、在所述第一导电层上开设与所述非钝化区域对应的第一窗口,所述第一窗口暴露出所述非钝化区域的衬底以及部分所述钝化区的衬底;

36、在所述第一导电层的表面形成第一介质层,所述第一介质层在所述第一窗口处与被暴露的所述钝化区相接触以隔离所述衬底和所述第一导电层。

37、在本发明的一个或多个实施例中,在所述第一介质层上开设第二窗口,所述第二窗口暴露出部分所述第一导电层;

38、在所述第一介质层的表面以及所述第一窗口内形成连通所述衬底的第二导电层。

39、在本发明的一个或多个实施例中,在所述第二导电层上开设第三窗口,所述第三窗口暴露出部分所述第一介质层;

40、在所述第二导电层的表面以及所述第三窗口内形成与所述第一介质层相连通的第二介质层,以隔离所述第一导电层和所述第二导电层。

41、在本发明的一个或多个实施例中,在所述第二介质层上开设有与所述第二窗口对应的第四窗口;

42、在所述第二介质层的表面以及所述第四窗口内形成第三导电层,所述第三导电层通过所述第二窗口内的导电材料与所述第一导电层相连通。

43、在本发明的一个或多个实施例中,所述非钝化区域位于所述衬底中部且被所述第二窗口和第三窗口包围设置;

44、所述第二窗口位于所述衬底边缘的第一表面处;

45、所述第三窗口位于所述衬底边缘的第一表面处,且被所述第二窗口包围设置。

46、与现有技术相比,本发明的电容结构及电容结构的制作方法,通过对第二导电层进行开孔,连通相邻的第一介质层和第二介质层,增加了介质层(第一介质层、第二介质层)和第一电极层(第二导电层和衬底)以及和第二电极层(第一导电层和第三导电层)之间的接触面积,提高了电容密度。

47、本发明的电容结构及电容结构的制作方法,仅将第一导电层与第三导电层引出作为第二电极层,第二导电层直接通过衬底引出形成第一电极层,避免采用了电极保护环的方式进行第一电极层的引出,有效增加了第二电极的面积,提高了电容密度。

48、本发明的电容结构及电容结构的制作方法,第一电极和第二电极分别形成在不同的表面,也不会造成后续打线时电极之间短路进而导致器件失效的问题。

49、本发明的电容结构及电容结构的制作方法,通过结构上的设计,优化了电流的流向路径,从而大幅度减小了esr(等效串联电阻)和esl(等效串联电感)。

- 还没有人留言评论。精彩留言会获得点赞!