扇出型封装结构和扇出型封装结构的制备方法与流程

本发明涉及半导体封装,具体而言,涉及一种扇出型封装结构和扇出型封装结构的制备方法。

背景技术:

1、现有技术中,bga焊球阵列封装(ball grid array package)封装结构广泛应用于半导体行业中。一般采用bga封装结构需要通过贴装散热盖实现散热,其要求散热盖满足散热,然而随着算力需求的提升需要多个芯片集成从而提升其算力,传统bga封装散热结构,采用倒装芯片贴装,受倒装芯片面积限制,从而导致其布输入/输出凸点限制。

2、进一步地,出现了采用扇出型封装技术进行芯片重构布线以及增加输入/输出凸点,提升其芯片性能,然而经发明人调研发现,传统单颗芯片进行扇出型封装结构,其芯片区域通常较芯片范围更大,需要占据一定的散热盖底部尺寸空间,无法实现排布更多的扇出型封装产品,集成度同样收到影响。此外,常规的多芯片封装结构则难以解决翘曲、散热的问题。

技术实现思路

1、本发明的目的包括,例如,提供了一种扇出型封装结构和扇出型封装结构的制备方法,其能够实现多芯片扇出封装,提升器件集成度,同时能够有效解决芯片之间布线层的翘曲问题,并提升了散热性能。

2、本发明的实施例可以这样实现:

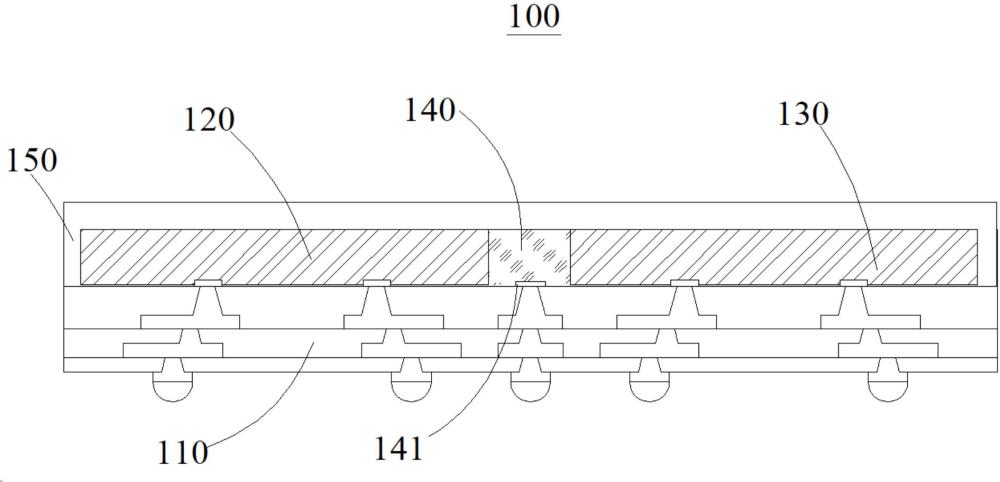

3、第一方面,本发明提供一种扇出型封装结构,包括:

4、扇出布线基底层;

5、至少一个第一芯片,所述第一芯片贴装在所述扇出布线基底层上;

6、至少一个第二芯片,所述第二芯片贴装在所述扇出布线基底层上,并与所述第一芯片并排间隔设置;

7、伪结构芯片,所述伪结构芯片贴装在所述扇出布线基底层上,且所述伪结构芯片设置在所述第一芯片和所述第二芯片的同一侧,并同时与所述第一芯片和所述第二芯片相间隔;

8、塑封体,所述塑封体设置在所述扇出布线基底层上,并包覆在所述第一芯片、所述第二芯片以及所述伪结构芯片外;

9、其中,第一芯片和所述第二芯片沿第一方向排布在所述扇出布线基底层上,所述扇出布线基底层同时与所述第一芯片和所述第二芯片电连接,所述伪结构芯片沿所述第一方向贴设在所述扇出布线基底层上,且所述伪结构芯片用于支撑所述扇出布线基底层,并对所述扇出布线基底层进行散热。

10、在可选的实施方式中,所述伪结构芯片的两端分别与所述第一芯片和所述第二芯片相背的两侧边缘相平齐。

11、在可选的实施方式中,所述伪结构芯片贴合在所述扇出布线基底层的一侧还设置有静电柱,所述静电柱延伸至所述扇出布线基底层,以消除所述扇出布线基底层上的静电并将所述扇出布线基底层的热量传导至所述伪结构芯片。

12、在可选的实施方式中,所述扇出型封装结构还包括基板和散热盖,所述扇出布线基底层远离所述塑封体的一侧设置在所述基板上,所述散热盖的中部贴合于所述塑封体远离所述扇出布线基底层的一侧,所述散热盖的边缘贴合于所述基板。

13、在可选的实施方式中, 所述塑封体远离所述扇出布线基底层的一侧设置有散热胶层,所述散热盖通过所述散热胶层贴合在所述塑封体的表面。

14、在可选的实施方式中,所述第一芯片和所述第二芯片相对于所述扇出布线基底层的高度小于或等于所述塑封体的厚度,以使所述塑封体包覆或露出所述第一芯片和所述第二芯片的表面。

15、在可选的实施方式中,所述塑封体完全贴合于所述散热盖,所述第一芯片、所述第二芯片以及所述伪结构芯片均设置于所述扇出布线基底层的芯片区域,且所述第一芯片、所述第二芯片以及所述伪结构芯片的边缘与所述芯片区域的边缘相重叠,所述芯片区域的面积sb为所述塑封体的顶侧面积sc的4/5-1。

16、在可选的实施方式中,所述塑封体的侧壁与所述扇出布线基底层的侧壁平齐,所述芯片区域的边缘与所述塑封体的侧壁之间的距离在10μm以上。

17、在可选的实施方式中,所述基板上还设置有被动元器件,所述散热盖罩设在所述被动元器件外。

18、第二方面,本发明提供一种扇出型封装结构的制备方法,用于制备如前述实施方式任一项所述的扇出型封装结构,所述制备方法包括:

19、沿重构晶圆区在载具上贴至少一个第一芯片、至少一个第二芯片和至少一个伪结构芯片;

20、在载具上塑封形成塑封体,该塑封体包覆在第一芯片、第二芯片和伪结构芯片外;

21、在所述塑封体的表面形成扇出布线基底层,其中所述扇出布线基底层内形成多个芯片区域,所述第一芯片、所述第二芯片以及所述伪结构芯片的边缘与所述芯片区域的边缘相重叠;

22、沿切割道切割所述扇出布线基底层和所述塑封体,形成芯片模块。

23、在可选的实施方式中,所述扇出布线基底层包括多个相互接合的扇出区域,所述芯片区域位于所述扇出区域内,且所述切割道位于所述扇出区域并与所述芯片区域相间隔,且所述切割道围设形成一布线区域,所述布线区域的边缘位于所述芯片区域的边缘和所述扇出区域的边缘之间。

24、在可选的实施方式中,所述扇出区域的面积sa为所述芯片区域的面积sb的5/4-5倍。

25、在可选的实施方式中,所述芯片区域的面积sb为所述布线区域的面积sc的4/5-1倍。

26、在可选的实施方式中,所述芯片区域的边缘与所述布线区域的边缘之间的距离在10μm以上。

27、在可选的实施方式中,相邻两个所述布线区域之间设置有两个切割道。

28、在可选的实施方式中,沿重构晶圆区在载具上贴第一芯片、第二芯片和伪结构芯片的步骤之后,所述制备方法还包括:

29、在所述重构晶圆区的边缘贴装应力伪芯片。

30、在可选的实施方式中,沿切割道切割所述扇出布线基底层和所述塑封体的步骤之后,所述制备方法还包括:

31、在基板上贴装所述芯片模块,其中所述扇出布线基底层远离所述塑封体的一侧设置在所述基板上;

32、在所述塑封体远离所述扇出布线基底层的一侧贴合散热盖,所述散热盖的边缘贴合于所述基板。

33、在可选的实施方式中,在沿切割道切割所述扇出布线基底层和所述塑封体的步骤之前,所述制备方法还包括:

34、研磨所述塑封体,以露出所述第一芯片、所述第二芯片和所述伪结构芯片的表面;

35、剥离所述载具。

36、本发明实施例的有益效果包括,例如:

37、本发明实施例提供的扇出型封装结构及其制备方法,首先利用扇出工艺,实现第一芯片、第二芯片以及伪结构芯片的贴装,使得第一芯片、第二芯片以及伪结构芯片均贴装在扇出布线基底层上,其中第一芯片和第二芯片沿第一方向并排间隔设置,且伪结构芯片位于第一芯片和第二芯片的同侧,并同时与第一芯片和第二芯片相间隔,然后利用塑封体实现包覆保护。通过设置伪结构芯片,且伪结构芯片沿第一方向贴设在扇出布线基底层上,一方面能够起到支撑扇出布线基底层的作用,提升器件的结构强度,压合扇出布线基底层以防止第一芯片和第二芯片下方的扇出布线基底层发生翘曲,另一方面伪结构芯片还能够对扇出布线基底层进行散热,提升器件的散热性能。

- 还没有人留言评论。精彩留言会获得点赞!