一种发光二极管的外延结构、制备方法及LED芯片与流程

本发明涉及半导体,特别涉及一种发光二极管的外延结构、制备方法及led芯片。

背景技术:

1、近年来发光二极管工艺在各大产商竞争下快速发展,被广泛的应用于通用照明、特种照明、直显显示屏、背光显示屏、车灯等各个领域。

2、现有技术当中,常规algainp发光二极管外延结构的多量子阱层发出的光在出射时,从未蒸镀电极区域出射的光线,相当一部分的光线会被吸收,而从蒸镀电极区域出射的光线,绝大一部分会被吸收,使得器件的光提取效率大幅下降,led器件亮度不足,且此问题随着制备的芯片尺寸越小而变得愈发严重,同时伴随而来的还有器件电流横向扩展能力差,抗静电能力弱,电压高的问题。

技术实现思路

1、基于此,本发明的目的是提供一种发光二极管的外延结构、制备方法及led芯片,可以有效解决上述现有技术当中的不足。

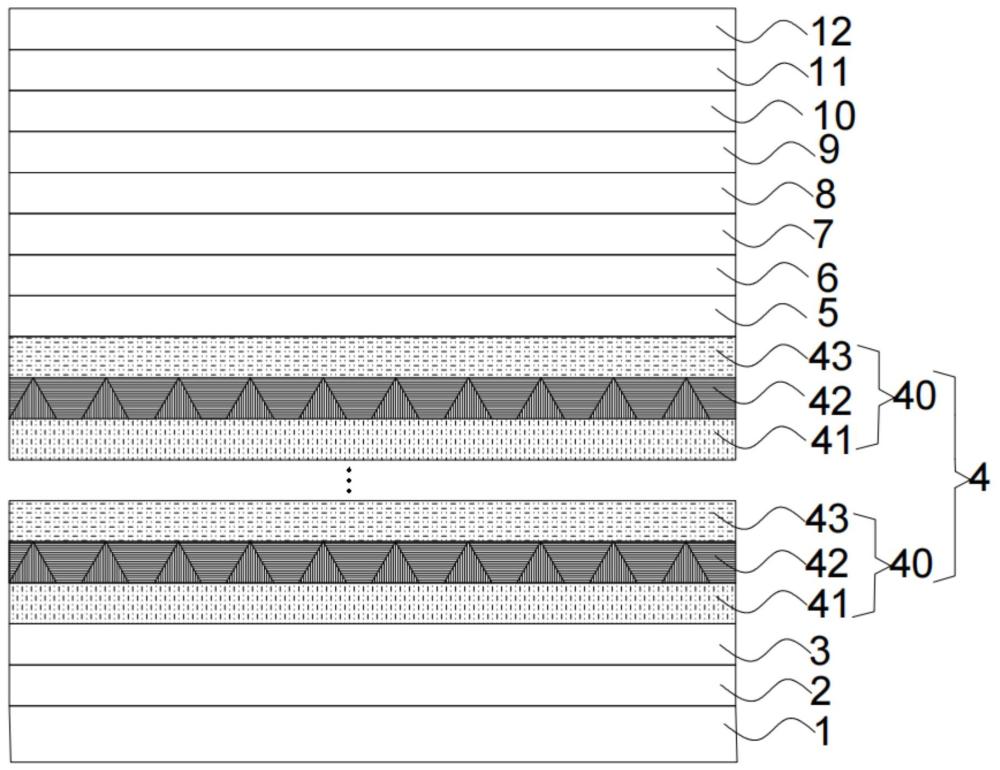

2、一种发光二极管的外延结构,包括:

3、过渡层;

4、所述过渡层包括n个周期性层叠设置的第一子层,所述第一子层包括依次层叠设置的二维alxgayinzp层、三维排列层以及二维alαgaβinγp层,所述三维排列层包括依次层叠设置的三维alxgayinzp层以及三维alαgaβinγp层;

5、所述三维alxgayinzp层为等间距排布的圆锥体或棱锥体;

6、所述二维alxgayinzp层以及所述三维alxgayinzp层的禁带宽度大于二维alαgaβinγp层以及三维alαgaβinγp层,所述二维alxgayinzp层以及所述三维alxgayinzp层的si掺杂浓度小于二维alαgaβinγp层、三维alαgaβinγp层。

7、与现有技术相比,本发明的有益效果是:通过将二维alxgayinzp层以及三维alxgayinzp层的禁带宽度大于二维alαgaβinγp层以及三维alαgaβinγp层设置,通过将二维alxgayinzp层以及三维alxgayinzp层的si掺杂浓度小于二维alαgaβinγp层以及三维alαgaβinγp层设置,进而提高了电子在二维alxgayinzp层的横向电流扩展能力以及在二维alxgayinzp层的纵向迁移率,使得三维alxgayinzp层可将二维alxgayinzp层的横向电流扩展细分至数量更多的横向电流,继而沿三维alαgaβinγp层纵向迁移至二维alαgaβinγp层,三者交替生长的结构可明显的提升器件的电流扩展能力,提升器件内电流分布的均匀性,提升器件的抗静电能力,降低工作电压,提升非电极区域下方的多量子阱层的发光效率;具有不同禁带宽度和si掺杂浓度的二维alxgayinzp层和二维alαgaβinγp层具有不相同的折射率,多量子阱层发出的光线从二维alxgayinzp层到三维排列层、三维排列层到二维alαgaβinγp层,光线在两两之间的交界面会发生折射,形成更加复杂的光路,提高出光效率,增大led芯粒的出光角度,以使相同光线覆盖面时所需的led芯粒的数量越少,提高利用率;具有不同禁带宽度和si掺杂浓度分布的三维alxgayinzp层和三维alαgaβinγp层,接触面间具有非平整粗糙弧面,光线沿三维排列层传播时,可形成更加复杂的光路,可获得更高的出光效率,提升器件的发光亮度。

8、进一步的,所述第一子层的周期n为2-6。

9、进一步的,所述等间距排布的圆锥体或棱锥体的间距为5nm-500nm。

10、进一步的,所述二维alxgayinzp层的厚度为5nm-60nm,所述二维alxgayinzp层的si掺杂浓度为1×1016atoms/cm3~1×1020atoms/cm3,所述二维alxgayinzp层的x、y以及z的取值范围为0≤x≤0.55,0≤y≤0.55,0.45≤z≤0.55。

11、进一步的,所述三维alxgayinzp层的厚度为5nm-50nm,所述三维alxgayinzp层的si掺杂浓度为1×1016atoms/cm3~1×1020atoms/cm3,所述三维alxgayinzp层的x、y以及z的取值范围为0≤x≤0.55,0≤y≤0.55,0.45≤z≤0.55。

12、进一步的,所述三维alαgaβinγp层的厚度为5nm-50nm,所述三维alαgaβinγp层的si掺杂浓度为1×1017atoms/cm3~1×1021atoms/cm3,所述三维alαgaβinγp层的α、β以及γ的取值范围为0≤α≤0.5,0≤β≤0.5,0.5≤γ≤0.6。

13、进一步的,所述二维alαgaβinγp层的厚度为5nm-60nm,所述二维alαgaβinγp层的si掺杂浓度为1×1017atoms/cm3~1×1021atoms/cm3,所述二维alαgaβinγp层的α、β以及γ的取值范围为0≤α≤0.5,0≤β≤0.5,0.5≤γ≤0.6。

14、另一方面,本发明还提出一种发光二极管的外延结构的制备方法,所述制备方法包括以下步骤:

15、s1、提供一衬底;

16、s2、在所述衬底上沉积缓冲层;

17、s3、在所述缓冲层上沉积截止层;

18、s4、在所述截止层上依次沉积n次二维alxgayinzp层、n次三维排列层以及n次二维alαgaβinγp层,得到n个周期性层叠设置的第一子层作为过渡层;

19、s5、在所述过渡层上沉积n型限制层;

20、s6、在所述n型限制层沉积上沉积n侧空间层;

21、s7、在所述n侧空间层上沉积多量子阱层;

22、s8、在所述多量子阱层上沉积p侧空间层;

23、s9、在所述p侧空间层上沉积p型限制层;

24、s10、在所述p型限制层上沉积p型过渡层;

25、s11、在所述p型过渡层上沉积p型窗口层;

26、s12、在所述p型窗口层上沉积反射层;

27、其中,所述过渡层包括n个周期性层叠设置的第一子层,所述第一子层包括依次层叠设置的二维alxgayinzp层、三维排列层以及二维alαgaβinγp层,所述三维排列层包括依次层叠设置的三维alxgayinzp层以及三维alαgaβinγp层;

28、所述三维alxgayinzp层为等间距排布的圆锥体或棱锥体;

29、所述二维alxgayinzp层以及所述三维alxgayinzp层的禁带宽度大于二维alαgaβinγp层以及三维alαgaβinγp层,所述二维alxgayinzp层以及所述三维alxgayinzp层的si掺杂浓度小于二维alαgaβinγp层、三维alαgaβinγp层。

30、进一步的,在所述s4中,沉积三维排列层的步骤包括:

31、在所述二维alxgayinzp层上生长所述三维alxgayinzp层;

32、对完成生长的所述三维alxgayinzp层进行刻蚀,使得所述三维alxgayinzp层为等间距排布的圆锥体或棱锥体;

33、在所述三维alxgayinzp圆锥体或棱锥体的侧壁以及所述二维alxgayinzp层上同时生长所述三维alαgaβinγp层作为所述三维排列层。

34、再一方面,本发明还提出一种含有发光二极管的外延结构的led芯片,其包括上述的发光二极管的外延结构。

- 还没有人留言评论。精彩留言会获得点赞!