静电放电电路、输出级电路、运放、芯片及电子设备的制作方法

本公开的实施例涉及集成电路,具体地,涉及静电放电电路、输出级电路、运放、芯片及电子设备。

背景技术:

1、随着集成电路技术的发展,低压工艺经常被应用在集成电路中。由于电路尺寸及功耗的减少,低工作电压可以使集成电路的成本降低。然而在一些集成电路中,由于电源电压高于低压工艺所能承受的最大电压,因此这些集成电路不能使用低压工艺来实现。因为一旦施加到采用低压工艺实现的集成电路上的电压过高则会导致该集成电路中的一个或多个元器件暂时甚至永久性的损坏,从而造成该集成电路不能正常工作。

技术实现思路

1、本文中描述的实施例提供了一种输出级电路、运算放大器、芯片及电子设备。

2、根据本公开的第一方面,提供了一种静电放电电路,用于对输出级电路的输出端进行静电保护。静电放电电路包括:第一静电释放电路和第二静电释放电路。其中,第一静电释放电路与第二静电释放电路串联连接在地电压端与输出端之间。其中,第一静电释放电路与第二静电释放电路的连接点耦接输出级电路中的固定电压端以使得第一静电释放电路和第二静电释放电路的承压均低于或者等于输出级电路的电源电压的一半。

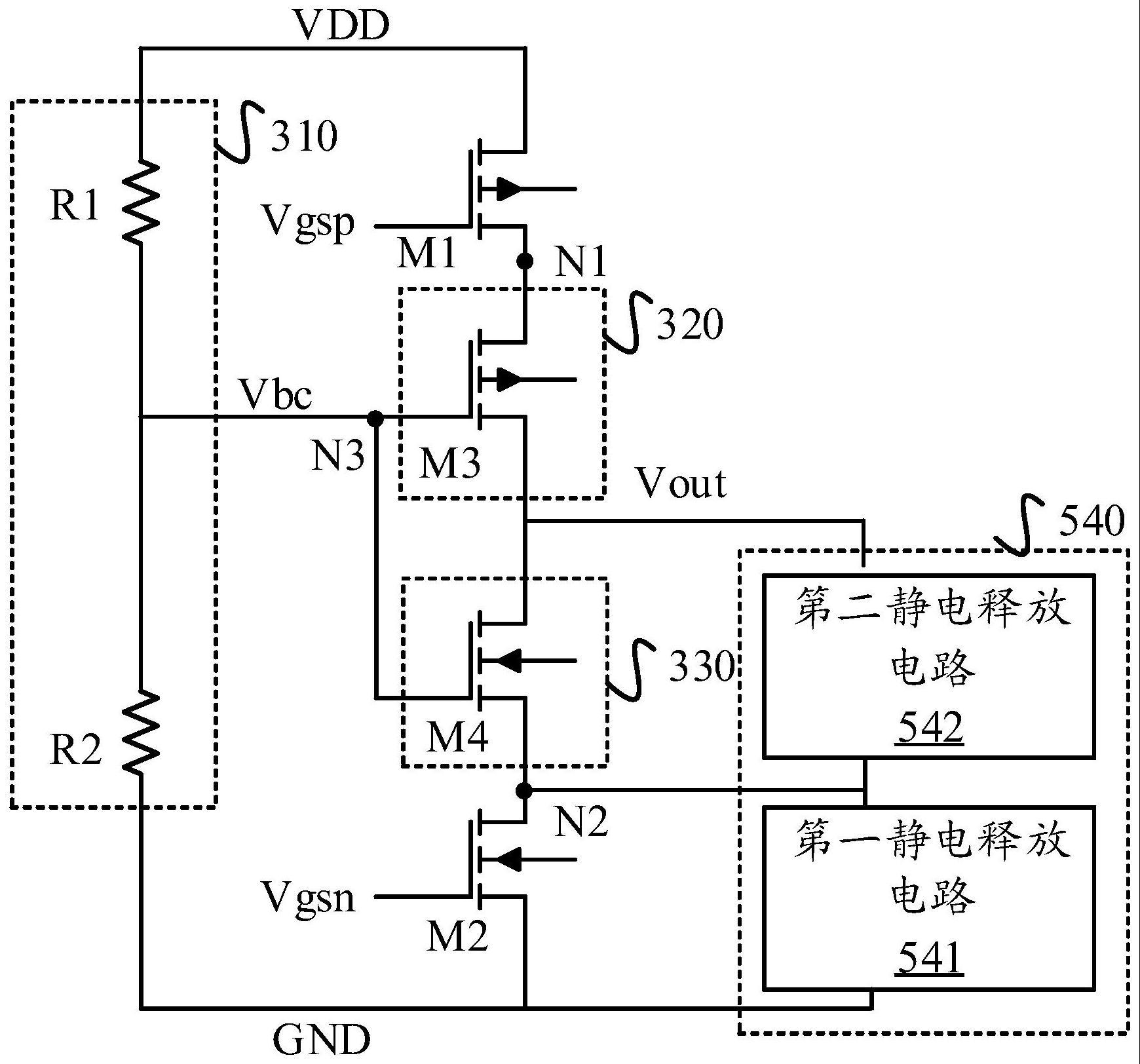

3、在本公开的一些实施例中,输出级电路包括:第一晶体管、第二晶体管、分压电路、第一承压电路、以及第二承压电路。其中,第一晶体管的控制极耦接其上一级的输出级控制电路的第一输出端。第一晶体管的第一极耦接电源电压端。第一晶体管的第二极耦接第一节点。第二晶体管的控制极耦接输出级控制电路的第二输出端。第二晶体管的第一极接地。第二晶体管的第二极耦接第二节点。分压电路被配置为:对来自电源电压端的电源电压进行分压以生成分压电压,并经由第三节点向第一承压电路和第二承压电路提供分压电压。第一承压电路被布置在第一节点与输出端之间,并被配置为:根据分压电压来控制第一节点的电压,以使得第一晶体管的第一极与第二极之间的电压差低于或者等于电源电压的一半。第二承压电路被布置在第二节点与输出端之间,并被配置为:根据分压电压来控制第二节点的电压,以使得第二晶体管的第一极与第二极之间的电压差低于或者等于电源电压的一半。其中,固定电压端是第二节点。

4、在本公开的一些实施例中,第一静电释放电路包括:第五晶体管。其中,第五晶体管的控制极耦接第五晶体管的第一极和地电压端。第五晶体管的第二极耦接第二节点。

5、在本公开的一些实施例中,第二静电释放电路包括:第六晶体管。其中,第六晶体管的控制极耦接第六晶体管的第一极和第二节点。第六晶体管的第二极耦接输出端。

6、在本公开的一些实施例中,第五晶体管和第六晶体管是nmos晶体管。

7、在本公开的一些实施例中,从输出端输出的电压的幅值范围包括:从零伏到电源电压。

8、在本公开的一些实施例中,分压电压被设置成等于电源电压的一半。

9、在本公开的一些实施例中,分压电压被设置成使得第一节点和第二节点的电压等于电源电压的一半。

10、在本公开的一些实施例中,分压电路包括:第一电阻器、以及第二电阻器。其中,第一电阻器的第一端耦接电源电压端。第一电阻器的第二端耦接第三节点。第二电阻器的第一端耦接第三节点。第二电阻器的第二端接地。

11、在本公开的一些实施例中,第一电阻器的电阻值等于第二电阻器的电阻值。

12、在本公开的一些实施例中,第一承压电路包括:第三晶体管。其中,第三晶体管的控制极耦接第三节点。第三晶体管的第一极耦接第一节点。

13、第三晶体管的第二极耦接输出端。其中,第三晶体管是低阈值晶体管。

14、在本公开的一些实施例中,第二承压电路包括:第四晶体管。其中,第四晶体管的控制极耦接第三节点。第四晶体管的第一极耦接第二节点。

15、第四晶体管的第二极耦接输出端。其中,第四晶体管是低阈值晶体管。

16、在本公开的一些实施例中,第一晶体管是pmos晶体管,第二晶体管是nmos晶体管。

17、在本公开的一些实施例中,第三晶体管是pmos晶体管。

18、在本公开的一些实施例中,第四晶体管是nmos晶体管。

19、根据本公开的第二方面,提供了一种输出级电路,包括:根据本公开的第一方面所述的静电放电电路。

20、根据本公开的第三方面,提供了一种运放。该运放包括:根据本公开的第二方面所述的输出级电路。

21、根据本公开的第四方面,提供了一种芯片。该芯片包括:根据本公开的第三方面所述的运放。

22、根据本公开的第五方面,提供了一种电子设备。该电子设备包括:根据本公开的第四方面所述的芯片。

技术特征:

1.一种静电放电电路,用于对输出级电路的输出端进行静电保护,所述静电放电电路包括:第一静电释放电路和第二静电释放电路,

2.根据权利要求1所述的静电放电电路,其中,所述输出级电路包括:第一晶体管、第二晶体管、分压电路、第一承压电路、以及第二承压电路,

3.根据权利要求2所述的静电放电电路,其中,所述第一静电释放电路包括:第五晶体管,

4.根据权利要求2或3所述的静电放电电路,其中,所述第二静电释放电路包括:第六晶体管,

5.根据权利要求1-3中任一项所述的静电放电电路,其中,从所述输出端输出的电压的幅值范围包括:从零伏到所述电源电压。

6.根据权利要求2-3中任一项所述的静电放电电路,其中,所述分压电压被设置成使得所述第一节点和所述第二节点的电压等于所述电源电压的一半。

7.一种输出级电路,包括:根据权利要求1-6中任一项所述的静电放电电路。

8.一种运放,包括:根据权利要求7所述的输出级电路。

9.一种芯片,包括:根据权利要求8所述的运放。

10.一种电子设备,包括:根据权利要求9所述的芯片。

技术总结

本公开的实施例提供一种静电放电电路、输出级电路、运算放大器、芯片及电子设备。静电放电电路用于对输出级电路的输出端进行静电保护。静电放电电路包括:第一静电释放电路和第二静电释放电路。其中,第一静电释放电路与第二静电释放电路串联连接在地电压端与输出端之间。其中,第一静电释放电路与第二静电释放电路的连接点耦接输出级电路中的固定电压端以使得第一静电释放电路和第二静电释放电路的承压均低于或者等于输出级电路的电源电压的一半。

技术研发人员:文宇

受保护的技术使用者:圣邦微电子(北京)股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!