一种低功耗振荡器的制作方法

本发明涉及集成电路技术领域,特别是涉及一种低功耗振荡器。

背景技术:

在电子电路中,振荡器作为时钟源必不可少,其可用于数据同步、系统唤醒等,特别是在通信系统中,数据的发送和接收都离不开时钟,没有时钟计算机将无法工作、通信系统将会瘫痪。

在当今的系统集成soc中,时钟的一个作用就是用于系统的唤醒,当系统处于休眠状态时,时钟仍需工作,例如烟感监测器。当系统休眠时,电路的功耗需降至极低,以便延长电池的使用的寿命,节约能源,这就要求时钟有极低的功耗。现有的振荡器包括环形振荡器、lc/rc振荡器、晶体振荡器、张弛振荡器等。其中,环形振荡器结构简单,频率范围广,但是频率稳定性差、功耗大;lc/rc振荡器结构简单,功耗低,但是占用面积大,lc振荡器不便于片内集成;晶体振荡器频率精确,但是结构复杂、功耗和面积极大,不能片内集成,只能外挂,在集成电路领域应用受限;张弛振荡器结构简单,频率线性度好,但是需要稳定的偏置电流和比较器、锁存器,功耗偏大。

在现有技术中,如图1所示,rc振荡器一般包括偏置电流源ibias、比较器comp1和comp2以及锁存器rs等器件,需要消耗大量的功耗,而且由于比较器comp1和comp2和锁存器rs会引入延时,这个延时随温度电压变化较大,使得rc振荡器的输出时钟频率不稳定。

技术实现要素:

本发明的主要目的在于提供一种低功耗振荡器,旨在使振荡器的输出时钟信号频率稳定、且功耗低。

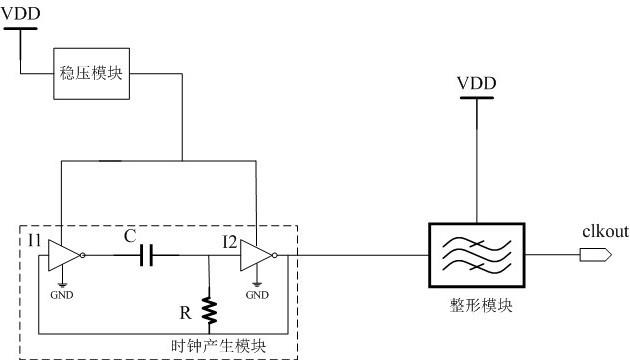

为实现上述目的,本发明提供一种低功耗振荡器,包括稳压模块、时钟产生模块和整形模块,所述稳压模块连接于电源并为所述时钟产生模块提供稳压电压,所述时钟产生模块产生时钟信号并发送至所述整形模块,所述整形模块将所述时钟信号进行整形后输出、并使其满足后续电路的电平需求。

优选地,所述时钟产生模块包括第一反相器、第二反相器、电容和电阻,所述第一反相器和所述第二反相器的电源端连接于所述稳压模块、地端接地,所述电容的一端连接于所述第一反相器的输出端、另一端连接于所述第二反相器的输入端和所述电阻的一端,所述电阻的另一端连接于所述第一反相器的输入端,所述第二反相器的输出端和所述电阻的另一端连接于所述整形模块。

优选地,所述电容的值大于或等于10倍电路寄生电容。

优选地,所述稳压模块的输出电压大于core器件的阈值电压、小于core器件的工作电压。

优选地,所述整形模块为电平转换电路。

优选地,所述整形模块还包括连接于所述电平转换电路的缓冲器,所述缓冲器将电平转换后的时钟信号缓冲后输出。

本发明技术方案通过稳压模块将电源电压降低并为时钟产生模块和整形模块提供电压,经时钟产生模块产生时钟信号后,由整形模块对时钟信号进行整形输出,以满足后续电路的电平需求,这样可以使得振荡器结构简单、输出频率稳定,同时由于振荡器的工作电压降低,使得振荡器的功耗极低。

附图说明

图1为现有技术中rc振荡器的电路原理示意图;

图2为本发明低功耗振荡器的电路原理示意图。

本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

下面结合附图对本发明进一步说明。

如图2所示,本发明实施例提供一种低功耗振荡器,包括稳压模块、时钟产生模块和整形模块,所述稳压模块连接于电源并为所述时钟产生模块提供稳压电压,所述时钟产生模块产生时钟信号并发送至所述整形模块,所述整形模块将所述时钟信号进行整形后输出、并使其满足后续电路的电平需求。

具体地,稳压模块的作用是将电源电压vdd降低以供振荡器工作,以使振荡器工作时功耗降低,在具体实施例中可使用现有技术中任意的稳压电路实现;整形模块的作用主要是把时钟产生模块输出的信号由低压上升至后续电路的工作电压,以便后续电路能正常使用振荡器提供的时钟clkout。

本发明实施例通过稳压模块将电源电压vdd降低并为时钟产生模块和整形模块提供电压,经时钟产生模块产生时钟信号后,由整形模块对时钟信号进行整形输出,以满足后续电路的电平需求,这样可以使得振荡器结构简单、输出频率稳定,同时由于振荡器的工作电压降低,可使得振荡器的功耗极低。

具体的,如图2所示,所述时钟产生模块包括第一反相器i1、第二反相器i2、电容c和电阻r,所述第一反相器i1和所述第二反相器i2的电源端连接于所述稳压模块、地端接地gnd,所述电容c的一端连接于所述第一反相器i1的输出端、另一端连接于所述第二反相器i2的输入端和所述电阻r的一端,所述电阻r的另一端连接于所述第一反相器i1的输入端,所述第二反相器i2的输出端和所述电阻r的另一端连接于所述整形模块。

在本发明实施例中,电容c和电阻r是无源器件,随温度、电压、工艺影响较小,频率稳定性好。同时,时钟产生模块通过采用反相器替代现有技术中的比较器和锁存器,结构简单,引入的延时小,静态零功耗。

具体地,时钟产生模块的延时tt通过等式一:tt=td+trc计算;其中,td是第一反相器i1和第二反相器i2引入的延时(反相器的时延较小,一般为10-12秒级别),电容c和电阻r的时延trc(一般为10-6秒级别)通过等式二:

振荡器的功耗主要是来自于电容c和电阻r充放电,一个周期充放电一次,每次充放电电量q=cu,从等式可知,减少电容c可以减小功耗、降低电压也可以减小功耗,而时钟的周期tt=2.2rc,为了保持频率不变,可减小电容c的值,增加电阻r的值。

优选地,所述电容c的值大于或等于10倍电路寄生电容。考虑到电路寄生电容对振荡器的影响,电容c必须满足c≥10cp,cp为电路寄生电容。

优选地,所述稳压模块的输出电压大于core器件的阈值电压、小于core器件的工作电压。

在不同的工艺条件下,集成电路中的器件有不同的工作电压、阈值电压。而在同一工艺条件下,根据不同的工艺角也会造成器件的阈值电压会在一定范围内变化。

具体地,在tsmc180nm工艺条件下,常用的器件包括3.3v的io器件和1.8v的core器件,而采用1.8v的core器件比采用3.3v的io器件可以获得更低的功耗。本发明实施例在采用1.8v的core器件的基础上,通过稳压模块降低振荡器的工作电压,可在常规工艺下进一步降低功耗,具体原理为:根据具体工艺内容可知,1.8v的core器件的阈值电压在0.45v左右,阈值范围一般为0.35v~0.55v,当输入电压大于阈值电压范围的最大值时器件就可以开启,振荡器就能正常工作。

因此,在具体实施例中,稳压模块的稳压电压设为0.6v,这个电压值可以保证在所有情况下第一反相器i1和第二反相器i2能正常翻转。稳压模块降低了电源噪声,大大提高了电源抑制比,使得振荡器功耗极低、可支持的输入电压的范围较广。

在一些实施例中,所述整形模块为电平转换电路。电平转换电路将时钟产生模块输出的时钟信号进行电平转换,以满足后续电路的电平需要。在具体实施中,电平转换电路可使用现有技术中任意的电平转换电路实现。

具体地,所述整形模块还包括连接于所述电平转换电路的缓冲器,所述缓冲器将电平转换后的时钟信号缓冲后输出。在具体实施例中,缓冲器包括串联的第三反相器和第四反相器,所述第三反相器的输入端连接于电平转换电路、输出端连接于所述第四反相器的输入端,所述第四反相器的输出端输出整形后的时钟clkout。由两个简单的反相器串联可将电平转换后的时钟信号进行整形,以满足后续电路需要的时钟波形。

本发明实施例的工作原理为:稳压模块为时钟产生模块提供稳定的稳压电压,时钟模块中通过使用反相器替代现有技术中的比较器和锁存器,以减小电路的时延,整形模块主要是把时钟产生模块输出的波形由较低的电压整形至core电压阈,供给外部电路使用。

通过对本发明实施例的低功耗振荡器进行仿真后可知,当在tsmc0.18um下,将稳压模块输出的稳压电压设为0.6v、低功耗振荡器的输出时钟频率为32khz时,本发明实施例的低功耗振荡器功耗低至60na,稳压模块的功耗也低至20na。而如图1所示的传统rc振荡器,在tsmc0.18um下、输出时钟频率为32khz时,功耗最少2ua,相差30多倍!

应当理解的是,以上仅为本发明的优选实施例,不能因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

- 还没有人留言评论。精彩留言会获得点赞!