多层电路板及其制造方法与流程

[0001]

本发明涉及一种电路板及其制造方法。尤其涉及一种多层电路板及其制造方法。

背景技术:

[0002]

多层印刷电路板(multilayer printed circuit board)是指一种通过对多个印刷电路板进行层叠而配备有三层以上的布线面的基板。如上所述的多层印刷电路板是通过在基础电路板上添加层间绝缘层的方式实现分层(layer up)。

技术实现要素:

[0003]

发明所要解决的问题

[0004]

在制造多层电路板时添加到基础电路板上的层间绝缘层,是在除基础电路板的连接端子部之外的基础电路板的几乎全部的面上形成。

[0005]

但是,如上所述的在基础电路板上形成有层间绝缘层的多层电路板,会因为一侧面与另一侧面之间的应力差异而造成平坦性的下降并因此导致板弯(bowing)现象。尤其是,当在层叠到基础电路板两侧的图案层数不对称的状态下继续进行分层时,会因为如上所述的应力差异的增加而导致板弯现象的进一步加剧。

[0006]

本发明拟解决的课题在于提供一种用于改善制造多层电路板时所发生的板弯问题的多层电路板及其制造方法。

[0007]

本发明的课题并不限定于在上述内容中提及的课题,相关从业人员将可以通过下述记载进一步明确理解未被提及的其他课题。

[0008]

用于解决问题的方案

[0009]

为了达成如上所述的课题,本发明的多层电路板的一方面(aspect),包括:基材层;第2图案层,形成于上述基材层的一侧面;第1图案层,形成于上述第2图案层上部;以及,层间绝缘层,形成于上述第1图案层与上述第2图案层之间,以与形成有上述第1图案层的区域对应的方式在上述第2图案层上部的一部分形成。

[0010]

上述层间绝缘层可以在与上述基材层的整体面积相比的1%~50%大小的面积上形成。

[0011]

当上述层间绝缘层以至少两个层形成时,上部层间绝缘层的面积可以小于或等于下部层间绝缘层的面积。

[0012]

上述层间绝缘层是在每次向上述基材层上追加图案层时在相邻的两个图案层之间形成,且可以以与相邻的两个图案层中位于上侧的图案层的形成区域对应的方式形成。

[0013]

上述层间绝缘层可以通过在将液状形态的聚酰亚胺(polyimide)成分印刷或涂布到相邻的两个图案层之间之后再进行硬化的方式形成。

[0014]

上述多层电路板,还可以包括:第3图案层,形成于上述基材层的另一侧面;其中,上述第3图案层可以通过形成于上述基材层上的导通孔以及形成于上述层间绝缘层上的导通孔与上述第1图案层以及上述第2图案层电气连接,上述第1图案层可以通过形成于上述

层间绝缘层上的导通孔与上述第2图案层电气连接。

[0015]

上述多层电路板,还可以包括:保护层,形成于上述第1图案层以及上述第2图案层中除端子部之外的剩余区域。

[0016]

上述第1图案层以及上述第2图案层可以利用铜、铝以及铁中的任一种金属形成,可以通过蚀刻法(etching process)、加成法(additive process)、半加成法(semi additive process)以及印刷法中的任一种工艺进行电镀。

[0017]

上述基材层可以利用聚酰亚胺成分、聚酯(polyester)成分、聚对苯二甲酸乙二醇酯(polyethylene terephthalate)成分、聚萘二甲酸乙二醇酯(polyethylene naphthalene)成分、聚碳酸酯(polycarbonate)成分以及环氧树脂(epoxy)成分中的任一种成分以薄膜形态形成。

[0018]

上述多层电路板,还可以包括:补强板(stiffner),为了对上述基材层进行补强而层叠到上述基材层的表面。

[0019]

为了达成如上所述的课题,本发明的多层电路板制造方法的一方面(aspect),包括:通过在基材层的一侧面形成第2图案层而形成基础电路板的步骤;以与形成第1图案层的区域对应的方式在上述第2图案层上部的一部分形成层间绝缘层的步骤;在上述层间绝缘层上部形成上述第1图案层的步骤;以及,在除上述第1图案层以及上述第2图案层的端子部区域之外的剩余区域形成保护层的步骤。

[0020]

在多层电路板制造方法中,还可以在上述基材层的另一侧面形成第3图案层,而在上述基材层上形成上述第2图案层以及上述第3基材层之前,还可以包括:在上述基材层上形成导通孔的步骤。

[0021]

上述形成基础电路板的步骤,可以包括:在上述基材层的两侧面层压(laminate)感光干膜(dry film resist)的步骤;在上述基材层的两侧面形成电镀抗蚀图案的步骤;在上述基材层的两侧面中通过上述电镀抗蚀图案裸露的部分以及上述基材层的导通孔内形成金属层并对上述金属层进行连接的步骤;以及,通过移除上述感光干膜而形成在上述基材层的两侧面形成有上述第2图案层以及上述第3图案层的上述基础电路板的步骤。

[0022]

上述形成第1图案层的步骤,可以包括:在上述层间绝缘层上部形成金属层的步骤;在上述层间绝缘层上形成导通孔的步骤;在上述金属层上部层压感光干膜的步骤;利用层压的上述感光干膜形成电镀抗蚀图案的步骤;通过电镀工艺在上述层间绝缘层上部形成上述第1图案层并通过形成于上述层间绝缘层上的导通孔以及形成于上述基材层上的导通孔对上述第1图案层以及上述第2图案层进行电气连接的步骤;移除上述电镀抗蚀图案的步骤;以及,移除裸露于上述第2图案层的图案之间的金属层的步骤。

[0023]

上述多层电路板制造方法,在上述形成保护层的步骤之后,还可以包括:通过在上述端子部区域安装元件而制造出多层电路板的步骤。

[0024]

其他实施例的具体事项包含于详细的说明以及附图中。

[0025]

发明效果

[0026]

通过本发明,可以达成如下所述的效果。

[0027]

第一,通过在除没有图案层叠的区域之外的有图案层叠的必要区域形成层间绝缘层,可以减少因为层间绝缘层而导致的多层电路板的应力不均衡现象,并借此预防在多层电路板上发生的板弯问题。

[0028]

第二,通过显著减少在以层叠为目的进行加热时的层间绝缘层的收缩区域,可以提升其平坦性,并借此提升电子部件的接合度。

[0029]

第三,通过减少在形成层间绝缘层时所使用的绝缘材料的使用量,可以达成原材料节省效果。

附图说明

[0030]

图1是适用本发明之一实施例的多层电路板的截面图。

[0031]

图2a以及图2b是对现有的多层电路板与本实施例的多层电路板进行比较的示意图。

[0032]

图3是对适用本发明之一实施例的多层电路板制造方法进行概要性图示的流程图。

[0033]

图4至图9是用于对适用本发明之一实施例的多层电路板制造方法的各个步骤进行说明的参考图。

[0034]

图10是对适用本发明之一实施例的基础电路板形成方法进行概要性图示的流程图。

[0035]

图11是对适用本发明之一实施例的第1图案层形成方法进行概要性图示的流程图。

具体实施方式

[0036]

接下来,将参阅附图对本发明的较佳实施例进行详细的说明。本发明的优点和特征及其达成方法,将可以通过结合附图进行详细说明的后续的实施例得到进一步明确。但是,本发明并不限定于在下述内容中公开的实施例,而是可以通过多种不同的形态实现,下述实施例只是为了更加完整地公开本发明,并向具有本发明所属技术领域之一般知识的人员更加完整地介绍本发明的范畴,本发明只应通过权利要求书的范畴做出定义。在整个说明书中,相同的参考符号代表相同的构成要素。

[0037]

当记载为元件(elements)或层位于其他元件或层的“上部(on)”或“上(on)”时,不仅包括直接位于其他元件或层的上部的情况,还包括中间介有其他层或其他元件的情况。而与此相反,当记载为元件“直接位于

……

上部(directly on)”或“正上部”时,表示中间没有其他元件或层存在。

[0038]

为了对一个元件或构成要素与其他元件或构成要素之间的相关关系进行明确说明,可能会使用空间上的相对术语即“下方(below)”、“下侧(beneath)”、“下部(lower)”、“上方(above)”、“上部(upper)”等。空间上的相对术语应理解为是在附图中所图示的方向的基础上还包括使用时或运行时的元件的不同方向的术语。例如,当对附图中所图示的元件进行翻转时,被记载为位于其他元件的“下方(below)”或“下侧(beneath)”的元件可能会位于其他元件的“上方(above)”。因此,示例性的术语“下方”可以同时包括下侧以及上侧方向。元件也可以按照不同的方向进行配置,因此空间性的相对术语可以按照其配置方向做出解释。

[0039]

虽然为了对不同的元件、构成要素和/或部分进行说明可能会使用如第1、第2等术语,但是上述元件、构成要素和/或部分并不因为所使用的术语而受到限定。上述术语只是

用于将一个元件、构成要素或部分与其他元件、构成要素或部分进行区分。因此,在下述内容中所提及的第1元件、第1构成要素或第1部分在本发明的技术思想范围内也可以是第2元件、第2构成要素或第2部分。

[0040]

在本说明书中所使用的术语只是用于对实施例进行说明,并不是为了对本发明做出限定。在本说明书中,除非另有明确的提及,否则单数型语句还包括复数型含义。在本说明书中所使用的如“包含(comprises)”和/或“包括(comprising)”并不排除所提及的构成要素、步骤、动作和/或元件之外的一个以上的其他构成要素、步骤、动作和/或元件存在或被附加的可能性。

[0041]

除非另有定义,否则在本说明书中使用的所有术语(包括技术性以及科学性术语)的含义与具有本发明所属技术领域之一般知识的人员所通常理解的含义相同。此外,除非另有明确的定义,否则通常所使用的已在词典中做出定义的术语不应做出过于理想化或夸张的解释。

[0042]

接下来,将参阅附图对本发明的实施例进行详细的说明,而在参阅附图进行说明的过程中,与图号无关,为相同或对应的构成要素分配了相同的参考编号并省略与其相关的详细说明。

[0043]

板弯(bowing)问题是在多层电路板上安装电子部件时导致其位置错位乃至接合不良的主要因素。而且,板弯问题还可能在为了与其他电子部件进行组装而对产品进行移送时导致脱离的现象。

[0044]

本发明所提供的多层电路板旨在改善板弯问题,其特征在于:在形成最上层(layer)时仅在必要区域局部性地形成绝缘层区域。接下来,将参阅附图对本发明进行详细的说明。

[0045]

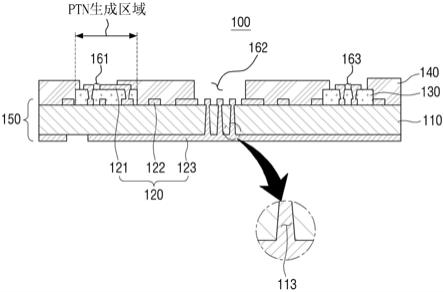

图1是适用本发明之一实施例的多层电路板的截面图。

[0046]

参阅图1,多层电路板100可以包括基材层110、图案层120、层间绝缘层130以及保护层140。

[0047]

基材层110是一定厚度的基材(base film),可以以平板形态形成。如上所述的基材层110可以将聚酰亚胺(polyimide)成分作为原料以薄膜形态进行制造。但是,本实施例并不因此而受到限定。作为一实例,基材层110除聚酰亚胺成分之外,还可以将从由聚酯(polyester)成分、聚对苯二甲酸乙二醇酯(polyethylene terephthalate)成分、聚萘二甲酸乙二醇酯(polyethylene naphthalene)成分、聚碳酸酯(polycarbonate)成分以及环氧树脂(epoxy)成分等高分子树脂构成的组中选择的物质(柔性材料)作为原料以薄膜形态进行制造。

[0048]

基材层110可以为了强化平板的强度而包括补强板(stiffner;未图示)。补强板可以将聚对苯二甲酸乙二醇酯(pet)成分作为原料进行制造,但是本实施例并不因此而受到限定。

[0049]

补强板可以在基材层110的一侧面或两侧面上层叠形成。但是,本实施例并不因此而受到限定。即,补强板也可以通过作为制造基材层110时的成分进行添加而混合到基材层110上。作为一实例,可以通过在将从聚酰亚胺成分、聚酯成分、聚对苯二甲酸乙二醇酯成分、聚萘二甲酸乙二醇酯成分、聚碳酸酯成分以及环氧树脂成分中选择的物质作为原料制造基材层110时混合聚对苯二甲酸乙二醇酯成分的补强板而制造出强度得到提升的基材层

110。

[0050]

图案层120可以起到对电子部件进行电气连接的布线功能,可以直接安装元件或安装与外部设备连接的端子。如上所述的图案层120除了起到电气功能的图案之外,还可以包括补强图案、虚拟图案、接地图案、屏蔽图案或重布线图案等。

[0051]

图案层120可以在基材层110的一侧面或两侧面层叠形成。当图案层120是在基材层110的两侧面分别形成时,可以通过形成于基材层110上的导通孔113(例如通孔(through hole)、通路孔(via hole)等)相互电气连接。

[0052]

图案层120可以将铜作为原料以金属层形成。但是,本实施例并不因此而受到限定。作为一实例,图案层120可以将从由铝、铁等金属构成的组中选择的物质作为原料形成。

[0053]

图案层120可以利用制造印刷电路板的通常的电路形成工艺在基材层110上部电镀(plating)形成。作为一实例,图案层120可以通过如蚀刻法(etching process)、加成法(additive process)、半加成法(semi additive process)以及印刷法(例如丝网印刷法)等在基材层110上部电镀形成。此外,图案层120也可以通过如涂布、层压等层叠工艺在基材层110上部形成。

[0054]

图案层120可以以在基材层110的两侧面包括一个以上的图案层的方式形成。此时,图案层120可以以在基材层110的两侧面包括相同数量的图案层的方式形成。作为一实例,图案层120可以在基材层110的一侧面形成第1图案层121以及第2图案层122,并在基材层110的另一侧面形成第3图案层123,从而以在两侧面包括三个图案层的方式形成。此外,图案层120也可以以仅在基材层110的一侧面包括两个以上的图案层的方式形成。

[0055]

考虑到可以将多个仅在一侧面形成有金属层的基材层110进行层叠的情况,图案层120也可以以仅在一侧面包括两个以上的第n图案层(n为2以上的自然数)的方式形成。

[0056]

在图案层120包括第1图案层121、第2图案层122、第3图案层123等三个图案层的情况下,可以以如下所述的形态形成于基材层110上部。

[0057]

第2图案层122可以形成于基材层110的一侧面上,第3图案层123可以形成于基材层110的量一侧面上。第2图案层122以及第3图案层123可以通过在基材层110的两侧面层压(laminating)感光干膜(dfr;dry film resist)并通过曝光、显影等方式形成电镀抗蚀图案之后对通过电镀抗蚀图案裸露的金属层进行电镀的方式形成于基材层110的两侧面。

[0058]

此外,第2图案层122以及第3图案层123可以通过在基材层110的导通孔内形成的金属层在相互之间实现电气连接。

[0059]

基础电路板150可以包括基材层110以及在上述基材层110上部直接形成的图案层(即第2图案层122以及第3图案层123)。基础电路板150可以通过从基材层110的两侧面移除感光干膜的方式形成。

[0060]

第1图案层121可以在第2图案层122上部形成。如上所述的第1图案层121可以利用层间绝缘层130在第2图案层122上部形成。即,可以在第2图案层122上部形成层间绝缘层130并在上述层间绝缘层130上部形成第1图案层121。

[0061]

此外,第1图案层121也可以形成于第3图案层123上部而不是第2图案层122上部。此外,第1图案层121也可以同时形成于第2图案层122上部以及第3图案层123上部。

[0062]

第1图案层121与第2图案层122以及第3图案层123等相同,可以通过在层间绝缘层130上部的金属层层压感光干膜并通过曝光、显影等方式形成电镀抗蚀图案之后通过电解

电镀、无电解电镀等电镀工艺形成于层间绝缘层130上部。

[0063]

第1图案层121可以在层间绝缘层130上形成电镀填充的导通孔之后通过上述导通孔与第2图案层122实现电气连接。此外,第1图案层121也可以通过形成于层间绝缘层130上的导通孔以及基材层110的导通孔与第3图案层123实现电气连接。

[0064]

此外,在本实施例中,也可以根据需要作为图案表面处理在第1图案层121、第2图案层122、第3图案层123等的上部形成金属镀膜。

[0065]

金属镀膜可以将从由锡、金、铬等中选择的至少一种以上的金属作为原料形成。但是,本实施例并不因此而受到限定。

[0066]

金属镀膜可以通过电镀方法在第1图案层121、第2图案层123、第3图案层123等的上部形成。但是,本实施例并不因此而受到限定。

[0067]

层间绝缘层130用于起到绝缘功能,可以将绝缘体(或电介质)作为原料形成。如上所述的层间绝缘层130可以形成于依次层叠到基材层110的一侧面上部的图案层之间,如第1图案层121与第2图案层122之间。

[0068]

层间绝缘层130可以形成于第2图案层122上部的整个面上。但是,在上述情况下会在基材层110的两侧面之间形成应力差异且层叠到基材层110的一侧面或两侧面上的层数也是非对称状态,因此会导致以及加剧多层电路板100上的板弯现象。

[0069]

在本实施例中考虑到如上所述的问题,在第2图案层122上部形成层间绝缘层130时并不是在整个面上形成,而是以与基础电路板150上通过层间绝缘层130层叠的图案层(即第1图案层121)的形成区域对应的方式部分形成。

[0070]

在本实施例中,即使是第2图案层122的上部,只要其上部没有形成第1图案层121,在相应区域也不会形成层间绝缘层130。即,不形成层间绝缘层130的区域,可以包括形成有不与基础电路板150上的第1图案层121重叠的图案的区域,以及形成于基础电路板150上的连接端子区域161、162、163。

[0071]

层间绝缘层130可以将液状聚酰亚胺作为原料形成。如上所述的层间绝缘层130,可以通过在相邻的两个图案层之间印刷(或涂布)液状聚酰亚胺并进行硬化的方式形成。

[0072]

层间绝缘层130可以在与基材层110的整体面积中的1%~50%对应的面积上形成。这是因为,当在不足1%的面积上形成层间绝缘层130时,很难在层间绝缘层130上部确保用于形成其他图案层的空间,而当在超过第2图案层122上部的整体面积中的50%的面积上形成层间绝缘层130时,可能会因为应力不均衡而导致板弯现象。

[0073]

层间绝缘层130可以以单层形成,但是也可以根据设计以多层形成。在如上所述的情况下,上部的层间绝缘层的形成面积可以等于下部的层间绝缘层,或者其形成面积可以小于下部的层间绝缘层。

[0074]

在层间绝缘层130上可以配备导通孔。层间绝缘层130的导通孔用于起到对第1图案层121以及第2图案层122进行电气连接的作用。层间绝缘层130的导通孔与基材层110的导通孔相同,可以利用激光形成,而当层间绝缘层130是将感光性材料为原料形成时,也可以通过曝光、显影等方式形成。

[0075]

此外,层间绝缘层130的导通孔与基材层110的导通孔相同,可以以一端的大小与另一端的大小不同的方式形成,但是本实施例并不因此而受到限定。

[0076]

此外,虽未图示,但是当在第3图案层123上部形成第4图案层的情况下,与第1图案

层121以及第2图案层122的情况相同,层间绝缘层130也可以在第3图案层123与其上部的第4图案层之间形成。此外,当在第1图案层121上部形成第5图案层的情况下,层间绝缘层130也可以在第1图案层121与其上部的第5图案层之间形成。即,在本实施例中,当在基材层110的一侧面上形成n个图案层的情况下,可以在上述一侧面上配备n-1个层间绝缘层130。

[0077]

保护层140用于对第1图案层121以及第2图案层122进行保护,可以在形成有第1图案层121、第2图案层122、层间绝缘层130等的基材层110的一侧面上部形成。但是,保护层140不会在端子结合的部分形成。即,保护层140可以在基材层110的一侧面上部中除端子结合区域之外的剩余区域形成。

[0078]

保护层可以将阻焊剂(solder resist)作为原料形成。但是,在本实施例中,保护层140的原料并不限定于阻焊剂。

[0079]

保护层140可以通过对阻焊剂进行印刷的方式形成。但是,在本实施例中,保护层140的形成方法并不限定于印刷方法。

[0080]

图2a以及图2b是对现有的多层电路板与本实施例的多层电路板进行比较的示意图。

[0081]

现有的非对称形态的多层电路板如图2a所示,因为板弯现象而导致的差异达到22mm。而与此相反,本实施例的多层电路板如图2b所示,因为板弯现象而导致的差异仅为2mm,可以确认与现有方式相比得到了显著的改善。

[0082]

接下来,将对适用本实施例的多层电路板的制造方法进行说明。图3是对适用本发明之一实施例的多层电路板制造方法进行概要性图示的流程图。

[0083]

首先,在步骤s210中,准备在两侧面形成有金属层111、112的基材层110。如上所述的基材层110如图4所示,可以将聚酰亚胺薄膜作为原料形成基材。此外,虽未图示,也可以仅在基材层110的一侧面形成金属层。

[0084]

形成于基材层110的两侧面的金属层111、112可以由铜层形成。金属层111、112可以通过如电解电镀、无电解电镀等多种电镀方法形成于基材层110的两侧面。但是,本实施例并不因此而受到限定。

[0085]

接下来,在步骤s220中,在基材层110的特定位置形成贯通两侧面的导通孔。

[0086]

接下来,在步骤s230中,通过利用电路形成工艺在基材层110的两侧面形成第2图案层122以及第3图案层123而形成基础电路板150。如上所述的基础电路板150如图5所示。

[0087]

在本实施例中,可以按照如下所述的顺序形成基础电路板150。但是这仅为一个实例,本实施例并不因此而受到限定。

[0088]

图10是对适用本发明之一实施例的基础电路板形成方法进行概要性图示的流程图。接下来,将参阅图10进行说明。

[0089]

首先,在步骤s310中,在基材层110的两侧面层压感光干膜(dfr)。

[0090]

接下来,在步骤s320中,通过曝光、显影等方式在基材层110的两侧面形成电镀抗蚀图案。

[0091]

接下来,在步骤s330中,在基材层110的两侧面中通过电镀抗蚀图案裸露的部分以及基材层110的导通孔内形成金属层,从而形成可以使基材层110的两侧面相互电气连接的图案。

[0092]

在本实施例中,可以利用进度电镀(例如铜电镀)的方式在通过电镀抗蚀图案裸露

的部分以及基材层110的导通孔内形成金属层。作为此时的电镀方法,可以利用如电解电镀、无电解电镀等。

[0093]

接下来,在步骤s340中,移除基材层110的两侧面的感光干膜。

[0094]

接下来,在步骤s350中,通过移除形成有图案的部分之外的剩余部分的金属层而完成图案。通过完成图案,可以形成在基材层110的一侧面形成有第2图案层122并在基材层110的另一侧面形成有第3图案层123的基础电路板150。

[0095]

此外,第2图案层122以及第3图案层123可以安装元件或包括与外部设备连接的端子部。在本实施例中,第1图案层121与第2图案层122、第3图案层123相同,也可以包括端子部。

[0096]

接下来,将重新参阅图3进行说明。

[0097]

在步骤s240中,在形成基础电路板150之后在第2图案层122上部形成层间绝缘层130。在基础电路板150上部形成层间绝缘层130的结构如图6所示。

[0098]

层间绝缘层130可以在除第2图案层122的端子部以及没有形成层叠到基础电路板150上的图案的电路区域之外的部分形成。即,层间绝缘层130可以以与在基础电路板150上通过层间绝缘层层叠的图案的形成区域对应的方式形成。在本实施例中,在层间绝缘层130上形成的图案为第1图案层121。

[0099]

接下来,在步骤s250中,在层间绝缘层130上部形成第1图案层121。在层间绝缘层130上部形成第1图案层121的结构如图7所示。

[0100]

在本实施例中,可以按照如下所述的顺序在层间绝缘层130上部形成第1图案层121。但是这仅为一个实例,本实施例并不因此而受到限定。

[0101]

图11是对适用本发明之一实施例的第1图案层形成方法进行概要性图示的流程图。接下来,将参阅图11进行说明。

[0102]

首先,在步骤s410中,在层间绝缘层130上部形成金属层。

[0103]

接下来,在步骤s420中,为了使第2图案层122裸露而在层间绝缘层130上形成导通孔。

[0104]

接下来,在步骤s430中,在金属层上部层压感光干膜。

[0105]

接下来,在步骤s440中,通过曝光、显影等方式利用层压到层间绝缘层130上部的感光干膜形成抗蚀图案。

[0106]

接下来,在步骤s450中,利用如电解电镀、无电解电镀等电镀工艺在层间绝缘层130上部形成第1图案层121。此时,层间绝缘层130的导通孔也可以通过电镀方式进行填充,从而使第1图案层121与第2图案层122、第3图案层123等电气连接。

[0107]

接下来,在步骤s460中,通过移除金属层上部的感光干膜以及电镀抗蚀图案并移除形成有图案的部分之外的剩余部分(例如裸露于第2图案层的图案之间的部分)的金属层而完成第1图案层121。

[0108]

接下来,将重新参阅图3进行说明。

[0109]

在层间绝缘层130上部形成第1图案层121之后,在步骤s260中,为了对第1图案层121以及第2图案层122进行保护而在除各个图案的端子部之外的区域形成保护层140。在第1图案层121以及第2图案层122上部形成保护层140的结构如图8所示。

[0110]

接下来,在步骤s270中,通过将元件170安装到端子部160而制造出多层电路板。安

装有元件的多层电路板100如图9所示。

[0111]

在上述内容中,参阅图1至图11对适用本实施例的多层电路板及其制造方法进行了说明。本实施例的目的在于改善因为制造多层电路板时的非对称结构以及绝缘层的热收缩特性而导致的板弯(bowing)现象,在形成最上层(layer)时在必要的区域局部形成绝缘层区域。本实施例可以借此达成如下所述的效果。

[0112]

第一,通过在除没有图案层叠的区域之外的有图案层叠的必要区域形成层间绝缘层130,可以减少因为层间绝缘层130而导致的多层电路板的应力不均衡现象,并借此预防在多层电路板上发生的板弯问题。

[0113]

第二,通过显著减少在以层叠为目的进行加热时的层间绝缘层130的收缩区域,可以提升其平坦性,并借此提升电子部件的接合度。

[0114]

第三,通过减少在形成层间绝缘层130时所使用的绝缘材料的使用量,可以达成原材料节省效果。

[0115]

在上述内容中参阅附图对本发明的实施例进行了说明,但是具有本发明所属技术领域之一般知识的人员应可以理解,本发明可以在不对本发明的技术思想或必要特征进行变更的前提下以其他具体的形态实施。因此,在上述内容中记述的实施例在所有方面仅为示例性目的而非限定。

[0116]

工业实用性

[0117]

本发明可适用于印刷电路板。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1