电平移位电路以及集成电路的制作方法

[0001]

本发明涉及集成电路领域,具体涉及一种电平移位电路以及集成电路。

背景技术:

[0002]

电平移位电路将低压逻辑控制信号转换为高压逻辑控制信号,实现低压逻辑输入级对高压逻辑输出级的控制,在显示驱动以及闪存等方面有广泛的应用。在液晶显示器的源极驱动芯片、电源管理芯片、时序控制芯片等应用中,电平移位电路一方面要求较低电压输入,另一方面又要求能在较大电源噪声的情况下正常工作。

[0003]

如图1所示,现有技术提供一种用于lcd模块的扫描驱动器的现有低压输入型电平移位电路,其将一低压数字信号转换为高压数字信号。该电平移位电路包含两个lv(低压)mos晶体管m1-m2和四个hv(高压)mos晶体管m3-m6。两个lv nmos晶体管m1及m2的源极及基板(substrate)连接至接地电压vssa,漏极分别连接至两个hv nmos晶体管m5及m6的源极,m5和m6的基板连接至接地电压vssa,栅极连接至控制信号vb,vb具有合适的电压,可以同时保证m5和m6导通,并且保护lv nmos m1和m2免受来自高电源电压vdda的损害,漏极分别连接至两个hv pmos晶体管m3和m4的漏极,m3和m4的源极及基板连接至电源电压vdda(例如9伏特或18伏特)。然而在多个驱动较大负载的缓冲同时进行翻转工作时,高电压电源容易产生较大噪声,在高电源噪声影响下,现有技术提供的电平移位电路会出现一些问题,例如:首先,输出信号状态切换的时间会增加。第二,可能在所有六个晶体管m1-m6皆导通时产生dc电流路径,从而消耗较大电流。第三,由于dc电流栓锁(latch)而使得转态(switching states)失败。进而造成现有技术提供的电平移位电路在低电压输入,在较大电源噪声的情况容易出现不能正常工作的问题。

技术实现要素:

[0004]

本发明提供一种电平移位电路以及集成电路,用以解决电平移位电路在低电压输入,在较大电源噪声的情况容易出现不能正常工作的问题。

[0005]

根据本发明的第一方面,本发明提供一种电平移位电路,包括:一负载单元,用以接收电源电压信号以及第一控制信号以产生栅极控制信号;一输入单元,用以接收输入信号以使所述栅极控制信号接地;以及多个偏置单元,设于所述负载单元和所述输入单元之间,所述多个偏置单元用以接收偏置电压信号以使所述栅极控制信号传输至所述输入单元,多个所述偏置单元相互串联并耦接至所述负载单元,所述多个偏置单元包括第一偏置单元、第二偏置单元以及第三偏置单元,所述第一偏置单元用于限制所述输入单元的漏级电位,所述第二偏置单元用于限制第一偏置单元的漏级电位,所述第三偏置单元用于提供所述负载单元的栅极控制电源;其中,所述电平移位电路用于将第一信号转化成第二信号,所述第二信号的电压大于所述第一信号的电压。

[0006]

在一些实施例中,所述输入单元包括:第一开关管以及第二开关管,所述第一开关管和所述第二开关管的基板及源级均连接至接地电压信号,所述第一开关管和所述第二开

关管的栅极连接分别连接至输入信号和反向输入信号;所述多个偏置单元包括:第三开关管和第四开关管,所述第三开关管和所述第四开关管的基板均连接至接地电压信号,所述第三开关管和所述第四开关管的源级分别连接至所述第一开关管和所述第二开关管的漏级,所述第三开关管和所述第四开关管的栅极均连接至第一偏置电压信号;第五开关管和第六开关管,所述第五开关管和所述第六开关管的基板均连接至接地电压信号,所述第五开关管和所述第六开关管的源级分别连接至所述第三开关管和所述第四开关管的漏级,所述第五开关管和所述第六开关管的栅极均连接至第二偏置电压信号;第七开关管和第八开关管,所述第七开关管和所述第八开关管的基板均连接至电源电压信号,所述第七开关管和所述第八开关管的漏级分别连接至所述第五开关管和所述第六开关管的漏极,所述第七开关管和所述第八开关管的栅极均连接至第三偏置电压信号;所述负载单元包括:第九开关管和第十开关管,所述第九开关管和所述第十开关管的基板和源极均连接至电源电压信号,所述第九开关管和所述第十开关管的漏极连接至所述第七开关管和所述第八开关管的源极,所述第九开关管的栅极分别耦接至所述第六开关管和所述第八开关管的漏极,所述第十开关管的栅极分别耦接至所述第五开关管和所述第七开关管的漏极;其中,所述第五开关管和所述第七开关管的漏极为所述电平移位电路的第一输出端,所述第六开关管和所述第八开关管的漏极为所述电平移位电路的第二输出端。

[0007]

在一些实施例中,所述第一开关管和所述第二开关管为第一n型晶体管或第一p型晶体管的一种。

[0008]

在一些实施例中,所述第三开关管和所述第四开关管为第二n型晶体管或第二p型晶体管的一种。

[0009]

在一些实施例中,所述第五开关管和所述第六开关管为第二n型晶体管或第二p型晶体管的一种。

[0010]

在一些实施例中,所述第七开关管和所述第八开关管为第二n型晶体管或第二p型晶体管的一种。

[0011]

在一些实施例中,所述第九开关管和所述第十开关管为第二n型晶体管或第二p型晶体管的一种。

[0012]

根据本发明的第二方面,本发明提供一种集成电路,包括如上述的电平移位电路。

[0013]

在一些实施例中,所述集成电路还包括:偏置电压发生器,用于为所述电平移位电路提供多个偏置电压信号,所述多个偏置电压信号包括:电源电压信号、接地电压信号、第一控制电压信号、第二控制电压信号以及第三控制电压信号。

[0014]

与现有技术相比,本发明的有益效果:在不增加过多的版图面积的情况下,保证低压输入的快速转态,同时有效减少电源噪声对电平移位电路的影响,从而增加电平移位电路的鲁棒性。

附图说明

[0015]

图1为现有技术提供的一种电平移位电路的结构示意图

[0016]

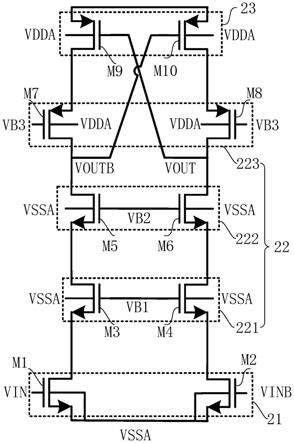

图2为本发明实施例提供的一种电平移位电路的结构示意图。

[0017]

图3a-3c为图2所示的电平移位电路的电路仿真图。

[0018]

图4为本发明实施例提供的一种集成电路的结构示意图。

具体实施方式

[0019]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0020]

如图2所示,本发明实施例提供一种电平移位电路,该电平移位电路用于将第一信号转化成第二信号,所述第二信号的电压大于所述第一信号的电压。该电平移位电路包括输入单元21、多个偏置单元22以及负载单元23。其中多个偏置单元22包括第一偏置单元221、第二偏置单元222以及第三偏置单元223。

[0021]

负载单元23用以接收电源电压信号(vdda)以及第一控制信号(vdda)以产生栅极控制信号(vout、voutb)。

[0022]

多个偏置单元22设于负载单元23和输入单元21之间,多个偏置单元22用以接收偏置电压信号(vb1、vb2、vb3)以使栅极控制信号(vout、voutb)传输至输入单元21,多个偏置单元22相互串联并耦接至负载单元23。

[0023]

输入单元21用以接收输入信号(vin、vinb)以使栅极控制信号(vout、voutb)接地。

[0024]

具体的,输入单元21包括:第一开关管m1以及第二开关管m2。第一开关管m1和第二开关管m2的基板及源级均连接至接地电压信号(vssa),第一开关管m1和所述第二开关管m2的栅极连接分别连接至输入信号(vin)和反向输入信号(vinb)。

[0025]

第一偏置单元221包括:第三开关管m3和第四开关管m4。第三开关管m3和第四开关管m4的基板均连接至接地电压信号(vssa),第三开关管m3和第四开关管m4的源级分别连接至第一开关管m1和第二开关管m2的漏级,第三开关管m3和第四开关管m4的栅极均连接至第一偏置电压信号(vb1)。该第一偏置单元221用于限制输入单元21中第一开关管m1和第二开关管m2的漏极电位,限制电平移位电路自身的转换尖峰电流,降低电源噪声,从而加快输出信号状态的切换时间。

[0026]

第二偏置单元222包括:第五开关管m5和第六开关管m6。第五开关管m5和第六开关管m6的基板均连接至接地电压信号(vssa),第五开关管m5和第六开关管m6的源级分别连接至第三开关管m3和第四开关管m4的漏级,第五开关管m5和第六开关管m6的栅极均连接至第二偏置电压信号(vb2)。该第二偏置单元222用于进一步提高电路的抗电源噪声,进而提高电平移位电路的鲁棒性。

[0027]

第三偏置单元223包括:第七开关管m7和第八开关管m8。第七开关管m7和第八开关管m8的基板均连接至电源电压信号(vdda),第七开关管m7和第八开关管m8的漏级分别连接至第五开关管m5和第六开关管m6的漏极,第七开关管m7和第八开关管m8的栅极均连接至第三偏置电压信号(vb3)。该第三偏置单元223用于限制负载单元23中第九开关管m9和第十开关管m10的电流,同时提供了栅极控制电流源,提高电路驱动能力。

[0028]

提供多个偏置单元22,即提供多个开关管并对其施加相应的偏置电压,可以降低电源噪声对电平移位电路的影响,从而避免dc电流路径的产生。

[0029]

负载单元23包括:第九开关管m9和第十开关管m10。第九开关管m9和第十开关管m10的基板和源极均连接至电源电压信号(vdda),第九开关管m9和第十开关管m10的漏极连接至第七开关管m7和第八开关管m8的源极,第九开关管m9的栅极分别耦接至第六开关管m6

和第八开关管m8的漏极,第十开关管m10的栅极分别耦接至第五开关管m5和第七开关管m7的漏极。

[0030]

第五开关管m5和第七开关管m7的漏极为电平移位电路的第一输出端,第六开关管m6和第八开关管m8的漏极为电平移位电路的第二输出端。

[0031]

其中,第一开关管m1和第二开关管m2为第一n型晶体管(低压n型晶体管)或第一p型晶体管(低压p型晶体管)的一种。

[0032]

第三开关管m3和第四开关管m4为第二n型晶体管(高压n型晶体管)或第二p型晶体管(高压p型晶体管)的一种。

[0033]

第五开关管m5和第六开关管m6为第二n型晶体管(高压n型晶体管)或第二p型晶体管(高压p型晶体管)的一种。

[0034]

第七开关管m7和第八开关管m8为第二n型晶体管(高压n型晶体管)或第二p型晶体管(高压p型晶体管)的一种。

[0035]

第九开关管m9和第十开关管m10为第二n型晶体管(高压n型晶体管)或第二p型晶体管(高压p型晶体管)的一种。

[0036]

在本发明实施例中,第一开关管m1以及第二开关管m2为低压n型晶体管,第三开关管m3至第六开关管m6为高压n型晶体管,第七开关管m7至第十开关管m10为高压p型晶体管。以本发明实施例对电平移位电路的操作原理说明如下。

[0037]

提供偏置电压信号vb1、vb2以及vb3以导通第三开关管m3至第八开关管m8。当将一具有低压高逻辑状态(例如1.4伏特)的输入信号vin施加于第一开关管m1处且一具有低压低逻辑状态(例如0伏特)的反相输入信号vinb施加于第二开关管m2处时,第一开关管m1导通,第十开关管m10的栅极通过第五开关管m5、第三开关管m3与第一开关管m1连接到地,第十开关管m10因此导通。第二开关管m2由于施加于其栅极处的具有低压低逻辑状态(即0伏特)的反相信号vinb而被关闭(turn off),因此输出信号vout显示电源电压vdda的高压高逻辑状态,输出信号voutb连接到地显示地电压vssa的高压低逻辑状态。亦即,低压高逻辑状态(例如1.4伏特)的输入信号vin通过电平移位电路被转换为高压高逻辑状态(例如9伏特或18伏特)的输出信号vout。当输入信号vin切换至低压低逻辑状态(0伏特)且反相信号vinb切换至低压高逻辑状态(1.4伏特)时,第一开关管m1得以关闭且第二开关管m2得以导通。第九开关管m9的栅极藉由导通的第六开关管m6、第四开关管m4和第二开关管m2连接到地,第九开关管m9因此导通,第十开关管m10的栅极藉由导通的第九开关管m9连接到电源电压vdda,第十开关管m10因此关闭。因此,输出信号vout显示高压低逻辑状态(0伏特)。亦即,低压低逻辑状态(0伏特)藉由电平移位电路而被转换为高压低逻辑状态(0伏特)。

[0038]

参考图3a-3c,为如图2的电平移位电路的电路仿真图。a曲线为电源电压vdda随时间的变化曲线;b曲线为接地电压vssa随时间的变化曲线;c曲线为输入信号随时间的变化曲线;d曲线和e曲线为输出电压比较,其中d曲线为现有技术的电平移位电路的输出电压随时间的变化曲线,e曲线为本实施例的电平移位电路的输出电压随时间的变化曲线。由图3a-3c可知,当输入信号由0伏特上升到1.4伏特时,输出电压由0伏特上升到13伏特左右。在输入信号由0伏特上升到1.4伏特的同时,电源电压vdda和接地电压vssa同时施加1.5v的噪声,现有技术的电平移位电路状态转换出现问题,无法正常翻转,本实施例的电平移位电路工作正常。因此,本发明实施例的电平移位电路同时具有低输入电压和抗电源噪声的功能。

[0039]

如图4所示,本发明实施例提供一种集成电路40,包括上文所述的电平移位电路41以及偏置电压发生器42。

[0040]

偏置电压发生器42用于为电平移位电路41提供多个偏置电压信号,多个偏置电压信号包括:电源电压信号、接地电压信号、第一控制电压信号、第二控制电压信号以及第三控制电压信号。

[0041]

本发明的有益效果在于:在不增加过多的版图面积的情况下,保证低压输入的快速转态,同时有效减少电源噪声对电平移位电路的影响,从而增加电平移位电路的鲁棒性。

[0042]

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

[0043]

上面结合附图对本发明的实施例进行了描述,但是本发明并不局限于上述的具体实施方式,上述的具体实施方式仅仅是示意性的,而不是限制性的,本领域的普通技术人员在本发明的启示下,在不脱离本发明宗旨和权利要求所保护的范围情况下,还可做出很多形式,均属于本发明的保护之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1