具有电磁辐射屏蔽机制的电感性装置及其制造方法与流程

1.本发明是关于电磁辐射屏蔽技术,尤其是关于一种具有电磁辐射屏蔽机制的电感性装置及其制造方法。

背景技术:

2.电感性的组件,例如电感以及变压器,在射频集成电路中是重要的组件,其可实现信号转换、耦合与阻抗匹配。在系统单芯片成为集成电路的主流后,整合在集成电路上的电感与变压器逐渐取代传统独立的组件,并广为应用在射频集成电路上。然而,集成电路上的电感与变压器经常受到外部电磁辐射,亦或自身产生电磁辐射影响其他组件。

3.因此,如何使集成电路上的电感与变压器具有电磁辐射屏蔽机制,来达到避免电磁辐射干扰的目的,成为重要的议题。

技术实现要素:

4.鉴于背景技术的问题,本发明的一目的在于提供一种具有电磁辐射屏蔽机制的电感性装置及其制造方法,以改善现有技术。

5.本发明包含一种具有电磁辐射屏蔽机制的电感性装置(inductive device),用以建立与电子装置间的电磁辐射屏蔽,包含:电感性组件以及至少一第一屏蔽结构。第一屏蔽结构具有封闭形状,邻设于电感性组件的一侧,并位于电感性组件以及电子装置间。

6.本发明另包含一种电感性装置制造方法,用以制造具有电磁辐射屏蔽机制的电感性装置,并建立与电子装置间的电磁辐射屏蔽,电感性装置制造方法包含:形成电感性组件;对电感性组件进行电磁辐射测试;以及当与电感性组件以及电子装置间相关的电磁辐射量超过辐射临界值时,形成具有封闭形状的至少一第一屏蔽结构,其中第一屏蔽结构邻设于电感性组件的一侧,并位于电感性组件以及电子装置间。

7.有关本发明的特征、实际操作与功效,兹配合附图作优选实施例详细说明如下。

附图说明

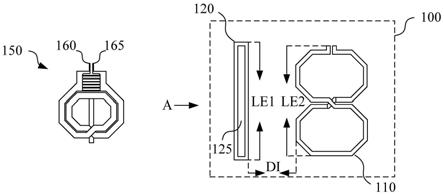

8.图1示出本发明的一实施例中,一种具有电磁辐射屏蔽机制的电感性装置的俯视图;

9.图2示出本发明的一实施例中,一种具有电磁辐射屏蔽机制的电感性装置的俯视图;

10.图3示出本发明的一实施例中,图1的电感性装置沿a方向的侧视图;以及

11.图4示出本发明一实施例中,在电子装置操作于不同操作频率下,电感性装置中的电感性组件的一端点所测量到电子装置产生的电磁辐射耦合量的示意图;

12.图5示出本发明一实施例中,电感性组件分别在不同屏蔽结构的设置下,所测量到电子装置产生的电磁辐射耦合量的示意图;以及

13.图6示出本发明一实施例中,一种电感性装置制造方法的流程图。

具体实施方式

14.本发明的一目的在于提供一种具有电磁辐射屏蔽机制的电感性装置及其制造方法,可通过具有封闭形状的第一屏蔽结构,设置于会互相造成影响的电感性组件以及电子装置间,在提供电磁屏蔽的功效的同时,不对电感性组件的操作效能造成影响,并维持较小的电路面积。

15.请参照图1。图1示出本发明的一实施例中,一种具有电磁辐射屏蔽机制的电感性装置100的俯视图。

16.电感性装置100用以建立与电子装置150间的电磁辐射屏蔽。其中,电子装置150可为例如,但不限于具有两端点160以及165的电感。其中,端点160及165其中之一可作为信号输入端,另一者可作为信号输出端。电感性装置100可在不影响自身操作,例如质量因子的大小的情形下建立电磁辐射屏蔽,避免电感性装置100以及电子装置150对彼此造成电磁辐射的干扰。

17.电感性装置100包含:电感性组件110以及第一屏蔽结构120。

18.电感性组件110包含例如,但不限于集成电路电感或是集成电路变压器的组件。在一实施例中,电感性组件110可操作为例如,但不限于电压控制振荡器(voltage control oscillator;vco)或是功率放大器。然而,本发明不限于此。

19.电感性组件110可产生内部电磁辐射,以使附近的外部电路组件,例如电子装置150受到电磁辐射的影响。反之,外部电路组件,例如电子装置150亦可产生外部电磁辐射,影响电感性组件110的操作。

20.如图1所示,第一屏蔽结构120具有封闭形状,邻设于电感性组件110的一侧,并位于电感性组件110以及电子装置150间。在一实施例中,第一屏蔽结构120的材质为金属。第一屏蔽结构120的形状可为例如,但不限于环状、矩形或其他可形成一封闭区域125的形状。在图1中,第一屏蔽结构120的形状是以矩形为范例进行示出,然而本发明不为此限。更进一步地,第一屏蔽结构120可为电性隔离(亦即未连接至任何电压源或是接地)或是接地。

21.当第一屏蔽结构120附近有电磁辐射产生,不论是由电感性组件110或电子装置150产生时,具有封闭形状的第一屏蔽结构120将产生感应电流,进而产生对抗电磁辐射的磁场。

22.因此,第一屏蔽结构120可避免电感性组件110被电子装置150的外部电磁辐射所影响,或是避免电子装置150被电感性组件110漏出的电磁辐射所影响。

23.在一实施例中,如图1所示,第一屏蔽结构120具有沿一方向的延伸长度le1,电感性组件对应此方向具有侧边长度le2,其中延伸长度le1大于侧边长度le2,以达到优选的屏蔽效果。

24.在图1中,是以电感性组件110旁设置一个第一屏蔽结构120为范例进行示出。在其他实施例中,电感性组件110旁可设置多个第一屏蔽结构120。在一实施例中,多个第一屏蔽结构120的设置不仅提供电磁辐射屏蔽的功效,亦可同时作用为冗余金属区块。

25.在图1中,为使图面清楚,是将第一屏蔽结构120与电感性组件110之间以较远的间隔距离di绘制。实际上,在彼此未接触的情形下,第一屏蔽结构120与电感性组件110间的距离di愈近,提供的屏蔽效果愈佳,且不会对电感性组件110造成过大的影响。在一实施例中,第一屏蔽结构120与电感性组件110间的距离di优选地为2微米(μm)。

26.在集成电路中,电感性的电路组件容易彼此耦合造成影响。特别是当电感性组件为电压控制振荡器或是功率放大器时,容易产生影响其他电路操作的电磁辐射。在部分技术中,是使用具有封闭形状的屏蔽结构围绕整个电感性组件。这样的方式虽然提供电磁屏蔽的功效,在屏蔽结构与电感性组件的间距较小时,却会对电感性组件的质量因子造成影响,使电感性组件的操作效能下降。然而,如果将间距拉大,又将造成电路面积过大。

27.因此,本发明的电感性装置100可通过具有封闭形状的第一屏蔽结构120,设置于会互相造成影响的电感性组件110以及电子装置150间,在提供电磁屏蔽的功效的同时,维持电感性组件110的质量因子,而不对电感性组件的操作效能造成影响。并且,第一屏蔽结构120可以较小的距离邻设于电感性组件110旁,维持较小的电路面积。

28.在一实施例中,电感性组件110是如图1所示为8字形电感或8字形变压器。在这样的状况下,由于8字形电感同时包含顺时针以及逆时针的绕线方向,在第一屏蔽结构120中产生的感应电流将互相抵消。因此,电感性装置100仅需在电感性组件110的一侧设置第一屏蔽结构120,即可达到提供电磁屏蔽的功效,且不会影响电感性组件110的质量因子。

29.类似地,当电子装置150产生电磁辐射,使第一屏蔽结构120产生对应的感应电流,且此感应电流的电磁辐射亦耦合到8字形电感时,8字形电感亦可因为上述的绕线方式而不受影响。

30.在另一实施例中,电感性组件110可为其他同样具有对称结构的电感性组件,例如但不限于对偶(twins)电感。

31.请参照图2。图2示出本发明的一实施例中,一种具有电磁辐射屏蔽机制的电感性装置200的俯视图。类似于图1中的电感性装置100,图2的电感性装置200包含电感性组件110以及第一屏蔽结构120。然而在本实施例中,电感性装置200还包含第二屏蔽结构130。其中,第二屏蔽结构130亦具有封闭形状。

32.在一实施例中,电感性组件110为非8字形电感。在这样的状况下,如果仅设置第一屏蔽结构120,依其结构的不同可能会对质量因子的影响具有0%至20%的下降量。因此,除了设置第一屏蔽结构120外,优选的方式是将第二屏蔽结构130邻设于电感性组件110相对第一屏蔽结构120的另一侧,以维持电感性组件110的对称性。优选地,第二屏蔽结构130与电感性组件110间的距离,和第一屏蔽结构120与电感性组件110间的距离相同,以维持对称性。

33.在一实施例中,电感性组件110亦可为金属导线,其在进行传递时,将产生磁场而同样具有电感性。通过第一屏蔽结构120的设置,亦可达到对电感性组件110进行电磁辐射屏蔽的功效。

34.在不同的实施例中,上述第一屏蔽结构120可设置于相对电感性组件110的不同位置。

35.举例而言,在一实施例中,电感性组件110设置在一个电路层中。第一屏蔽结构120可选择性地设置于与电感性组件110相同电路层中的同一平面或不同平面。在另一实施例中,第一屏蔽结构120与电感性组件110形成于不同电路层。在又一实施例中,第一屏蔽结构120可包含形成于不同电路层的不同单元。

36.请参照图3。图3示出本发明的一实施例中,图1的电感性装置100沿a方向的侧视图。

37.在一实施例中,电感性装置100是设置于电路层300中,且电路层300上具有邻接的另一电路层310。在一实施例中,电路层300以及电路层310分别为重布层(redistribution layer;rdl)以及超厚金属层(ultra thick metal layer;utm)。

38.在一实施例中,第一屏蔽结构120实际上包含分别具有封闭形状的第一屏蔽单元320以及第二屏蔽单元330,第一屏蔽单元320以及第二屏蔽单元330分别与电感性组件110形成于相同以及不同的电路层。更详细地说,第一屏蔽单元320设置于电路层300,第二屏蔽单元330设置于电路层310。

39.因此,本案的电感性装置可视需求配置于不同的位置,达到最佳的电磁辐射屏蔽效果。

40.请参照图4。图4示出本发明一实施例中,在电子装置150操作于不同操作频率下,电感性装置100中的电感性组件110的一端点所测量到电子装置150产生的电磁辐射耦合量的示意图。其中,图4的横轴表示单位为吉赫(ghz)的频率,纵轴表示单位为分贝(db)的耦合量。

41.图4示出四个不同的线段la1至la4。其中,以粗实线绘制的线段la1表示设置第一屏蔽结构120在电感性组件110的一侧的情形下,电感性组件110测量到电子装置150分别以端点160以及165作为信号输入端以及信号输出端来操作时产生的电磁辐射耦合量。

42.以粗虚线绘制的线段la2表示未设置第一屏蔽结构120在电感性组件110的一侧的情形下,电感性组件110测量到电子装置150分别以端点160以及165作为信号输入端以及信号输出端来操作时产生的电磁辐射耦合量。

43.两者相较下,在频率为5吉赫时,电磁辐射耦合量在设置第一屏蔽结构120的情形比未设置第一屏蔽结构120的情形降低了7db。

44.进一步地,以细实线绘制的线段la3表示设置第一屏蔽结构120在电感性组件110的一侧的情形下,电感性组件110测量到电子装置150分别以端点165以及160作为信号输入端以及信号输出端来操作时产生的电磁辐射耦合量。

45.以细虚线绘制的线段la4表示未设置第一屏蔽结构120在电感性组件110的一侧的情形下,电感性组件110测量到电子装置150分别以端点165以及160作为信号输入端以及信号输出端来操作时产生的电磁辐射耦合量。

46.两者相较下,在频率为5吉赫时,电磁辐射耦合量在设置第一屏蔽结构120的情形比未设置第一屏蔽结构120的情形降低了3db。

47.请参照图5。图5示出本发明一实施例中,电感性组件110分别在不同屏蔽结构的设置下,所测量到电子装置150产生的电磁辐射耦合量的示意图。其中,图5的横轴表示单位为吉赫的频率,纵轴表示单位为分贝的耦合量。

48.图5示出三个不同的线段lb1至lb3。其中,以细实线绘制的线段lb1表示电感性组件110未设置任何屏蔽结构的情形。以粗虚线绘制的线段lb2表示电感性组件110旁设置有仅位于单一电路层的第一屏蔽结构120的情形。以粗实线绘制的线段lb3表示电感性组件110旁设置有包含分别位于不同电路层(例如图3中的电路层300及310)的屏蔽单元(例如图3中的第一屏蔽单元320以及第二屏蔽单元330)的第一屏蔽结构120的情形。

49.如图5所示,在设置有愈多屏蔽单元的情形下,电感性组件110所受到电子装置150产生的电磁辐射耦合量愈少。

50.综上所述,第一屏蔽结构120可对电子装置150产生的电磁辐射达到约2db至7db的屏蔽量。

51.请参照图6。图6示出本发明一实施例中,一种电感性装置制造方法600的流程图。

52.除前述装置外,本发明另披露一种电感性装置制造方法600,应用以制造例如,但不限于图1的电感性装置100。电感性装置制造方法600的一实施例如图6所示,包含下列步骤:

53.在步骤s610:形成电感性组件110。

54.在步骤s620:对电感性组件110进行电磁辐射测试。

55.在步骤s630:判断与电感性组件110以及电子装置150间相关的电磁辐射量是否超过辐射临界值。

56.在步骤s640:当与电感性组件110以及电子装置150间相关的电磁辐射量超过辐射临界值时,形成具有封闭形状的第一屏蔽结构120,其中第一屏蔽结构120邻设于电感性组件110的一侧,并位于电感性组件110以及电子装置150间,以使电感性组件110的质量因子的下降量不大于第一预设值,且电磁辐射屏蔽量不小于第二预设值。

57.在步骤s650:当与电感性组件110以及电子装置150间相关的电磁辐射量并未超过辐射临界值时,不形成第一屏蔽结构120。

58.需注意的是,上述的实施方式仅为一范例。在其他实施例中,本领域的普通技术人员可在不违背本发明的精神下进行更动。

59.综合上述,本发明中具有电磁辐射屏蔽机制的电感性装置及其制造方法可通过具有封闭形状的第一屏蔽结构,设置于会互相造成影响的电感性组件以及电子装置间,在提供电磁屏蔽的功效的同时,不对电感性组件的操作效能造成影响,并维持较小的电路面积。

60.虽然本发明的实施例如上所述,然而该些实施例并非用来限定本发明,本技术领域普通技术人员可依据本发明的明示或隐含的内容对本发明的技术特征施以变化,凡此种种变化均可能属于本发明所寻求的专利保护范畴,换言之,本发明的专利保护范围须视本说明书的权利要求所界定者为准。

61.【符号说明】

62.100:电感性装置

63.110:电感性组件

64.120:第一屏蔽结构

65.125:封闭区域

66.130:第二屏蔽结构

67.150:电子装置

68.160、165:端点

69.200:电感性装置

70.300、310:电路层

71.320:第一屏蔽单元

72.330:第二屏蔽单元

73.600:电感性装置制造方法

74.s610至s650:步骤

75.a:方向

76.di:距离

77.la1至la4:线段

78.lb1至lb3:线段

79.le1:延伸长度

80.le2:侧边长度。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1