一种高速ATE测试板及制作方法与流程

一种高速ate测试板及制作方法

技术领域

[0001]

本发明涉及半导体测试领域,尤指一种高速ate测试板及制作方法。

背景技术:

[0002]

ate(automatic test equipment)测试板,是半导体测试板里面的一种,也俗称loard board,负载测试板or负载基板,是半导体测试环节里面用到的一种基板,用于搭载ic在测试机上测试ic相关性能。

[0003]

随着67g甚至更高112g的高速传输技术和数字无线处理技术的发展,故对ate测试板在高速方面的可测试性能也提出了更高的要求,除了对ate测试板本身的材料在高速方面的要求外,更重要的是对高速加工控制的要求。传统高速ate测试板在设计过程,如果需要使用到高速信号(如32g及以下),设计上通常是通孔+控深钻孔(背钻)的形式制作,这种方式较为保险,但是由于控深钻孔(背钻)的技术受限,因此无法满足非常好的背钻残桩控制。

[0004]

通常的高速ate测试板一般是在多层高板厚形成的基础上,先打通孔,然后通过控深钻孔(背钻)的形式制作,将高速环回路径上多余的铜钻掉,减少损耗影响,但随着高速速率的日渐往上,对控深钻孔(背钻)的残桩控制要求也越来越严格,需要的残桩长度越来越小。

[0005]

现有技术的高速ate测试板制作流程一般为:内层图形制作

→

压合成多层板

→

钻高速过孔

→

孔金属化

→

塞孔

→

磨板

→

钻其他孔

→

孔金属化

→

正常外层图形制作

→

表面处理

→

控深钻孔(背钻)

→

正常剩余流程。

[0006]

此种方法,针对32g以下的高速测试其是可适用的。当高速需求越来越高时,其对控深钻孔(背钻)的要求很高,残桩长度需要很小,因此,在生产过程中可能会存在以下2点隐患:(1)因为背钻深度较深,背钻孔易形成从上到下的偏位,导致底部残铜较多,增大信号传输干扰,损耗偏大(如图2左边示例);(2)同样因为背钻深度较深,背钻孔从上到下的深度未能达到理论背钻深度,因此底部两边的残铜会严重偏多,同样损耗偏大(如图2右边示例)。

技术实现要素:

[0007]

本发明的目的是提供一种高速ate测试板及制作方法,该方法通过避免经过“控深钻孔(背钻)”的流程,有效地改善了高速ate测试板高速过孔背钻加工时引入的背钻残桩过长或背钻偏位问题,也消除了高速性能问题。

[0008]

本发明提供的技术方案如下:

[0009]

一种高速ate测试板制作方法,包括步骤:

[0010]

通过导电胶将单层板压合以及高速过孔形成第一高速子板,以及所述第一高速子板对称的第二高速子板;

[0011]

将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行

外层图形制作形成高速ate测试板。

[0012]

进一步优选地,所述通过导电胶将所述单层板压合以及高速过孔形成第一高速子板,包括步骤:

[0013]

对通过导电胶压合后的所述单层板进行所述高速过孔、过孔金属化、过孔塞孔、磨板、底层图形制作形成第一高速子板;

[0014]

其中,所述单层板为浸润板。

[0015]

进一步优选地,所述通过导电胶将所述单层板压合以及高速过孔形成与所述第一高速子板对称的所述第二高速子板,具体包括步骤:

[0016]

在所述第一高速子板上压合至少一个所述单层板形成预处理的所述第二高速子板;

[0017]

对预处理的所述第二高速子板和所述第一高速子板进行所述高速过孔、过孔金属化、通过导电胶进行过孔塞孔、磨板形成第二高速子板。

[0018]

进一步优选地,所述通过导电胶将所述单层板压合以及高速过孔形成与所述第一高速子板对称的所述第二高速子板,具体包括步骤:

[0019]

通过导电胶压合后的所述单层板形成预处理的所述第二高速子板;

[0020]

对预处理的所述第二高速子板进行所述高速过孔、过孔金属化、过孔塞孔、磨板形成第二高速子板。

[0021]

进一步优选地,所述通过导电胶压合后的所述单层板形成预处理的所述第二高速子板,具体包括步骤:

[0022]

通过芯板和浸润板互相层叠压合形成预处理的所述第二高速子板。

[0023]

进一步优选地,所述将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行外层图形制作形成高速ate测试板,具体包括步骤:

[0024]

对压合后的所述第一高速子板和所述第二高速子板进行钻孔、沉铜、电镀;

[0025]

对所述第二高速子板外层图形转移、镀金或硬金、外层蚀刻、外层aoi以进行所述外层图形的制作。

[0026]

进一步优选地,在所述通过导电胶将单层板压合以及高速过孔形成第一高速子板之前,还包括步骤:

[0027]

利用pcb板制作所述高速ate测试板中的单层板。

[0028]

进一步优选地,所述利用pcb板制作所述高速ate测试板中的单层板,包括步骤:

[0029]

通过开料、高速线路的内层图形转移、内层蚀刻、内层aoi、棕化以进行内层图形制作,并进行第一高速过孔,以形成盲孔或埋孔;

[0030]

通过过孔金属化、过孔塞孔、磨板、底层图形制作以形成所述单层板。

[0031]

进一步优选地,在所述将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行外层图形制作形成高速ate测试板之后,还包括步骤:

[0032]

对所述高速ate测试板进行阻焊、字符、外形、电子测试、终检、包装。

[0033]

另一方面,本发明还提供一种高速ate测试板,通过所述高速ate测试板制作方法制作而成。

[0034]

本发明提供的一种高速ate测试板及制作方法,具有以下有益效果:

[0035]

1)本发明通过避免经过“控深钻孔(背钻)”的流程,有效地改善了高速ate测试板

高速过孔背钻加工时引入的背钻残桩过长或背钻偏位问题,也消除了高速性能问题。

[0036]

2)在本发明中,通过导电胶相连,即保障了导通性,也避免了残桩长度控制。

[0037]

3)在本实施例中,层压采用导电胶,必要时可采用任意层导电胶互连。

[0038]

4)通过将多层板2下半部分再拆分成和多层板1对层的子板,可有效进一步改善最终的翘曲,增强可靠性。

附图说明

[0039]

下面将以明确易懂的方式,结合附图说明优选实施方式,对一种高速ate测试板及制作方法的上述特性、技术特征、优点及其实现方式予以进一步说明。

[0040]

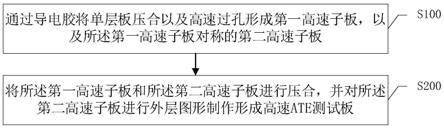

图1是本发明一种高速ate测试板制作方法的一个实施例的流程图;

[0041]

图2是现有技术中高速ate测试板的结构示意图;

[0042]

图3是本发明中高速ate测试板的结构示意图;

[0043]

图4是本发明中高速ate测试板的示意图;

[0044]

图5是本发明中一种高速ate测试板制作方法的一个实施例的流程图;

[0045]

图6是本发明中一种高速ate测试板制作方法的一个实施例的流程图。

具体实施方式

[0046]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对照附图说明本发明的具体实施方式。显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图,并获得其他的实施方式。

[0047]

为使图面简洁,各图中只示意性地表示出了与本发明相关的部分,它们并不代表其作为产品的实际结构。另外,以使图面简洁便于理解,在有些图中具有相同结构或功能的部件,仅示意性地绘示了其中的一个,或仅标出了其中的一个。在本文中,“一个”不仅表示“仅此一个”,也可以表示“多于一个”的情形。

[0048]

实施例一

[0049]

本发明的一个实施例,如图1、3所示,一种高速ate测试板制作方法,包括步骤:

[0050]

s100通过导电胶将单层板压合以及高速过孔形成第一高速子板,以及所述第一高速子板对称的第二高速子板。

[0051]

s200将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行外层图形制作形成高速ate测试板。

[0052]

具体的,导电胶是一种固化或干燥后具有一定导电性的胶粘剂。导电粒子间的相互接触形成导电通路,使导电胶具有导电性,胶层中粒子间的稳定接触是由于导电胶固化或干燥造成的。导电胶在固化或干燥前,导电粒子在胶粘剂中是分离存在的,相互间没有连续接触,因而处于绝缘状态。导电胶固化或干燥后,由于溶剂的挥发和胶粘剂的固化而引起胶粘剂体积的收缩,使导电粒子相互间呈稳定的连续状态,因而表现出导电性。

[0053]

需要说明的是,ate测试板是pcb板,尺寸很大500mm,分多层制作,一次压合。

[0054]

在本实施例中,使用导电胶对层板进行压合可以使得层板之间导通,或者任意层互联。

[0055]

在本实施例中,一般用的材质是bt/abf/pi,pcb产品一般用fr4 fr5 fr6等,pcb瞳孔电镀导通,是孔内填塞导电物质导通。

[0056]

示例性的,如图3所示,所述第一高速子板为多层板1,多层板1通过导电胶与第二高速子板压合形成多层板2,一般之前制作的多层板2中单层板的线路均为内层线路,未制作外层线路,故需要外层图形制作。多层板1在于高速线路层存在多层,故只有通过多层板1的形式才能排布所有的高速走线。

[0057]

在本实施例中,通过把原来的高速层拆分出来,形成高速子板层,避免经过“控深钻孔(背钻)”的流程,有效地改善了高速ate测试板高速过孔背钻加工时引入的背钻残桩过长或背钻偏位问题,也消除了高速性能问题。

[0058]

实施例二

[0059]

本发明的一个实施例,如图3~5所示,一种高速ate测试板制作方法,在本实施例中,关于步骤s100所述通过导电胶将所述单层板压合以及高速过孔形成第一高速子板,具体包括步骤:

[0060]

s101对通过导电胶压合后的所述单层板进行所述高速过孔、过孔金属化、过孔塞孔、磨板、底层图形制作形成第一高速子板;其中,所述单层板为浸润板。

[0061]

示例性的,如图3所示,其中pp(prepreg)为浸润板,它是一种半固化片,又称预浸材料,是用树脂浸渍并固化到中间程度(b阶)的薄片材料。半固化片可用作多层印制板的内层导电图形的黏结材料和层间绝缘。在层压时,半固化片的环氧树脂融化、流动、凝固,将各层电路毅合在一起,并形成可靠的绝缘层。

[0062]

示例性的,如图3所示,所述通过导电胶将所述单层板压合以及高速过孔形成与所述第一高速子板对称的所述第二高速子板,具体包括步骤:

[0063]

s102在所述第一高速子板上压合至少一个所述单层板形成预处理的所述第二高速子板;对预处理的所述第二高速子板和所述第一高速子板进行所述高速过孔、过孔金属化、通过导电胶进行过孔塞孔、磨板形成第二高速子板。

[0064]

传统的2层core堆叠技术简单,成本低,但是受限制较大,不可以做小pitch,高密度,布线密度低,电性也差,很多产品的要求用传统pcb工艺做不出来。

[0065]

优选地,所述通过导电胶压合后的所述单层板形成预处理的所述第二高速子板,具体包括步骤:

[0066]

通过芯板和浸润板互相层叠压合形成预处理的所述第二高速子板。

[0067]

示例性的,如图4所示,其中,core为芯板,芯板是一种硬质的、有特定厚度的、两面包铜的板材,是构成印制板的基础材料。

[0068]

在本实施例中,多层板是由芯板和半固化片互相层叠压合而成的。而半固化片构成所谓的浸润层,起到粘合芯板的作用,虽然也有一定的初始厚度,但是在压制过程中其厚度会发生一些变化。

[0069]

多层板最外面的两个介质层都是浸润层,在这两层的外面使用单独的铜箔层作为外层铜箔。外层铜箔和内层铜箔的原始厚度规格,一般有0.5oz、1oz、2oz(1oz约为35um或1.4mil)三种,但经过一系列表面处理后,外层铜箔的最终厚度一般会增加将近1oz左右。内层铜箔即为芯板两面的包铜,其最终厚度与原始厚度相差很小,但由于蚀刻的原因,一般会减少几个um。

[0070]

优选地,所述将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行外层图形制作形成高速ate测试板,具体包括步骤:

[0071]

s201对压合后的所述第一高速子板和所述第二高速子板进行钻孔、沉铜、电镀;对所述第二高速子板外层图形转移、镀金或硬金、外层蚀刻、外层aoi以进行所述外层图形的制作。

[0072]

在本实施例中,先制作一个2-4层核心板通孔,电镀,线路,然后增层压合,每次压一层(2面各一层),打盲孔,电镀,线路,重复增层。通过本实施例能够满足高速ate测试版的需求。

[0073]

实施例三

[0074]

基于上述实施例,如图3、4、6所示,本发明提供一种高速ate测试板制作方法,具体包括:

[0075]

s103对通过导电胶压合后的所述单层板进行所述高速过孔、过孔金属化、过孔塞孔、磨板、底层图形制作形成第一高速子板;其中,所述单层板为浸润板。

[0076]

s104通过导电胶压合后的所述单层板形成预处理的所述第二高速子板;对预处理的所述第二高速子板进行所述高速过孔、过孔金属化、过孔塞孔、磨板形成第二高速子板。

[0077]

s200将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行外层图形制作形成高速ate测试板。

[0078]

具体的,在本实施例中,通过分别制作第一高速子板和第二高速子板,然后通过导电胶进行压合,由于之前就已经进行了高速过孔和塞孔,层与层之间已经选择性的导通了,因此在压合时不需要再次钻孔,直接通过导电胶就可以使得高速子板之间导通,以形成高速ate测试板。

[0079]

实施例四

[0080]

基于上述实施例,在本实施例中,在所述通过导电胶将单层板压合以及高速过孔形成第一高速子板之前,还包括步骤:

[0081]

利用pcb板制作所述高速ate测试板中的单层板。

[0082]

具体的,通过开料、高速线路的内层图形转移、内层蚀刻、内层aoi、棕化以进行内层图形制作,并进行第一高速过孔,以形成盲孔或埋孔;通过过孔金属化、过孔塞孔、磨板、底层图形制作以形成所述单层板。

[0083]

在所述将所述第一高速子板和所述第二高速子板进行压合,并对所述第二高速子板进行外层图形制作形成高速ate测试板之后,还包括步骤:对所述高速ate测试板进行阻焊、字符、外形、电子测试、终检、包装。

[0084]

实施例五

[0085]

基于上述实施例,如图3所示,本发明还提供一种高速amt测试板制作方法的另一个实施例,包括:

[0086]

(1)该方法的制作流程为:涉及高速走线层次的内层图形制作

→

压合成多层板1

→

采用激光孔或机械盲孔的形式形成多阶高速过孔

→

多层板1常规流程制作

→

第二次压合成多层板2(中间添加导电胶)

→

正常外层图形制作。

[0087]

(2)多层板1可以进行多次压合,也可以通过多次导电胶进行一次压合。

[0088]

(3)控制好多层板1和其余层次压合在一起形成多层板2的涨缩控制,以避免最后

形成翘曲,影响最终成品可靠性。

[0089]

(4)其他控制要点与现有的高速ate测试板制造技术控制点类似。

[0090]

具体的生产流程为:开料

→

涉及高速层次的内层图形转移

→

内层蚀刻

→

内层aoi

→

棕化

→

层压(压合成多层板1)

→

高速过孔制作(机械or激光均可)

→

过孔金属化

→

过孔塞孔

→

磨板

→

多层板1底层图形制作

→

导电胶制作

→

层压(压合成多层板2)

→

钻孔

→

沉铜

→

全板电镀

→

外层图形转移

→

镀金/硬金

→

外层蚀刻

→

外aoi

→

阻焊

→

字符

→

外形

→

电子测试

→

终检

→

包装、出货。

[0091]

此实施例所制作的印制电路板,避免了“控深钻孔(背钻)”的流程,可涉及多层高速线路的ate测试板,不仅仅局限于图示的区域和层次。

[0092]

此流程避免了“控深钻孔(背钻)”流程,即把原来的高速层拆分出来,形成高速子板层。

[0093]

现有做法下,控制控深钻孔(背钻)的残桩长度是一个非常头疼的问题,良率较低。此种流程下,通过导电胶相连,即保障了导通性,也避免了残桩长度控制。

[0094]

同时,层压采用导电胶,必要时可采用任意层导电胶互连。若多层板2下半部分再拆分成和多层板1对层的子板,可有效进一步改善最终的翘曲,增强可靠性。

[0095]

另一方面,如图4所示,本发明还提供一种高速ate测试板,通过所述高速ate测试板制作方法制作而成。

[0096]

此实施例所制作的印制电路板,避免了“控深钻孔(背钻)”的流程,可涉及多层高速线路的ate测试板,不仅仅局限于图示的区域和层次。

[0097]

应当说明的是,上述实施例均可根据需要自由组合。以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1