电流导向式比较器与电容控制方法与流程

1.本案是关于比较器电路,尤其是关于具有动态偏置的电流导向式比较器与电容控制方法。

背景技术:

2.比较器电路常应用于量化器来将模拟信号转换为数字信号。为了达到高分辨率,比较器电路需具有较佳的噪声表现。为了达到高转换率,比较器电路需具有较快的操作速度。然而,在现有的比较器电路中,噪声表现往往相反于操作速度。再者,由于制程/电压/温度变异,比较器电路的内部节点的电平不容易精准控制,导致较难以掌握比较器电路的效能。

技术实现要素:

3.在一些实施例中,电流导向式比较器包括放大器电路、偏置电路、锁存器电路以及检测电路。放大器电路用以在一比较期间比较一第一输入信号与一第二输入信号,以输出一第一信号与一第二信号。偏置电路用以在该比较期间利用一可调电容偏置该放大器电路。锁存器电路用以在该比较期间根据该第一信号与该第二信号产生一第一输出信号与一第二输出信号。检测电路用以根据一预设频率信号检测该第一输出信号与该第二输出信号以产生一控制信号,以调整该可调电容。

4.在一些实施例中,电容控制方法包括下列操作:藉由具有一可调电容的一偏置电路在一比较期间偏置一电流导向式比较器的一放大器电路,其中该放大器电路在该比较期间比较一第一输入信号与一第二输入信号以输出一第一信号与一第二信号,且该电流导向式比较器中的一锁存器电路在该比较期间根据该第一信号与该第二信号产生一第一输出信号与一第二输出信号;以及根据一预设频率信号检测该第一输出信号与该第二输出信号以产生一控制信号,以调整该可调电容。

5.有关本案的特征、实作与功效,将配合附图作较佳实施例详细说明如下。

附图说明

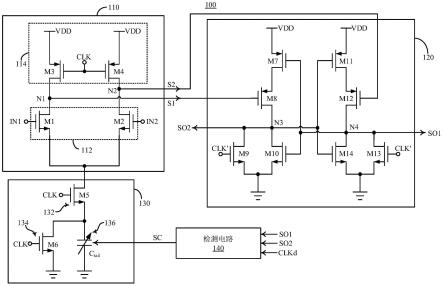

6.图1为根据本案一些实施例示出的一种电流导向式比较器的示意图;

7.图2为根据本案一些实施例示出图1中的电容阵列电路的示意图;

8.图3a为根据本案一些实施例示出图1中的检测电路的示意图;

9.图3b为根据本案一些实施例示出图1中的频率信号与预设频率信号的波形示意图;以及

10.图4为根据本案一些实施例示出一种电容控制检测方法的流程图。

具体实施方式

11.本文所使用的所有词汇具有其通常的意涵。上述的词汇在普遍常用的字典中的定

义,在本案的内容中包括任一在此讨论的词汇所使用例子仅为示例,不应限制到本案的范围与意涵。同样地,本案也不仅以在此说明书所示出的各种实施例为限。

12.关于本文中所使用的“耦接”或“连接”,均可指二或多个组件相互直接作实体或电性接触,或是相互间接作实体或电性接触,也可指二或多个组件相互操作或动作。如本文所用,用语“电路系统(circuitry)”可为由至少一电路(circuit)所形成的单一系统,且用语“电路”可为由至少一个晶体管与/或至少一个主被动组件按一定方式连接以处理信号的装置。

13.如本文所用,用语“与/或”包括了列出的关联项目中的一个或多个的任何组合。在本文中,使用第一、第二与第三等等的词汇,是用于描述并辨别各个组件。因此,在本文中的第一组件也可被称为第二组件,而不脱离本案的本意。为易于理解,在各附图中的类似组件将被指定为相同标号。

14.图1为根据本案一些实施例示出的一种电流导向式(current steering)比较器100的示意图。在一些实施例中,电流导向式比较器100可应用于各种电路系统(例如可为,但不限于、数字模拟转换器电路系统与模拟数字转换器电路系统)。

15.电流导向式比较器100包括放大器电路110、锁存器电路120、偏置电路130以及检测电路140。放大器电路110用以在比较期间比较输入信号in1以及输入信号in2,以产生信号s1以及信号s2。锁存器电路120用以在比较期间根据信号s1以及信号s2产生输出信号so1以及输出信号so2。偏置电路130具有一可调电容c

tail

,其可用来降低放大器电路110的噪声。偏置电路130用以在比较期间利用可调电容c

tail

偏置放大器电路110。在一些实施例中,前述的比较期间可为频率信号clk为高电平的期间。

16.详细而言,放大器电路110可包括输入对电路112以及重置电路114。输入对电路112用以在比较期间比较输入信号in1以及输入信号in2,以经由节点n1输出信号s1,并经由节点n2输出信号s2。重置电路114用以在重置期间将节点n1的电平调整至预设电平(例如为电压vdd),并将节点n2的电平调整至该预设电平。在一些实施例中,前述的重置期间可为频率信号clk具有低电平的期间。

17.例如,输入对电路112包括晶体管m1以及晶体管m2。晶体管m1的控制端(例如为栅极)接收输入信号in1。晶体管m1的第一端(例如为漏极)耦接至节点n1。晶体管m1的第二端(例如为源极)耦接至偏置电路130。晶体管m2的控制端接收输入信号in2。晶体管m2的第一端耦接至节点n2。晶体管m2的第二端耦接至偏置电路130。重置电路114包括晶体管m3以及晶体管m4。晶体管m3的第一端(例如为源极)以及晶体管m4的第一端接收电压vdd。晶体管m3的第二端(例如为漏极)耦接至节点n1,且晶体管m4的第二端耦接至节点n2。晶体管m3的控制端与晶体管m4的控制端接收频率信号clk。

18.在重置期间(例如为频率信号clk具有低电平的期间),晶体管m3与晶体管m4导通,以将电压vdd传输至节点n1以及节点n2。在此条件下,节点n1的电平以及节点n2的电平可被重置至电压vdd。在比较期间(例如为频率信号clk具有高电平的期间),晶体管m3与晶体管m4不导通。在此条件下,晶体管m1以及晶体管m2可依据输入信号in1以及输入信号in2选择拉低节点n1与节点n2中的一者的电平,并保持节点n1与节点n2中的另一者的电平,以产生信号s1以及信号s2。

19.偏置电路130包括开关132、开关134以及电容阵列电路136。开关132耦接于输入对

电路112与电容阵列电路136之间,并用以在比较期间导通。开关134用以在重置期间导通,以使电容阵列电路136进行放电。电容阵列电路136用以提供可调电容c

tail

,其中可调电容c

tail

的容值可根据控制信号sc调整。

20.例如,开关132可由(但不限于)晶体管m5实施,且开关134可由(但不限于)晶体管m6实施。晶体管m5的第一端耦接至晶体管m1以及晶体管m2两者的第二端。晶体管m5的第二端耦接至电容阵列电路136。晶体管m5的控制端接收频率信号clk。晶体管m6的第一端耦接至晶体管m5的第二端。晶体管m6的第二端耦接至地。晶体管m6的控制端接收频率信号clk'。频率信号clk'的相位与频率信号clk的相位相差180度。换言之,若频率信号clk具有高电平,频率信号clk'具有低电平。若频率信号clk具有低电平,频率信号clk'具有高电平。

21.在频率信号clk具有低电平的期间(即重置期间),晶体管m6导通,以使电容阵列电路136进行放电。在此条件下,可调电容c

tail

上的电压为地电压。在重置期间,晶体管m3与晶体管m4导通,以对耦接至节点n1的寄生电容(未示出)以及耦接至节点n2的寄生电容(未示出)进行充电。在频率信号clk具有高电平的期间(即比较期间),晶体管m5导通且晶体管m6不导通。如此,耦接至节点n1与节点n2的寄生电容开始放电,以对可调电容c

tail

进行充电。在此条件下,可调电容c

tail

上的电压变高,以减少晶体管m1的栅极-源极间电压,并减少晶体管m2的栅极-源极间电压。等效地,可调电容c

tail

可在比较期间内对输入对电路112提供动态偏置。藉由上述偏置方式,可以降低放大器电路110的总输入相关噪声(input referred noise)。一般而言,可调电容c

tail

的容值越低,放大器电路110的总输入相关噪声越低。然而,若容值过低,可能导致锁存器电路120的操作速度变慢。如后述说明,藉由检测电路140,可调电容c

tail

的容值可在操作速度与噪声表现之间取得较好的平衡。

22.锁存器电路120包括多个晶体管m7~m14。多个晶体管m7~m8、m10~m12以及m14形成一正反馈电路,其可用以根据信号s1与信号s2产生输出信号so1以及输出信号so2。晶体管m9以及晶体管m13在重置期间重置节点n3的电平以及节点n4的电平。例如,在重置期间,晶体管m9以及晶体管m13根据频率信号clk'导通,以将节点n3的电平与节点n4的电平拉低至地。在比较期间,若信号s1具有高电平且信号s2具有低电平,晶体管m8不导通且晶体管m12导通。在此条件下,节点n4的电平被拉升至电压vdd,以输出具有高电平的输出信号so1。响应于节点n4的电平,晶体管m7不导通且晶体管m10导通以将节点n3的电平拉低至地,以输出具有低电平的输出信号so2。

23.上述关于放大器电路110、锁存器电路120以及偏置电压130的设置方式用于示例,且本案并不以此为限。在一些实施例中,多个晶体管m1、m2、m5、m6、m9、m10、m13以及m14可为n型晶体管,且多个晶体管m3、m4、m7、m8、m11以及m12可为p型晶体管。在一些实施例中,上述各个晶体管可由金属氧化物场效晶体管(mosfet)实施,但本案并不以此为限。可实施类似操作的各种类型的晶体管皆为本案所涵盖的范围。

24.检测电路140用以根据预设频率信号clkd检测输出信号so1与输出信号so2,以产生控制信号sc。在一些实施例中,检测电路140可在放大器电路110根据频率信号clk进入比较期间后的一预设期间(例如为图3b的预设期间t)检测输出信号so1以及输出信号so2,以确认放大器电路110以及锁存器电路120两者的操作速度是否符合预设要求。若操作速度不符合预设要求,检测电路140可输出对应的控制信号sc,以调整可调电容c

tail

的容值。藉由调整可调电容c

tail

的容值,可调整放大器电路110以及锁存器电路120两者的操作速度。

25.在一些相关技术中,具有固定容值的电容被用来实施偏置电路。在此些技术中,由于制程变异、电压变异与/或温度变异,输入对电路的多个(例如为晶体管m1以及晶体管m2)的临界电压以及电源电压(例如为电压vdd)都会出现偏移。如此一来,无法准确地控制该电容的容值与比较器电路的内部节点(例如为节点n1与节点n2)的电平,导致电路操作可能失效或是影响下一级电路(例如为锁存器电路120)的操作。相较于上述相关技术,在本案的一些实施例中,藉由设置电容阵列电路136,检测电路140可依据输出信号so1以及输出信号so2确认放大器电路110以及锁存器电路120的操作速度。若操作速度不符合预设要求,检测电路140可输出控制信号sc,以调整可调电容c

tail

的容值。如此一来,在制程变异、电压变异与/或温度变异的影响下,电流导向式比较器100的效能仍可符合预设要求。

26.图2为根据本案一些实施例示出图1中的电容阵列电路136的示意图。电容阵列电路136包括多个电容c以及多个开关sw。多个开关sw分别耦接至多个电容c,并根据控制信号sc选择性导通。例如,第一个开关sw接收控制信号sc的第一个位[0],第二个开关sw接收控制信号sc的第二个位[1],且第三个开关sw接收控制信号sc的第三个位[2]。依此类推,应可理解多个开关sw与控制信号sc的多个位之间的对应关系。

[0027]

在图1的例子中,由于晶体管m8与晶体管m12为p型晶体管,节点n1的电平与节点n2的电平会直接影响锁存器电路120的操作速度。例如,节点n1的电平越低,晶体管m8的驱动电流越大,故操作速度会提升。反之,节点n1的电平越高,晶体管m8的驱动电流越小,故操作速度会降低。若检测电路140判断放大器电路110以及锁存器电路120两者的操作速度过慢,检测电路140可输出对应的控制信号sc,以使更多的开关sw导通。在此条件下,可调电容c

tail

的容值增加,以降低节点n1的电平与节点n2的电平。如此,可提升锁存器电路120的操作速度。或者,若检测电路140判断操作速度过快,检测电路140可输出对应的控制信号sc,以使更多的开关sw不导通。在此条件下,可调电容c

tail

的容值降低,以提升节点n1的电平与节点n2的电平。如此,可降低锁存器电路120的操作速度。

[0028]

图3a为根据本案一些实施例示出图1中的检测电路140的示意图,且图3b为根据本案一些实施例示出图1中的频率信号clk与预设频率信号clkd的波形示意图。检测电路140包括逻辑门电路310、正反器电路320以及处理电路330。逻辑门电路310用以根据输出信号so1以及输出信号so2产生检测信号sd1。在图3a的例子中,逻辑门电路310可为非或门电路。在其他实施例中,根据放大器电路110的设置方式,逻辑门电路310可为(但不限于)互斥或门电路、非与门电路等等。

[0029]

如前所述,在重置期间,图1中的节点n3的电平以及节点n4的电平重置为地电压。因此,在重置期间,逻辑门电路310可输出具有逻辑值1的检测信号sd1。若放大器电路110与锁存器电路120可在比较期间产生比较结果,依据不同的比较结果,节点n3与节点n4中的一者会具有高电平(即输出信号so1与输出信号so2中的一者具有高电平),且节点n3与节点n4中的另一者会具有高电平(即输出信号so1与输出信号so2中的另一者具有高电平)。响应于输出信号so1以及输出信号so2,逻辑门电路310可输出具有逻辑值0的检测信号sd1。反之,若放大器电路110与锁存器电路120无法在比较期间产生比较结果,逻辑门电路310仍输出具有逻辑值1的检测信号sd1。

[0030]

正反器电路320用以根据预设频率信号clkd将检测信号sd1输出为检测信号sd2。正反器电路320可在放大器电路110进入比较期间后的一段预设期间t内将检测信号sd1输

出为检测信号sd2。例如,如图3b所示,频率信号clk的转态边缘(例如可为,但不限于,上升边缘)与预设频率信号clkd的转态边缘(例如可为,但不限于,上升边缘)之间具有一延迟时间td。正反器电路320可为(但不限于)d型正反器电路,其可根据预设频率信号clkd的上升边缘将检测信号sd1输出为检测信号sd2。

[0031]

处理电路330用以根据检测信号sd2判断放大器电路110与锁存器电路120两者的操作速度是否符合预设需求,以产生控制信号sc。例如,若检测信号sd2为逻辑值0,代表放大器电路110以及锁存器电路120无法在比较期间内产生比较结果(即放大器电路110以及锁存器电路120两者的操作速度过慢而不符合预设需求)。在此条件下,处理电路330可输出对应的控制信号sc以提高可调电容c

tail

的容值,以增加操作速度。或者,若检测信号sd2为逻辑值1,代表放大器电路110以及锁存器电路120能够在比较期间内产生比较结果(即放大器电路110以及锁存器电路120两者的操作速度符合预设需求)。在此条件下,处理电路330可输出对应的控制信号sc以降低可调电容c

tail

的容值。如此,可使放大器电路110的噪声进一步地降低。藉由反复地执行上述操作,可调电容c

tail

的容值可在制程变异、电压变异与/或温度变异下在操作速度与噪声表现之间取得较好的平衡。在一些实施例中,处理电路330可为微控制器电路、数字信号处理电路或其他具有处理能力的数字电路实施。在一些实施例中,前述的预设需求可根据电流导向式比较器100的实际应用决定。例如,当电流导向式比较器100应用于模拟数字转换器电路时,预设需求可根据模拟数字转换器的转换时间而定。

[0032]

图4为根据本案一些实施例示出一种电容控制方法400的流程图。在一些实施例中,电容控制方法400用于(但不限于)调整比较器电路中的一可变电容。

[0033]

在操作s410,藉由具有可调电容的偏置电路(例如为图1的偏置电路130)在比较期间偏置电流导向式比较器的放大器电路(例如为图1的放大器电路110),其中放大器电路在该比较期间比较第一输入信号与第二输入信号以输出第一信号与第二信号,且该电流导向式比较器中的锁存器电路(例如为图1的锁存器电路120)在比较期间根据第一信号与第二信号产生第一输出信号与第二输出信号。在操作s420,根据预设频率信号检测第一输出信号与第二输出信号以产生控制信号,以调整可调电容。

[0034]

上述多个操作的说明可参照前述各个实施例,故不重复赘述。上述电容控制方法400的多个操作仅为示例,并非限定需依照此示例中的顺序执行。在不违背本案的各实施例的操作方式与范围下,在电容控制方法400下的各种操作当可适当地增加、替换、省略或以不同顺序执行(例如可以是同时执行或是部分同时执行)。

[0035]

综上所述,本案一些实施例中的电流导向式比较器与电容控制方法可在制程变异、电压变异与/或温度变异下准确地调整比较器中的可变电容的容值,以在噪声表现以及操作速度之间取得较好的平衡。

[0036]

虽然本案的实施例如上所述,然而该些实施例并非用来限定本案,本技术领域普通技术人员可依据本案的明示或隐含的内容对本案的技术特征施以变化,凡此种种变化均可能属于本案所寻求的专利保护范畴,换言之,本案的专利保护范围须视本说明书的权利要求的范围为准。

[0037]

【符号说明】

[0038]

100:电流导向式比较器

[0039]

110:放大器电路

[0040]

112:输入对电路

[0041]

114:重置电路

[0042]

120:锁存器电路

[0043]

130:偏置电路

[0044]

132、134:开关

[0045]

136:电容阵列电路

[0046]

140:检测电路

[0047]

310:逻辑门电路

[0048]

320:正反器电路

[0049]

330:处理电路

[0050]

400:电容控制方法

[0051]

[0]、[1]、[2]:位

[0052]

c:电容

[0053]

clk、clk':频率信号

[0054]

clkd:预设频率信号

[0055]ctail

:可调电容

[0056]

in1、in2:输入信号

[0057]

m1~m14:晶体管

[0058]

n1~n4:节点

[0059]

s1、s2:信号

[0060]

s410、s420:操作

[0061]

sc:控制信号

[0062]

sd1、sd2:检测信号

[0063]

so1、so2:输出信号

[0064]

sw:开关

[0065]

t:预设期间

[0066]

td:延迟时间

[0067]

vdd:电压

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1