一种可观察波形的可变增益放大器的制作方法

[0001]

本实用新型涉及电子电路领域,尤其涉及一种可观察波形的可变增益放大器。

背景技术:

[0002]

虚拟的仿真设备通过fpga和adc模块实现简易示波器功能,输入波形通过可变增益放大器调整输入到adc芯片的电压大小,现有的可变增益放大器电路,不能观察输入波形和输出波形变化。

技术实现要素:

[0003]

有鉴于此,本实用新型针对上述问题,提供了一种可观察波形的可变增益放大器,在可变增益放大器模块两端添加观察点,并提供模块中间电压测试点,方便观察输入和输出波形的变化;所述一种可观察波形的可变增益放大器,包括以下:

[0004]

前级放大电路和次级放大电路;所述前级放大电路和所述次级放大电路电性连接;所述前级放大电路包括ad芯片u8;所述ad芯片u8的一个输入引脚引出为vocm_aa端,接外部可调节输入电平;两个输出引脚引出为第一 p_test接口和第二p_test接口,接示波器,用于观察输入波形;所述次级放大电路包括ad芯片u6;所述ad芯片u6的一个输出脚引出为vocm_a端,用于对外输出,提供中间电压;所述ad芯片u6的另外两个输出脚分别引出为第三p_test接口和第四p_test接口,用于观察输出波形。

[0005]

进一步地,所述前级放大电路,具体连接关系为:所述ad芯片u8的1脚与电阻r47的一端、电容c46的一端、电阻r51的一端电性连接;电阻r47的另一端与电阻r39的一端电性连接;电阻r39的另一端接地;电容c46的另一端、电阻r51的另一端与电阻r60的一端、所述ad芯片u8的4脚电性连接;电阻r60的另一端与电阻r62的一端、电容c55的一端电性连接;电阻r62的另一端作为输出信号端ina+,用于接所述次级放大电路的输入信号端ina+;电容c55的另一端接电阻r61的一端和电阻r63的一端;电阻r63的另一端接输出信号端ina-,用于接所述次级放大电路的输入信号端ina-;电阻r61的另一端与所述ad芯片u8的5脚、电阻r50的一端和电容c47的一端电性连接;电阻r50的另一端、电容c47的另一端与电阻r48的一端电性连接;电阻r48 的另一端与电阻r40的一端电性连接;电阻r40的一端还与外部输入信号bnc 接口的1脚电性连接;电阻r40的另一端与外部输入信号bnc接口的2、3、4、 5脚电性连接;所述ad芯片u8的2脚与电容c50的一端、电阻r49的一端、电阻r55的一端电性连接;电阻r49的另一端接电源vcc5;电容c50的另一端与电阻r55的另一端接地;所述ad芯片u8的3脚与电容c48的一端连接;电容c48的另一端接地;所述ad芯片u8的6脚与电容c49的一端电性连接;电容c49的另一端接地;

[0006]

进一步地,所述ad芯片u8的2脚引出为vocm_aa端,用于外接可调整的输入电平;所述电阻r62的一端引出为第一p_test接口j36;所述电阻r63 的一端引出为第二p_test接口j37;所述第一p_test接口j36和所述第二 p_test接口j37用于接示波器,观察输入波形;

[0007]

进一步地,所述次级放大电路,具体连接关系为:所述ad芯片u6的1脚与电阻r56的

一端相连;电阻r56的另一端与所述电阻62的另一端电性连接,作为输入信号端ina+;所述ad芯片u6的16脚与电阻r45的一端相连;电阻r45的另一端与所述电阻r63的另一端电性连接,输入信号ina-端;所述 ad芯片u6的2脚和7脚接地;所述ad芯片u6的3脚和4脚相连,并共同连接电容c56的一端和电源vcc5;电容c56的另一端接地;所述ad芯片u6 的5脚与电容c53的一端相连,电容c53的另一端接地;所述ad芯片u6的6 脚与电容c57的一端和电源vcc5连接;电容c57的另一端接地;所述ad芯片u6的6脚还与所述ad芯片u6的3脚、所述ad芯片u6的11脚电性连接;所述ad芯片u6的8脚与电阻r58的一端连接;所述电阻r58的另一端作为输出端cha_n;所述ad芯片u6的9脚与电阻r43的一端连接;所述电阻 r43的另一端作为输出端cha_p;所述ad芯片u6的10脚和所述ad芯片u6 的15脚连接,并共同接地;所述ad芯片u6的12脚、13脚、14脚用于接通道a的时钟信号和数据信号;

[0008]

所述ad芯片u6的5脚引出为vocm_a端,用于对外输出,提供中间电源;所述ad芯片u6的8脚引出为第三p_test接口j34,作为输出波形的一端;所述ad芯片u6的9脚引出为第四p_test接口j29,作为输出波形的另一端;所述第三p_test接口j34和所述第四p_test接口j29,用于接示波器,观察输出波形。

[0009]

本实用新型提供的有益效果是:方便观察和演示虚拟仿真设备的输入信号的波形图,并根据实际需要调整输入电平。

附图说明

[0010]

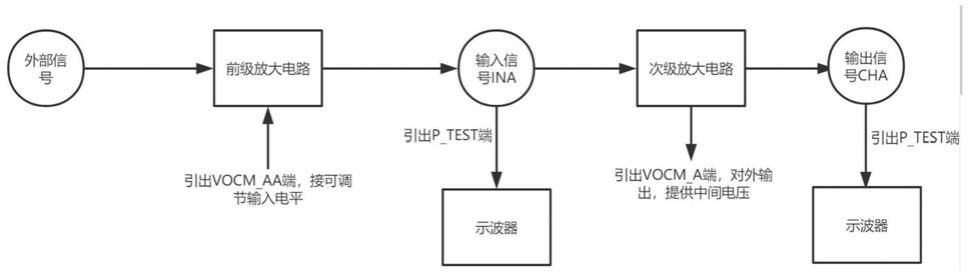

图1是本实用新型一种可观察波形的可变增益放大器连接关系示意图。

[0011]

图2是本实用新型前级放大电路原理图;

[0012]

图3是本实用新型次级放大电路原理图。

具体实施方式

[0013]

为使本实用新型的目的、技术方案和优点更加清楚,下面将结合附图对本实用新型实施方式作进一步地描述。

[0014]

请参考图1,本实用新型的实施例提供了一种可观察波形的可变增益放大器,包括以下:

[0015]

前级放大电路和次级放大电路;所述前级放大电路和所述次级放大电路电性连接;所述前级放大电路包括ad芯片u8;所述ad芯片u8的一个输入引脚引出为vocm_aa端,接外部可调节输入电平;两个输出引脚引出为第一 p_test接口和第二p_test接口,接示波器,用于观察输入波形;所述次级放大电路包括ad芯片u6;所述ad芯片u6的一个输出脚引出为vocm_a端,用于对外输出,提供中间电压;所述ad芯片u6的另外两个输出脚分别引出为第三p_test接口和第四p_test接口,用于观察输出波形。

[0016]

请参考图2,所述前级放大电路,具体连接关系为:所述ad芯片u8的1 脚与电阻r47的一端、电容c46的一端、电阻r51的一端电性连接;电阻r47 的另一端与电阻r39的一端电性连接;电阻r39的另一端接地;电容c46的另一端、电阻r51的另一端与电阻r60的一端、所述ad芯片u8的4脚电性连接;电阻r60的另一端与电阻r62的一端、电容c55的一端电性连接;电阻 r62的另一端作为输出信号端ina+,用于接所述次级放大电路的输入信号端 ina+;电容c55的另一端接电阻r61的一端和电阻r63的一端;电阻r63的另一端接输出信号端ina-,

用于接所述次级放大电路的输入信号端ina-;电阻 r61的另一端与所述ad芯片u8的5脚、电阻r50的一端和电容c47的一端电性连接;电阻r50的另一端、电容c47的另一端与电阻r48的一端电性连接;电阻r48的另一端与电阻r40的一端电性连接;电阻r40的一端还与外部输入信号bnc接口的1脚电性连接;电阻r40的另一端与外部输入信号bnc接口的2、3、4、5脚电性连接;所述ad芯片u8的2脚与电容c50的一端、电阻 r49的一端、电阻r55的一端电性连接;电阻r49的另一端接电源vcc5;电容c50的另一端与电阻r55的另一端接地;所述ad芯片u8的3脚与电容c48 的一端连接;电容c48的另一端接地;所述ad芯片u8的6脚与电容c49的一端电性连接;电容c49的另一端接地;

[0017]

,所述ad芯片u8的2脚引出为vocm_aa端,用于外接可调整的输入电平;所述电阻r62的一端引出为第一p_test接口j36;所述电阻r63的一端引出为第二p_test接口j37;所述第一p_test接口j36和所述第二p_test接口j37 用于接示波器,观察输入波形;

[0018]

请参考图3,所述次级放大电路,具体连接关系为:所述ad芯片u6的1 脚与电阻r56的一端相连;电阻r56的另一端与所述电阻62的另一端电性连接,作为输入信号端ina+;所述ad芯片u6的16脚与电阻r45的一端相连;电阻r45的另一端与所述电阻r63的另一端电性连接,输入信号ina-端;所述 ad芯片u6的2脚和7脚接地;所述ad芯片u6的3脚和4脚相连,并共同连接电容c56的一端和电源vcc5;电容c56的另一端接地;所述ad芯片u6 的5脚与电容c53的一端相连,电容c53的另一端接地;所述ad芯片u6的6 脚与电容c57的一端和电源vcc5连接;电容c57的另一端接地;所述ad芯片u6的6脚还与所述ad芯片u6的3脚、所述ad芯片u6的11脚电性连接;所述ad芯片u6的8脚与电阻r58的一端连接;所述电阻r58的另一端作为输出端cha_n;所述ad芯片u6的9脚与电阻r43的一端连接;所述电阻 r43的另一端作为输出端cha_p;所述ad芯片u6的10脚和所述ad芯片u6 的15脚连接,并共同接地;所述ad芯片u6的12脚、13脚、14脚用于接通道a的时钟信号和数据信号;

[0019]

所述ad芯片u6的5脚引出为vocm_a端,用于对外输出,提供中间电源;所述ad芯片u6的8脚引出为第三p_test接口j34,作为输出波形的一端;所述ad芯片u6的9脚引出为第四p_test接口j29,作为输出波形的另一端;所述第三p_test接口j34和所述第四p_test接口j29,用于接示波器,观察输出波形。

[0020]

所述vocm_a端和所述vocm_aa端还被引出作为接口j5;

[0021]

vocm_a和vocm_aa跳线连接时,是使用u6的vocm_a端输出的标准值;不连接时,vocm_aa端可以接外部输入可调节电平;

[0022]

通过调整前级放大电路vocm电压,可以使前级放大电路输出波形偏置电压改变,通过这样的方式可以调节可变增益放大器输入信号的垂直偏置,从而可以调整可变增益放大器模块最终输入到后级adc模块的波形;

[0023]

,在不冲突的情况下,本文中上述实施例及实施例中的特征可以相互结合。

[0024]

为了方便解释说明,本实用新型统一对电路中元器件相关规格参数解释如下:

[0025]

ad芯片u8(ad8138)、电阻r39(25r)、电阻r40(49.9r)、电阻 r47(499r)、电阻r48(499r)、电容c46(1pf)、电阻r51(499r)、电阻r49(4k)、电阻r50(499r)、电容c47(1pf)、电容50(100nf)、电阻r55(1k)、电容c48(100nf)、电容c49(100nf)、电阻r60(50r)、电阻r61(50r)、电阻r62(0r)、电容c55(15pf)、电阻r63(0r);

[0026]

ad芯片u6(ad8370)、电阻r45(50r)、电阻r43(50r)、电阻r56 (50r)、电阻r58

(50r)、电容c53(1nf)、电容c56(100nf)、电容c57 (1nf);

[0027]

在本实用新型提供的有益效果是:在可变增益放大器模块两端添加观察点,并提供模块中间电压测试点,可以根据实际需要调整输入电平,方便观察输入和输出波形的变化。

[0028]

以上所述仅为本实用新型的较佳实施例,并不用以限制本实用新型,凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1