极化码的译码方法、装置和极化码的编码方法、装置与流程

1.本公开涉及编码技术领域,特别涉及一种极化码的译码方法、极化码的译码装置、极化码的编码方法、极化码的编码装置、电子设备和非易失性计算机可读存储介质。

背景技术:

2.sc(successive-cancellation,连续取消)译码算法在译码时码元连续按顺序立即硬判决并译出,译出的过程同时也是删除的过程。

3.由于sc译码算法中后一码元的硬判决依赖于前一码元,如果前一码元译码出错,将不该删除的路径删除了,就会影响到后一码元的译码结果,并且译码错误没有机会得到纠正。

4.列表sc译码算法(scl)译码时保留出现概率最大的l条备选路径,从中选择出现概率最大的备选路径作为译码结果。

5.在相关技术中,一种译码方法将待译码码字分为等长的m个子段,各个子段独立进行scl译码,得到m个第一子段译码结果,对m个第一子段译码结果执行子段变换得到m个第二子段译码结果,m个第二子段译码结果经过位置置换后得到和待编码码元序列同序的译码结果,用scl译码过程中获得的crc(cyclic redundancy check,循环冗余校验)校验码辅助sc译码器,从l条备选路径中选出通过校验的路径作为译码结果。

技术实现要素:

6.本公开的发明人发现上述相关技术中存在如下问题:第一子段译码结果虽然包含l个备选路径,没有相应的crc校验码可用,第二子段译码结果虽然包含了crc校验码,但需要进行复杂的、计算量巨大的备选路径合并。

7.鉴于此,本公开提出了一种极化码的译码方法,包括:将待译码码元序列划分为m个长度为n的y子段,m、n为2的整次幂;对m个y子段分别进行独立的译码,得到m个a子段;根据a子段与v子段的变换关系,确定m个v子段,变换关系中每一个v子段中码元由相应的预设数量的a子段码元的异或确定;将预设数量相同的v子段拼接成一个v子段,生成k个v子段,k为正整数;利用各v子段中的校验码,对各v子段进行校验;根据校验结果,确定各v子段的译码结果。

8.在一些实施例中,k的取值为1+log2m。

9.在一些实施例中,根据校验结果,确定各v子段的译码结果包括:对于第k个v子段,在存在一条通过校验的备选路径的情况下,将通过校验的备选路径确定为第k个v子段的译码结果,在存在多条通过校验的备选路径的情况下,将出现概率最大的通过校验的备选路径确定为第k个v子段的译码结果,在不存在通过校验的备选路径的情况下,将出现概率最大的备选路径确定为第k个v子段的译码结果。

10.在一些实施例中,译码方法还包括:对于第k-1个v子段,将第k个v子段的译码结果代入变换关系,以更新变换关系;其中,根据a子段与v子段的变换关系,确定m个v子段包括:

根据更新之后的变换关系,确定m个v子段;将预设数量相同的v子段拼接成一个v子段包括:将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段;利用各v子段中的校验码,对各v子段进行校验包括:利用各v子段中的校验码,对第k-1个v子段的l条备选路径进行校验。

11.在一些实施例中,将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段包括:将第k-1个v子段中第1个v子段的l条备选路径和第2个v子段的l条备选路径进行两两拼接,得到l2条备选路径;保留出现概率最大的l条备选路径,并与第3个v子段的l条备选路径拼接,再次得到l2条备选路径;保留出现概率最大的l条备选路径;重复上述步骤,直到完成log2m个v子段的拼接,保留出现概率最大的l条备选路径作为第k-1个v子段的l条备选路径。

12.在一些实施例中,将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段包括:将log2m个v子段两两拼接,分别得到出现概率最大的l条备选路径;分别将出现概率最大的l条备选路径两两拼接,再次分别得到出现概率最大的l条备选路径;重复上述步骤,直到完成log2m个v子段的拼接,保留出现概率最大的l条备选路径作为第k-1个v子段的l条备选路径。

13.在一些实施例中,译码方法还包括:对于第k个v子段以外的v子段,将排在该v子段后面的v子段的译码结果代入变换关系,以更新变换关系;根据a子段与v子段的变换关系,确定m个v子段包括:根据更新之后的变换关系,确定m个v子段;将预设数量相同的v子段拼接成一个v子段包括:将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的该v子段;利用各v子段中的校验码,对各v子段进行校验包括:利用各v子段中的校验码,对该v子段的l条备选路径进行校验。

14.在一些实施例中,根据校验结果,确定各v子段的译码结果包括:对各v子段进行子段拆分处理、位置逆置换处理,确定译码结果,位置逆置换处理与编码侧的位置置换处理互为逆过程。

15.在一些实施例中,拼接成各v子段的v子段的数量根据a子段与v子段的变换关系确定,拼接成第1个v子段的v子段的数量为1,拼接成第k个v子段的v子段的数量为1。

16.在一些实施例中,冻结码元为0。

17.根据本公开的另一些实施例,提供一种极化码的编码方法,包括:对原始的待编码码元序列进行位置置换处理,得到m个长度为n的w子段,m、n为2的整次幂,原始的待编码码元序列包括k个全0的原始校验码;根据b子段与w子段的变换关系,将m个w子段中的码元分解为m个b子段中的码元的组合,每一个w子段中码元由相应的预设数量的b子段码元的异或确定;将预设数量相同的w子段拼接成一个w子段,生成k个w子段,k为正整数;生成各w子段的校验码,各w子段的校验码和各w子段的数据码元组成各w子段的信息码元,各w子段的信息码元和各w子段的冻结码元组成各w子段;利用各w子段的校验码替换原始的待编码码元序列中的全0原始校验码,得到待编码码元序列;对待编码码元序列进行极化码编码,得到编码码元序列,以便译码侧进行译码处理。

18.在一些实施例中,k的取值为1+log2m。

19.在一些实施例中,原始的待编码码元序列包括数据码元、冻结码元。

20.在一些实施例中,冻结码元为预设的固定值。

21.根据本公开的又一些实施例,提供一种极化码的译码装置,包括:划分单元,用于将待译码码元序列划分为m个长度为n的y子段,m、n为2的整次幂;译码单元,用于对m个y子段分别进行独立的译码,得到m个a子段,根据校验结果,确定各v子段的译码结果;确定单元,用于根据a子段与v子段的变换关系,确定m个v子段,变换关系中每一个v子段中码元由相应的预设数量的a子段码元的异或确定;拼接单元,用于将预设数量相同的v子段拼接成一个v子段,生成k个v子段,k为正整数;校验单元,用于利用各v子段中的校验码,对各v子段进行校验。

22.根据本公开的又一些实施例,提供一种极化码的编码装置,包括:置换单元,用于对原始的待编码码元序列进行位置置换处理,得到m个长度为n的w子段,m、n为2的整次幂,原始的待编码码元序列包括k个全0的原始校验码;分解单元,用于根据b子段与w子段的变换关系,将m个w子段中的码元分解为m个b子段中的码元的组合,每一个w子段中码元由相应的预设数量的b子段码元的异或确定;拼接单元,用于将预设数量相同的w子段拼接成一个w子段,生成k个w子段,k为正整数;校验单元,用于生成各w子段的校验码,各w子段的校验码和各w子段的数据码元组成各w子段的信息码元,各w子段的信息码元和各w子段的冻结码元组成各w子段,利用各w子段的校验码替换原始的待编码码元序列中的全0原始校验码,得到待编码码元序列;编码单元,用于对待编码码元序列进行极化码编码,得到编码码元序列,以便译码侧进行译码处理。

23.根据本公开的又一些实施例,提供一种电子设备,包括:存储器;和耦接至存储器的处理器,处理器被配置为基于存储在存储器装置中的指令,执行上述任一个实施例中的极化码的译码方法,或者极化码的编码方法。

24.根据本公开的再一些实施例,提供一种非易失性计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现上述任一个实施例中的极化码的译码方法,或者极化码的编码方法。

25.在上述实施例中,在译码器侧利用子段变换公式的特点,采用消元法,将v码元空间的v子段校验码直接运用于a码元空间的校验,将a

→

v码元空间变换的多码元多码值多出现概率组合的浮点及异或运算指数复杂性转化为a

→

v码元空间多码元单码值出现概率为1的子段变换异或运算线性复杂性。

26.从而,大幅度降低子段并行译码-子段校验scl译码的复杂性和硬件要求。

附图说明

27.构成说明书的一部分的附图描述了本公开的实施例,并且连同说明书一起用于解释本公开的原理。

28.参照附图,根据下面的详细描述,可以更加清楚地理解本公开:

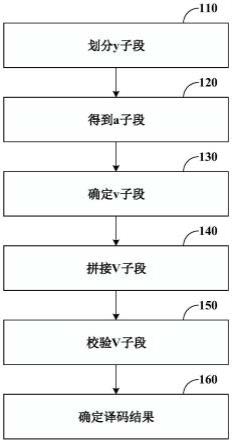

29.图1示出本公开的极化码的译码方法的一些实施例的流程图;

30.图2示出本公开的极化码的编码方法的一些实施例的流程图;

31.图3示出本公开的极化码的译码/编码方法的一些实施例的示意图;

32.图4a示出本公开的极化码的译码装置的一些实施例的框图;

33.图4b示出本公开的极化码的编码装置的一些实施例的框图;

34.图5示出本公开的电子设备的一些实施例的框图;

35.图6示出本公开的电子设备的另一些实施例的框图。

具体实施方式

36.现在将参照附图来详细描述本公开的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本公开的范围。

37.同时,应当明白,为了便于描述,附图中所示出的各个部分的尺寸并不是按照实际的比例关系绘制的。

38.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本公开及其应用或使用的任何限制。

39.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,技术、方法和设备应当被视为授权说明书的一部分。

40.在这里示出和讨论的所有示例中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它示例可以具有不同的值。

41.应注意到:相似的标号和字母在下面的附图中表示类似项,因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

42.针对上述技术问题,可以通过下面的实施例实现本公开的技术方案。

43.图1示出本公开的极化码的译码方法的一些实施例的流程图。

44.如图1所示,在步骤110中,将待译码码元序列划分为m个长度为n的y子段,m、n为2的整次幂。

45.在步骤120中,对m个y子段分别进行独立的译码,得到m个a子段。

46.在步骤130中,根据a子段与v子段的变换关系,确定m个v子段。变换关系中每一个v子段中码元由相应的预设数量的a子段码元的异或确定。

47.在步骤140中,将预设数量相同的v子段拼接成一个v子段,生成k个v子段,k为正整数。

48.在步骤150中,利用各v子段中的校验码,对各v子段进行校验。

49.在步骤160中,根据校验结果,确定各v子段的译码结果。

50.在一些实施例中,k的取值为1+log2m。

51.在一些实施例中,根据校验结果,确定各v子段的译码结果包括:对于第k个v子段,在存在一条通过校验的备选路径的情况下,将通过校验的备选路径确定为第k个v子段的译码结果,在存在多条通过校验的备选路径的情况下,将出现概率最大的通过校验的备选路径确定为第k个v子段的译码结果,在不存在通过校验的备选路径的情况下,将出现概率最大的备选路径确定为第k个v子段的译码结果。

52.在一些实施例中,译码方法还包括:对于第k-1个v子段,将第k个v子段的译码结果代入变换关系,以更新变换关系;其中,根据a子段与v子段的变换关系,确定m个v子段包括:根据更新之后的变换关系,确定m个v子段;将预设数量相同的v子段拼接成一个v子段包括:将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段;利用各v子段中的校验码,对各v子段进行校验包括:利用各v子段中的校验码,对第k-1个v子段的l条备选路径进行校验。

53.在一些实施例中,将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段包括:将第k-1个v子段中第1个v子段的l条备选路径和第2个v子段的l条备选路径进行两两拼接,得到l2条备选路径;保留出现概率最大的l条备选路径,并与第3个v子段的l条备选路径拼接,再次得到l2条备选路径;保留出现概率最大的l条备选路径;重复上述步骤,直到完成log2m个v子段的拼接,保留出现概率最大的l条备选路径作为第k-1个v子段的l条备选路径。

54.在一些实施例中,将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段包括:将log2m个v子段两两拼接,分别得到出现概率最大的l条备选路径;分别将出现概率最大的l条备选路径两两拼接,再次分别得到出现概率最大的l条备选路径;重复上述步骤,直到完成log2m个v子段的拼接,保留出现概率最大的l条备选路径作为第k-1个v子段的l条备选路径。

55.在一些实施例中,译码方法还包括:对于第k个v子段以外的v子段,将排在该v子段后面的v子段的译码结果代入变换关系,以更新变换关系;根据a子段与v子段的变换关系,确定m个v子段包括:根据更新之后的变换关系,确定m个v子段;将预设数量相同的v子段拼接成一个v子段包括:将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的该v子段;利用各v子段中的校验码,对各v子段进行校验包括:利用各v子段中的校验码,对该v子段的l条备选路径进行校验。

56.在一些实施例中,根据校验结果,确定各v子段的译码结果包括:对各v子段进行子段拆分处理、位置逆置换处理,确定译码结果,位置逆置换处理与编码侧的位置置换处理互为逆过程。

57.在一些实施例中,拼接成各v子段的v子段的数量根据a子段与v子段的变换关系确定,拼接成第1个v子段的v子段的数量为1,拼接成第k个v子段的v子段的数量为1。

58.在一些实施例中,冻结码元为0。

59.图2示出本公开的极化码的编码方法的一些实施例的流程图。

60.如图2所示,在步骤210中,对原始的待编码码元序列进行位置置换处理,得到m个长度为n的w子段,m、n为2的整次幂,原始的待编码码元序列包括k个全0的原始校验码。

61.在步骤220中,根据b子段与w子段的变换关系,将m个w子段中的码元分解为m个b子段中的码元的组合,每一个w子段中码元由相应的预设数量的b子段码元的异或确定。

62.在步骤230中,将预设数量相同的w子段拼接成一个w子段,生成k个w子段,k为正整数。

63.在步骤240中,生成各w子段的校验码,各w子段的校验码和各w子段的数据码元组成各w子段的信息码元,各w子段的信息码元和各w子段的冻结码元组成各w子段。利用各w子段的校验码替换原始的待编码码元序列中的全0原始校验码,得到待编码码元序列。

64.在步骤250中,对待编码码元序列进行极化码编码,得到编码码元序列,以便译码侧进行译码处理。

65.在一些实施例中,k的取值为1+log2m。

66.在一些实施例中,原始的待编码码元序列包括数据码元、冻结码元。

67.在一些实施例中,冻结码元为预设的固定值。

68.图3示出本公开的极化码的译码/编码方法的一些实施例的示意图。

69.如图3所示,与译码器相对应,编码器对原始待编码码元序列进行位置置换、w子段组合,w子段校验码生成后,对包含w子段校验码的u

1n

进行极化码编码得到编码码字。

70.在编码侧,可以按照预设参数的极化码编码公式,利用原始待编码码元序列,通过位置置换得到m个长度为n的w子段。

71.m和n为2的整次幂,原始待编码码元序列由数据码元、全0校验码码元和预设的冻结码元组成。冻结码元为固定值,一般为0,全0校验码码元位于信息位。

72.w子段的码元可以分解为b子段中的b

ij

码元组合,i=1,2,3,

…

m,j=1,2,3,

…

n。例如,b

→

w子段的变换公式如下:

[0073][0074]

j=1,2,3,

…

,n。

[0075]

将b

→

w子段的变换公式中包含b

ij

码元数量相同的w子段串接为一个wi子段,i=1,2,3,

…

,,k,2

k-1

=m。

[0076]

对wi子段中的数据码元序列进行校验码生成运算得到校验码cci。cci和wi子段中的数据码元组成wi子段的信息码元。将cci代替原始待编码码元序列中的全0原始校验码得到待编码码元序列;对待编码码元序列进行极化码编码得到编码码字。

[0077]

在译码侧,vi子段对应于编码器侧的wi子段;vi子段由与wi子段中w子段相对应的v子段以和wi子段相同的拼接方法拼接而成。

[0078]

将待译码码字分为m个长度为n的y

1n

子段,对m个y

1n

子段分别独立进行scl译码得到m个a子段。例如,a

→

v子段变换公式如下所示:

[0079][0080]

j=1,2,3,

…

,n。

[0081]

采用消元法,按照顺序消除上面公式中的a

mj

、a

(m-1)j

、a

(m-2)j

、

…

、a

2j

。

[0082]

在一些实施例中,消除公式中的a

mj

。vk子段已经是单码元多码值多出现概率的子段,不需要消元就可由cck执行vk子段校验。

[0083]

通过校验的备选路径为vk子段的译码结果;如果有多条备选路径通过校验,以通过校验的、出现概率最大的备选路径作为vk子段的译码结果;如果没有备选路径通过校验,以出现概率最大的备选路径作为vk子段的译码结果。将vk子段的、同时也是am子段的译码结果代入上述公式得到更新的公式:

[0084][0085]amj

(0|1)表示a

mj

的值已经确定为0或1,j=1,2,3,

…

,n。

[0086]

从更新的公式可见,m个等式右边的多码值多出现概率的a码元数量减少了1个(消元法),v

(m-1)j

、v

(m-2)j

、v

(m-4)j

、v

(m-8)j

、

…

、等则分别只包含一个多码值多出现概率的a码元:a

(m-1)j

、a

(m-2)j

、a

(m-4)j

、a

(m-8)j

、

…

、等。

[0087]

在一些实施例中,消除a

(m-1)j

、a

(m-2)j

、a

(m-4)j

、a

(m-8)j

、

…

、等。将v

k-1

子段中有l条备选路径的v子段,按照下述方式拼接为一个只有l条备选路径长度为n

×

log2m的v

k-1

子段。

[0088]

拼接方式为:v

k-1

中第1个v子段的l条备选路径和第2个v子段的l条备选路径两两组合得到l2条备选路径;保留出现概率最大的l条备选路径作为拼接后的子段的备选路径;

以相同方法与第3个v子段的l条备选路径拼接,保留出现概率最大的l条备选路径作为拼接后的子段的备选路径,依次类推,直到完成全部log2m个v子段的拼接。

[0089]

对v

k-1

子段的l条备选路径由cc

k-1

进行校验;通过校验的路径为v

k-1

子段的译码结果;如果有多条备选路径通过校验,以通过校验的、出现概率最大的备选路径作为v

k-1

子段的译码结果;如果没有备选路径通过校验,以出现概率最大的备选路径作为v

k-1

子段的译码结果v

k-1hn

(0|1),由v

k-1hn

(0|1)拆分得到v

(m-1)j

、v

(m-2)j

、v

(m-4)j

、v

(m-8)j

、

…

、等,h=h

k-1

=log2m。

[0090]

依据上述更新的公式可以得到:

[0091][0092][0093][0094][0095]

…

[0096]

将a

(m-1)j

(0|1)、a

(m-2)j

(0|1)、a

(m-4)j

(0|1)、a

(m-8)j

(0|1)、

…

、等代入更新的公式,再次更新公式为:

[0097][0098]aij

(0|1)表示a

ij

的值已经确定为0或1,i=1,2,3,m,j=1,2,3,

…

,n。

[0099]

在执行消元的子段校验过程中,如果v

ij

为冻结码元,而待校验的l条备选路径中相应a

ij

码元的异或结果不为0,则该备选路径可直接删除,不需要进行校验,以减少计算量。

[0100]

以此类推,依次对v

k-2

、v

k-3

、v

k-4

、

…

、v1进行消元处理直到完成全部v子段/v子段的译码并经位置逆置换后作为译码输出。

[0101]

例如,拼接方式可以为:将v

k-2

、v

k-3

、v

k-4

、

…

、v1子段中有l条备选路径的v子段拼接为一个只有l条备选路径长度为h

×

n的v

k-2

、v

k-3

、v

k-4

、

…

、v1子段,h为v

k-2

、v

k-3

、v

k-4

、

…

、v1子段中包含v子段的数量。

[0102]

例如,m=8时,预设数量为1的v子段中有1个(h=1)v子段,预设数量为2的v子段中有3个(h=3)v子段,预设数量为4的v子段中有3个(h=3)v子段,预设数量为8的v子段中有1个(h=1)v子段。

[0103]

例如,对于任意m,第1个和最后一个(第k个)v子段的预设数量都为1(h=1);第2个和倒数第2个(第k-1个)v子段的预设数量都为log2m(h=log2m);第3个和倒数第3个(第k-2

个)v子段的预设数量都为以此类推。

[0104]

例如,预设数量h的取值可以如下表所示:

[0105]

v子段序号kk-1k-2k-3k-4k-5k-6k-7k-8k-9m=211

ꢀꢀꢀꢀꢀꢀꢀꢀ

m=4121

ꢀꢀꢀꢀꢀꢀꢀ

m=81331

ꢀꢀꢀꢀꢀꢀ

m=1614641

ꢀꢀꢀꢀꢀ

m=3215101051

ꢀꢀꢀꢀ

m=641615201561

ꢀꢀꢀ

m=128172135352171

ꢀꢀ

m=25618285670562881 m=1024193684126126843691

…ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

[0106]vk-2

、v

k-3

、v

k-4

、

…

、v1子段中第1个v子段的l条备选路径和第2个v子段的l条备选路径两两组合得到l2条备选路径,保留出现概率最大的l条作为拼接后的备选路径;以相同方法与第3个v子段的l条备选路径拼接,直到完成全部v子段的拼接。

[0107]

上述串行拼接方法不是唯一的,还可以两两v子段同时拼接成更长的子段,然后更长v子段再两两同时拼接,依次类推,直到完成全部子段的拼接,可以缩短拼接时间。

[0108]

实际译码过程中,a

→

v子段变换公式中第1子段的m个a码元组合包含了第2到第m个子段的组合,因此可以重复使用各种组合以降低计算复杂性。

[0109]

在本公开中,码元和比特含义相同,例如,信息码元和信息比特的含义相同,冻结码元和冻结比特的含义相同。

[0110]

译码器中scl译码器独立地进行m个子段的scl译码,因此可以灵活采用不同的具体实现方式。

[0111]

例如,可以用m个scl译码器并行执行scl译码,以便在最短的时间完成译码;也可以采用一个scl译码器串行地执行m个子段的scl译码,需要的硬件资源最少,但译码时间最长;还可以将m个子段分成m1个组,由m2(m2=m/m1)个scl译码器重复执行m1次scl译码,以均衡硬件资源要求和译码时间要求。

[0112]

在上述实施例中,译码过程中a

→

v子段变换时只需要执行一条译码路径的异或运算。与总数为2m×

l条合并备选路径的浮点计算以及硬件要求相比,其复杂性以及硬件要求非常低。

[0113]

m个子段拼接的复杂性为o((m-1)l2)个,和子段数量为线性关系,当m较大时,其复杂性和m个scl译码器的复杂性o(lnlog(n/m))以及联合判决-逐比特合并路径的复杂性2mln/m相比较,其复杂性非常低。

[0114]

本公开的技术方案适用于polar长码以及较大的m,可以获得更低的译码时间、更低的复杂性、更低的硬件要求。

[0115]

图4a示出本公开的极化码的译码装置的一些实施例的框图。

[0116]

如图4a所示,极化码的译码装置4a包括:划分单元41a,用于将待译码码元序列划

分为m个长度为n的y子段,m、n为2的整次幂;译码单元42a,用于对m个y子段分别进行独立的译码,得到m个a子段,根据校验结果,确定各v子段的译码结果;确定单元43a,用于根据a子段与v子段的变换关系,确定m个v子段,变换关系中每一个v子段中码元由相应的预设数量的a子段码元的异或确定;拼接单元44a,用于将预设数量相同的v子段拼接成一个v子段,生成k个v子段,k为正整数;校验单元45a,用于利用各v子段中的校验码,对各v子段进行校验。

[0117]

在一些实施例中,k的取值为1+log2m。

[0118]

在一些实施例中,译码单元42a对于第k个v子段,在存在一条通过校验的备选路径的情况下,将通过校验的备选路径确定为第k个v子段的译码结果,在存在多条通过校验的备选路径的情况下,将出现概率最大的通过校验的备选路径确定为第k个v子段的译码结果,在不存在通过校验的备选路径的情况下,将出现概率最大的备选路径确定为第k个v子段的译码结果。

[0119]

在一些实施例中,确定单元43a对于第k-1个v子段,将第k个v子段的译码结果代入变换关系,以更新变换关系;根据更新之后的变换关系,确定m个v子段;拼接单元44a将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的第k-1个v子段;校验单元45a利用各v子段中的校验码,对第k-1个v子段的l条备选路径进行校验。

[0120]

在一些实施例中,拼接单元44a将第k-1个v子段中第1个v子段的l条备选路径和第2个v子段的l条备选路径进行两两拼接,得到l2条备选路径;保留出现概率最大的l条备选路径,并与第3个v子段的l条备选路径拼接,再次得到l2条备选路径;保留出现概率最大的l条备选路径;重复上述步骤,直到完成log2m个v子段的拼接,保留出现概率最大的l条备选路径作为第k-1个v子段的l条备选路径。

[0121]

在一些实施例中,拼接单元44a将log2m个v子段两两拼接,分别得到出现概率最大的l条备选路径;分别将出现概率最大的l条备选路径两两拼接,再次分别得到出现概率最大的l条备选路径;重复上述步骤,直到完成log2m个v子段的拼接,保留出现概率最大的l条备选路径作为第k-1个v子段的l条备选路径。

[0122]

在一些实施例中,确定单元43a对于第k个v子段以外的v子段,将排在该v子段后面的v子段的译码结果代入变换关系,以更新变换关系;根据更新之后的变换关系,确定m个v子段;将拼接单元44a将有l条备选路径的多个v子段,拼接为一个有l条备选路径长度为n

×

log2m的该v子段;校验单元45a利用各v子段中的校验码,对该v子段的l条备选路径进行校验。

[0123]

在一些实施例中,确定单元43a对各v子段进行子段拆分处理、位置逆置换处理,确定译码结果,位置逆置换处理与编码侧的位置置换处理互为逆过程。

[0124]

在一些实施例中,拼接成各v子段的v子段的数量根据a子段与v子段的变换关系确定,拼接成第1个v子段的v子段的数量为1,拼接成第k个v子段的v子段的数量为1。

[0125]

图4b示出本公开的极化码的编码装置的一些实施例的框图。

[0126]

如图4b所示,极化码的编码装置4b包括:置换单元41b,用于对原始的待编码码元序列进行位置置换处理,得到m个长度为n的w子段,m、n为2的整次幂,原始的待编码码元序列包括k个全0的原始校验码;分解单元42b,用于根据b子段与w子段的变换关系,将m个w子段中的码元分解为m个b子段中的码元的组合,每一个w子段中码元由相应的预设数量的b子段码元的异或确定;拼接单元43b,用于将预设数量相同的w子段拼接成一个w子段,生成k个

w子段,k为正整数;校验单元44b,用于生成各w子段的校验码,各w子段的校验码和各w子段的数据码元组成各w子段的信息码元,各w子段的信息码元和各w子段的冻结码元组成各w子段,利用各w子段的校验码替换原始的待编码码元序列中的全0原始校验码,得到待编码码元序列;编码单元45b,用于对待编码码元序列进行极化码编码,得到编码码元序列,以便译码侧进行译码处理。

[0127]

在一些实施例中,k的取值为1+log2m。

[0128]

在一些实施例中,原始的待编码码元序列包括数据码元、冻结码元。

[0129]

在一些实施例中,冻结码元为预设的固定值。

[0130]

图5示出本公开的电子设备的一些实施例的框图。

[0131]

如图5所示,该实施例的电子设备5包括:存储器51以及耦接至该存储器51的处理器52,处理器52被配置为基于存储在存储器51中的指令,执行本公开中任意一个实施例中的极化码的译码方法,或者极化码的编码方法。

[0132]

其中,存储器51例如可以包括系统存储器、固定非易失性存储介质等。系统存储器例如存储有操作系统、应用程序、引导装载程序boot loader、数据库以及其他程序等。

[0133]

图6示出本公开的电子设备的另一些实施例的框图。

[0134]

如图6所示,该实施例的电子设备6包括:存储器610以及耦接至该存储器610的处理器620,处理器620被配置为基于存储在存储器610中的指令,执行前述任意一个实施例中的极化码的译码方法,或者极化码的编码方法。

[0135]

存储器610例如可以包括系统存储器、固定非易失性存储介质等。系统存储器例如存储有操作系统、应用程序、引导装载程序boot loader以及其他程序等。

[0136]

电子设备6还可以包括输入输出接口630、网络接口640、存储接口650等。这些接口630、640、650以及存储器610和处理器620之间例如可以通过总线860连接。其中,输入输出接口630为显示器、鼠标、键盘、触摸屏、麦克、音箱等输入输出设备提供连接接口。网络接口640为各种联网设备提供连接接口。存储接口650为sd卡、u盘等外置存储设备提供连接接口。

[0137]

本领域内的技术人员应当明白,本公开的实施例可提供为方法、系统、或计算机程序产品。因此,本公开可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本公开可采用在一个或多个其中包含有计算机可用程序代码的计算机可用非瞬时性存储介质包括但不限于磁盘存储器、cd-rom、光学存储器等上实施的计算机程序产品的形式。

[0138]

至此,已经详细描述了根据本公开的极化码的译码方法、极化码的译码装置、极化码的编码方法、极化码的编码装置、电子设备和非易失性计算机可读存储介质。为了避免遮蔽本公开的构思,没有描述本领域所公知的一些细节。本领域技术人员根据上面的描述,完全可以明白如何实施这里公开的技术方案。

[0139]

可能以许多方式来实现本公开的方法和系统。例如,可通过软件、硬件、固件或者软件、硬件、固件的任何组合来实现本公开的方法和系统。用于方法的步骤的上述顺序仅是为了进行说明,本公开的方法的步骤不限于以上具体描述的顺序,除非以其它方式特别说明。此外,在一些实施例中,还可将本公开实施为记录在记录介质中的程序,这些程序包括用于实现根据本公开的方法的机器可读指令。因而,本公开还覆盖存储用于执行根据本公

开的方法的程序的记录介质。

[0140]

虽然已经通过示例对本公开的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上示例仅是为了进行说明,而不是为了限制本公开的范围。本领域的技术人员应该理解,可在不脱离本公开的范围和精神的情况下,对以上实施例进行修改。本公开的范围由所附权利要求来限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1