用于减少音频假象的数字信号发生器的制作方法

1.本公开涉及一种用于减少音频放大器中的音频假象(audio artefact)的数字信号发生器。

背景技术:

2.音频放大器可以产生音频假象,例如可听见的砰砰声和卡嗒声。例如当音频放大器接通或关闭时或者由于静音操作或取消静音操作,可能会出现这些假象。为了减少此类音频假象,可以在使放大器通电或断电或者执行静音/取消静音操作时逐渐增大或减小施加到所述放大器的电压。

技术实现要素:

3.在所附权利要求书中限定本公开的各种方面。在第一方面中,提供一种用于减少音频放大器中的音频假象的数字信号发生器,所述数字信号发生器包括:计数器,所述计数器具有计数器输出且被配置成取决于计数器控制输入从初始计数器值开始递增计数或递减计数;比较器,所述比较器具有耦合到所述计数器输出的第一比较器输入、第二比较器输入以及耦合到所述计数器控制输入的比较器输出;其中所述数字信号发生器被配置成取决于应用于所述第二比较器输入的阈值与计数器输出值之间的比较确定所述初始计数方向之后的计数方向;以及积分器,所述积分器具有耦合到所述计数器输出的积分器输入和耦合到数字信号发生器输出的积分器输出。

4.在一个或多个实施例中,所述数字信号发生器可以另外被配置成从所述初始计数器值递增计数到所述阈值,接着递减计数到所述初始计数器值。

5.在一个或多个实施例中,所述数字信号发生器可以另外被配置成从所述初始计数器值递减计数到所述阈值,接着递增计数到所述初始计数器值。

6.在一个或多个实施例中,所述数字信号发生器可以另外包括耦合到所述积分器和所述计数器的复位输入以及耦合到所述计数器的预设值输入,其中所述初始计数器值通过复位值确定且计数器步长通过所述预设值确定。

7.在一个或多个实施例中,所述积分器可以另外包括求和模块、延迟元件和增益模块,其中第一求和模块输入耦合到所述计数器输出,第二求和模块输入耦合到延迟元件输出,求和模块输出耦合到增益模块输入,并且增益模块输出耦合到所述积分器输出。

8.在一个或多个实施例中,数字信号的持续时间可以取决于所述计数器的时钟频率和所述计数器步长中的至少一个。

9.在一个或多个实施例中,所述数字信号发生器输出的幅值可以取决于所述增益模块的增益。

10.在一个或多个实施例中,所述计数器输出可以对应于三角波形,并且所述数字信号发生器输出可以对应于升余弦波形的近似。

11.在一个或多个实施例中,根据在前的任一项权利要求所述的数字信号发生器可以

包括控制器,所述控制器具有耦合到所述计数器的输出的输入、耦合到阈值输入的第一控制输出、耦合到所述复位输入的第二控制输出和耦合到预设输入的第三控制输出。

12.在一个或多个实施例中,所述数字信号发生器可以包括在音频放大器系统中。所述数字信号发生器输出可以耦合到所述音频放大器系统的放大器级的音频输入。

13.在一个或多个实施例中,所述数字信号发生器可以被配置成响应于使所述放大器级在关闭状态与接通状态之间切换而生成数字信号。

14.在一个或多个实施例中,所述数字信号发生器可以被配置成响应于在所述音频放大器的静音状态与取消静音状态之间切换而生成数字信号。

15.在第二方面中,提供一种用于减少音频放大器中的音频假象的数字信号生成方法,所述方法包括:提供被配置成从初始值沿初始计数方向开始递增计数或递减计数的数字计数器;将计数器输出与阈值进行比较以确定所述初始计数方向之后的计数方向;提供用以对所述计数器输出进行积分的积分器;提供来自所述积分器的输出的数字信号输出。

16.在一个或多个实施例中,所述方法可以另外包括响应于使所述音频放大器的放大器级在关闭状态与接通状态之间切换,将数字信号施加到所述放大器级。

17.在一个或多个实施例中,所述方法可以另外包括响应于使所述音频放大器的所述放大器级在所述音频放大器的静音状态与取消静音状态之间切换,将所述数字信号施加到所述放大器级。

18.在一个或多个实施例中,所述计数器输出可以对应于三角波形或锯齿状波形。

19.在第三方面中,提供一种包括计算机程序的非暂时性计算机可读介质,所述计算机程序包括计算机可执行指令,所述计算机可执行指令在由计算机执行时使所述计算机执行用于减少音频放大器中的音频假象的方法,所述方法包括以下步骤:从初始值沿初始计数方向开始递增计数或递减计数;将计数器输出与阈值进行比较以确定所述初始计数方向之后的计数方向;提供用以对所述计数器输出进行积分的积分器;以及提供来自所述积分器的输出的数字信号输出。

20.在一个或多个实施例中,所述非暂时性计算机可读介质可以另外包括用以执行以下步骤的计算机可执行指令:响应于使所述音频放大器的放大器级在关闭状态与接通状态之间切换,将数字信号施加到所述放大器级。

21.在一个或多个实施例中,所述非暂时性计算机可读介质可以另外包括用以执行以下步骤的计算机可执行指令:响应于使所述音频放大器的所述放大器级在所述音频放大器的静音状态与取消静音状态之间切换,将所述数字信号施加到所述放大器级。

附图说明

22.在图和描述中,相同的附图标记指代相同的特征。现在仅借助于通过附图示出的例子详细地描述实施例,在附图中:

23.图1示出了根据实施例的包括数字信号发生器的音频放大器系统。

24.图2a示出了图1的音频放大器系统的操作方法。

25.图2b示出了图1的音频放大器系统的操作方法。

26.图3a示出了使用图1的数字信号发生器生成用于减少音频假象的升余弦信号的近似的方法。

27.图3b示出了由图1的数字信号发生器使用图3a的方法生成的示例增大的近似余弦波形。

28.图3c示出了使用图3a的方法生成的示例减小的近似余弦波形。

29.图4a示出了使用图1的数字信号发生器生成升余弦信号的近似的方法。

30.图4b示出了使用图4a的方法生成的示例近似余弦波形。

31.图5示出了根据实施例的数字信号发生器。

具体实施方式

32.图1示出了根据实施例的包括数字信号发生器120的音频放大器系统100。音频放大器系统100还可以包括数模转换器(dac)122,可以是例如a类、ab类或d类放大器的放大器级126,以及扬声器130。

33.数字信号发生器120可以包括控制器112、积分器114、计数器模块110和比较器108。控制器112可以具有耦合到计数器模块110和积分器114的复位输出102。控制器112可以具有连接到计数器输出116的输入。计数器输出116可以连接到比较器108的第一输入和积分器114的输入。控制器112可以具有连接到比较器108的第二输入的阈值输出106。比较器输出104可以连接到计数器模块110的上下控制输入。积分器114的输出可以连接到数字信号发生器输出118。数字信号120可以完全使用硬件数字逻辑门来实施。在其它例子中,计数器模块110、积分器114、控制器112和比较器108中的一个或多个可以实施为在微处理器上运行的软件。

34.在操作中,数字信号发生器输出118可以连接到dac 122的输入。如果放大器级126是数字放大器或具有数字放大器输入,则可以省略dac 122。放大器级126可以具有连接到dac 122的输出的音频输入124。放大器级输出128可以连接到扬声器130。

35.图2a示出了音频放大器系统100的示例操作方法150。在步骤152,可以使音频放大器100接通或取消静音。在步骤154,数字信号发生器120可以生成增大的升余弦近似信号。在步骤156,可以将升余弦近似信号施加到放大器级126的音频输入。在步骤156之后,音频放大器级126随后可以基于音频输入124接收所需音频信号。如图1所示,dac输出直接连接到音频输入124。在放大器级126是数字放大器的其它实施例中,可以省略dac 122,并且数字信号发生器输出118可以例如利用多路复用器或其它数字逻辑与音频输入124以数字方式组合。

36.图2b示出了音频放大器系统100的示例操作方法160。在步骤162,可以使音频放大器100关闭或静音。在步骤164,数字信号发生器120可以生成减小的升余弦近似信号。在步骤166,可以将升余弦近似信号施加到放大器级126的音频输入。

37.图3a示出了生成可以增大或减小的近似升余弦信号的方法200。方法200可以例如使用数字信号发生器120来实施。在步骤202,可以例如由控制器112基于阈值输出106设定值来设定计数器阈值。在步骤204,可以由控制器112将计数器110和积分器114复位到相应的初始值。在一些例子中,可以颠倒步骤202和204的次序。可以设定积分器复位值以确定dc电压电平。计数器复位值可以例如为零,但可以为一些其它值。在步骤206,计数器110可以从通过复位确定的初始计数器值开始递增计数或递减计数。可以取决于是需要增大的升余弦近似还是需要减小的升余弦近似来确定初始计数器方向。对于增大的升余弦近似,计数

器将初始地递增计数,并且对于减小的升余弦近似,计数器110将初始地递减计数。在步骤206之后,方法进行到其中进行阈值与计数器值之间的比较的步骤210。在数字信号发生器120中,这可以例如通过比较器108将由控制器112设定的阈值与基于计数器输出116的当前计数器值进行比较来完成。如果尚未达到阈值,则方法进行到步骤208,并且计数器沿如先前设定的相同方向继续计数。方法接着返回到210以针对阈值重复检查。如果已达到阈值,则方法进行到212并且改变计数方向。方法200接着进行到其中进行关于是否已达到在步骤204设定的初始计数器值的检查的步骤214。如果尚未达到初始计数器值,则方法进行到步骤216,并且沿相同方向继续计数。在步骤216之后,方法接着返回到214处的检查。如果在步骤214已达到初始计数器值,则方法进行到步骤218且流程结束。

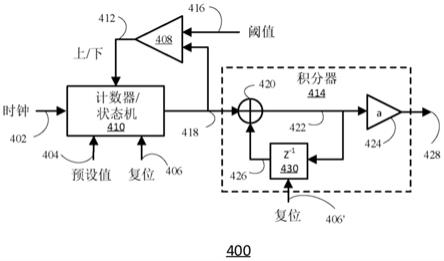

38.图3b示出了y轴上的计数器值与x轴上的时间的关系的曲线图260。曲线图260示出了当实施方法200以生成增大的余弦近似信号时,数字信号发生器120的计数器输出值262和积分器输出264的例子。计数器120输出锯齿状波形或三角波形,所述波形从初始计数器值增大到阈值,接着从阈值减小到初始值。积分器114对此波形的积分产生了升余弦的增大近似。

39.图3c示出了y轴上的计数器值与x轴上的时间的关系的曲线图270。曲线图270示出了当实施方法200以生成减小的余弦近似信号时,数字信号发生器120的计数器输出值272和积分器输出274的例子。计数器120输出锯齿状波形,所述波形从初始值减小到阈值,接着从阈值增大到初始值。积分器114对此波形的积分产生了升余弦的增大近似。

40.为了实现升余弦(或一般而言,余弦),通常需要查找表(内存)。此内存的大小取决于所需的分辨率。为了减小内存大小,可以在后续点之间进行插值,但这会限制准确性或需要更高阶的内插,这意味着可能需要大量硬件。

41.本公开的发明人已了解,升余弦函数可以通过a(x-b)2+c函数的组合以数字逻辑有效地实施的近似计算从这里开始被称作近似法。在近似升余弦的前半部分,a为正,在升余弦的后半部分,a为负。选择系数b和c使得两条半曲线精确拟合在一起,由此确保曲线是连续的。a(x-b)2+c的导数是y=2ax-2ba,a和b取决于操作数区域。因此,近似法的导数看起来像三角波。因此,通过使用计数器110和积分器114,数字信号发生器120可以生成近似余弦,与例如从等于零伏dc(或其它dc值)开始的简单线性斜坡相比,所述近似余弦可能会由于卡嗒声和砰砰声而提供改进的音频假象减少。

42.图4a示出了例如使用数字信号发生器120来生成连续的近似升余弦信号300的方法。在步骤302,可以由控制器112设定计数器阈值。在步骤304,可以将计数器110和积分器114设定成相应的初始值。在一些例子中,可以颠倒步骤302和304的次序。计数器110和积分器114的初始值可以相同或不同。在步骤306,计数器可以沿初始方向开始递增计数或递减计数。方法接着进行到步骤310且进行检查以查看是否已达到第一阈值。可以通过比较器108将计数器输出116与阈值输出106进行比较而在数字信号发生器120中完成此检查。如果尚未达到第一阈值,则方法进行到步骤308且沿相同方向继续计数,接着方法返回到步骤310。一旦已达到第一阈值,则方法进行到步骤312且改变计数器方向。在改变方向之后,在步骤314设定第二阈值。这可以例如由控制器112基于阈值输出106设定第二阈值来完成。方法接着进行到其中进行检查以查看是否已达到第二阈值的步骤318。如果尚未达到第二阈值,则在步骤316计数器将沿如先前限定的相同方向继续计数。方法然后返回到步骤318。一

旦已达到第二阈值,则方法300进行到步骤320且再次改变计数器方向。在步骤322,控制器112可以将计数器阈值设定回第一值。方法接着进行到其中计数器110递增计数或递减计数的306,通过当前计数器方向值确定方向且重复周期。

43.图4b示出了y轴上的计数器值与x轴上的时间的关系的曲线图330。曲线图330示出了使用方法300生成的波形的例子。波形332示出了正生成连续三角波的计数器的输出。波形334对应于通过对计数器输出进行积分而生成升余弦波的近似的积分器114的输出。

44.图5示出了根据实施例的数字信号发生器400。数字信号发生器400可以使用数字逻辑硬件来实施,并且可以用于例如实施方法200和300。数字信号发生器400包括计数器410、比较器408和积分器414。积分器414包括求和模块420、延迟元件430和增益模块424。

45.计数器410可以被配置成递增计数且递减计数,且还可以包括实施为状态机的一些控制逻辑。计数器可以具有可以用于例如确定计数器步长s的时钟输入402、预设值输入404。计数器410还可以具有复位输入406和上下控制输入412。计数器输出418还可以连接到比较器408的第一输入。比较器408的第二输入416可以从控制器(未示出)接收阈值。比较器输出可能连接到上下控制输入412。计数器输出418可以连接到求和模块420的第一输入。求和模块420的第二输入可以连接到延迟元件430的输出426。求和模块输出422可以连接到延迟元件430的输入和增益模块424的输入。增益模块424的输出可以连接到信号发生器输出428。复位输入406'可以连接到延迟元件430。可以是硬件寄存器的延迟元件430还可以连接到时钟输入402(未示出)。

46.在操作中,数字信号发生器400可以类似于方法200的方式生成曲线图260中所示的增大的余弦近似。在可以由连接到复位输入406的控制器(未示出)确定的复位时,计数器的输出可以设定成零。上下控制输入412可以例如是指示递增计数方向的逻辑高,并且可以设定积分器开始值。在复位之后,每个时钟周期,计数器410的输出增大s,即计数器的步长,所述步长通过预设值输入404确定。在通过阈值确定的某一阈值处,比较器输出412变为逻辑低,且因此计数器410变成递减计数,接着计数器的输出每一时钟周期减小s,直到达到0且此时将停止。对应于数字信号发生器输出428的积分器输出将成为计数器410生成的三角波的积分,如先前所描述,将近似计算升余弦波形。

47.可以通过改变施加到计数器的时钟的时钟频率和计数器步长值来改变近似升余弦长度和幅值。可以通过改变增益模块424的增益来改变近似升余弦幅值。最终幅值通常可以设定成电源电压的一半,以便所需音频信号可以沿任一方向具有最大电压摆幅。

48.数字信号发生器还可以使用类似于如方法300所描述的第二阈值来生成重复的三角波形。为了能够重构完整的正弦波,计数器410可能需要能够计数小于0。在替代性例子中,在计数器410之后,可以减去正确的dc值,以避免积分器414的失控。随后,可以利用较小的调整生成连续的余弦波。

49.数字信号发生器400允许使用非常简单的硬件来创建余弦或升余弦的近似。相比于以数字方式生成升余弦(或一般而言,余弦),通常需要查找表(内存)。此内存的大小取决于所需的分辨率。为了减小内存大小,可以在后续点之间进行插值,但这会限制准确性或需要更高阶的内插,这还意味着大量硬件。

50.在音频放大器系统100中,可以使用数字信号发生器400代替数字信号发生器120,以减少音频假象。与使用线性斜坡相比,在静音/取消静音或通电/断电操作期间使用近似

升余弦可能会减少音频假象,这是因为从dc(通常为0)到线性斜坡的转换会在导数中产生较大的不连续性,因此产生更多的频谱成分,从而产生可听见的扑通声。

51.近似余弦函数的具体应用是在音频放大器的升余弦启动中发现的。使放大器从关闭状态切换到接通状态经常会使扬声器发出可听见的扑通声。为了减少音频砰砰声,可以在关闭与打开之间使用更平滑的转换。数字信号发生器的实施例生成连续的升余弦的近似,因为0处的余弦和圆周率(pi)具有为零的导数。因此,频谱成分较少,且可听见的扑通声大大减少。通过所描述的数字信号发生器和方法生成的近似余弦可以提供与真实升余弦信号类似的音频假象减少性能,但在以硬件逻辑实施时具有明显减小的面积。

52.描述了一种数字信号发生器设备和方法。所述数字信号发生器包括计数器、积分器和比较器。所述计数器取决于计数器控制输入从初始计数器值开始递增计数或递减计数。所述比较器具有耦合到计数器输出的第一输入、阈值输入和耦合到所述计数器控制输入的比较器输出。所述积分器具有耦合到所述计数器输出的输入和耦合到数字信号发生器输出的输出。所述数字信号发生器取决于应用于所述阈值输入的阈值与计数器输出值之间的比较确定初始方向之后的计数方向。所述数字信号发生器可以实施具有升余弦函数的近似的波形生成。所生成的波形可以用于在静音操作或取消静音操作期间或在通电、断电操作期间减少音频放大器中的音频假象。

53.在一些示例实施例中,上文描述的指令集/方法步骤实施为体现为可执行指令集的功能和软件指令,所述可执行指令集在计算机或以所述可执行指令编程且受所述可执行指令控制的机器上实现。此类指令经过加载以在处理器(例如,一个或多个cpu)上执行。术语处理器包括微处理器、微控制器、处理器模块或子系统(包括一个或多个微处理器或微控制器),或其它控制或计算装置。处理器可指代单个组件或多个组件。

54.尽管所附权利要求书是针对特定特征组合的,但是应理解,本发明的公开内容的范围还包括本文中明确地或隐含地公开的任何新颖特征或任何新颖特征组合或所述新颖特征的任何概括,而不管所述新颖特征是否涉及与当前在任何权利要求中要求保护的本发明相同的发明或所述新颖特征是否缓和与本发明所缓和的技术问题相同的任一或全部技术问题。

55.在单独的实施例的上下文中描述的特征也可以在单个实施例中以组合形式提供。相反,为了简洁起见,在单个实施例的上下文中描述的各种特征也可以单独地或以任何合适的子组合形式提供。

56.申请人特此提醒,在审查本技术或由此衍生的任何另外的申请期间,可以针对此类特征和/或此类特征的组合而制定新的权利要求。

57.为完整性起见,还规定术语“包括”不排除其它元件或步骤,术语“一”或“一个”不排除多个,单个处理器或其它单元可以满足权利要求书中叙述的若干构件的功能,并且权利要求书中的附图标记不应被解释为限制权利要求书的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1