一种高速跨阻放大器的低功耗设计方法与流程

1.本发明涉及一种尾电流重注入技术,属于集成电路下跨阻放大器中的低功耗研发领域。

背景技术:

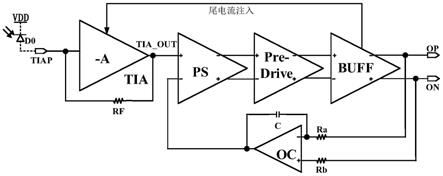

2.参见图1,高速跨阻放大器包括前置放大器tia、相位分裂级ps、预驱动级pre-drive、输出驱动级buff和失调消除电路oc;高速跨阻放大器位于光纤通信集成电路的接收端,其功能是将光电二极管d0输出的电流信号转换为电压信号并放大。低功耗设计是高速跨阻放大器的发展方向之一,即需要在灵敏度、动态范围、跨阻等性能和功耗之间进行折中,通过技术创新,在提高芯片性能的同时,降低芯片功耗。

3.电流注入技术(有文献也称为增益提高技术)是跨阻放大器常见的高性能设计技术。参见图2、3所示,给出种常见的电流注入技术,该技术使用电阻r5(图2)或者电流源 i0(图3)向输入管m1的漏端注入一个大电流(通常为10ma以上),以提高m1的跨导 gm和负载电阻r1的阻值,进而增大前置放大器tia的增益a=gm*r1,从而实现跨阻放大器的高带宽和低噪声设计。但是,该注入电流较大,会显著增加芯片的功耗。

4.因此,在使用电流注入技术提高芯片性能的同时降低芯片功耗是高性能跨阻放大器低功耗设计的关键。

技术实现要素:

5.本发明目的是为了解决现有高速跨阻放大器采用电流注入技术存在芯片功耗大的问题,提供了一种高速跨阻放大器的低功耗设计方法。

6.本发明所述一种高速跨阻放大器的低功耗设计方法,将输出驱动级buff的尾电流注入至前置放大器tia的输入管mn1漏端,来降低或杜绝通过电阻或电流源注入输入管mn1漏端的大电流,以实现低功耗。

7.优选地,将输出驱动级buff的尾电流全部注入至前置放大器tia的输入管mn1漏端,且存在关系式:

8.i1=i79.其中,i1为输入管mn1漏端的注入电流,i7为输出驱动级buff的尾电流。

10.优选地,将输出驱动级buff的尾电流全部注入至前置放大器tia的输入管mn1漏端,输入管mn1漏端还同时注入补充注入电流,所述补充注入电流采用电阻或电流源注入方式;

11.且存在关系式:

12.i1=i7+is13.其中,i1为输入管mn1漏端的注入电流,i7为输出驱动级buff的尾电流,is为补充注入电流。

14.优选地,将输出驱动级buff的尾电流部分注入至前置放大器tia的输入管mn1漏

端;

15.输出驱动级buff的尾电流i7分为两部分i7=i

71

+i

72

,i

71

为注入输入管mn1漏端的尾电流,i

72

为接地的尾电流,

16.存在关系式:

17.i1=i

71

18.其中,i1为输入管mn1漏端的注入电流。

19.优选地,将输出驱动级buff的尾电流部分注入至前置放大器tia的输入管mn1漏端;

20.输出驱动级buff的尾电流i7分为两部分i7=i

71

+i

72

,i

71

为注入输入管mn1漏端的尾电流,i

72

为接地的尾电流;

21.输入管mn1漏端还同时注入补充注入电流,所述补充注入电流采用电阻或电流源注入方式;

22.且存在关系式:

23.i1=i

71

+is24.其中,i1为输入管mn1漏端的注入电流,is为补充注入电流。

25.优选地,输出驱动级buff中的nmos晶体管mn7输出尾电流;

26.所述低功耗设计方法将尾电流通过nmos晶体管mn8引出并注入至前置放大器tia 中输入管mn1的漏端;同时,nmos晶体管mn8的漏端通过电容c3接地;

27.输入管mn1和nmos晶体管mn8和nmos晶体管mn7构成三层共源共栅结构。

28.优选地,输出驱动级buff中的nmos晶体管mn7输出尾电流;

29.所述低功耗设计方法将尾电流通过nmos晶体管mn8引出并注入至前置放大器tia 中输入管mn1的漏端;同时,nmos晶体管mn8的漏端通过电容c3接地;

30.所述低功耗设计方法还将电阻或电流源方式形成的补充注入电流同步注入前置放大器tia中输入管mn1的漏端;

31.输入管mn1和nmos晶体管mn8和nmos晶体管mn7构成三层共源共栅结构。

32.优选地,输出驱动级buff中的nmos晶体管mn7输出尾电流;

33.所述低功耗设计方法将尾电流分成两部分,一部分尾电流通过nmos晶体管mn8 引出并注入至前置放大器tia中输入管mn1的漏端,且nmos晶体管mn8的漏端通过电容c3接地;另一部分尾电流通过nmos晶体管mn9接地;

34.输入管mn1和nmos晶体管mn8和nmos晶体管mn7构成三层共源共栅结构。

35.优选地,输出驱动级buff中的nmos晶体管mn7输出尾电流;

36.所述低功耗设计方法将尾电流分成两部分,一部分尾电流通过nmos晶体管mn8 引出并注入至前置放大器tia中输入管mn1的漏端,且nmos晶体管mn8的漏端通过电容c3接地;另一部分尾电流通过nmos晶体管mn9接地;

37.所述低功耗设计方法还将电阻或电流源方式形成的补充注入电流同步注入前置放大器tia中输入管mn1的漏端;

38.输入管mn1和nmos晶体管mn8和nmos晶体管mn7构成三层共源共栅结构。

39.优选地,输出驱动级buff包括nmos晶体管mn5、nmos晶体管mn6、nmos 晶体管mn7、电阻r3、电阻r4和尾电流引出单元,输出驱动级buff还包括稳压辅助电路,用于稳定nmos晶

体管mn7漏端x点电压;

40.所述稳压辅助电路包括运算放大器amp、低通滤波器lpf、pmos晶体管mp1~mp4、电阻r5~r8、电容c1、电容c2、电流源i2和电流i3;

41.信号输入端口vinp和vinn同时连接低通滤波器lpf的输入端、电容c2的一端和电容c1的一端;

42.低通滤波器lpf的输出端同时连接pmos晶体管mp4和mp3的栅极、pmos晶体管mp2和mp1的漏端;

43.pmos晶体管mp1和mp2的栅极连接运算放大器amp的输出端;运算放大器amp 的反相端连接基准电压vref;运算放大器amp的正相端同时连接nmos晶体管mn7的漏端、nmos晶体管mn5和mn6的源端,所连接结节为x点;

44.pmos晶体管mp3的源端同时连接电阻r8的一端和电流源i3的负端;

45.pmos晶体管mp4的源端同时连接电阻r7的一端和电流源i2的负端;

46.电阻r7的另一端同时连接电容c1的另一端和nmos晶体管mn6的栅极;

47.电阻r8的另一端同时连接电容c2的另一端和nmos晶体管mn5的栅极;

48.nmos晶体管mn5的漏端同时连接电阻r3的一端和信号输出端口outn;

49.nmos晶体管mn6的漏端同时连接电阻r4的一端和信号输出端口outp;

50.nmos晶体管mn7的栅极连接电压偏置端口vb3;

51.nmos晶体管mn7的源端输出的尾电流通过尾电流引出单元注入至前置放大器tia 的输出管mn1的漏端;

52.电容c3的另一端、pmos晶体管mp4和mp3的漏端连接地;

53.电阻r3、r4、r5和r6的另一端、电流源i2和i3的正端连接电源电压vdd。

54.本发明的有益效果:提出一种跨阻放大器高性能低功耗设计方法及具体实现电路。将输出驱动器的偏置电流注入到前置放大器,取代了传统电流注入技术中的电阻或者电流源,提高了跨阻放大器的带宽和噪声等性能指标。因为将电流注入技术中的电流和输出缓冲器的偏置电流全部或者部分复用,因此实现了电流注入技术的零功耗或者低功耗,达到了高性能低功耗设计的目的。

附图说明

55.图1是现有高速跨阻放大器的组成框图;

56.图2是采用电阻向tia输入管漏端注入大电流原理框图,其中图2(a)为前置放大器的电路图,图2(b)为输出驱动级buff的电路图;

57.图3是采用电流源向tia输入管漏端注入大电流原理框图,其中图3(a)为前置放大器的电路图,图3(b)为输出驱动级buff的电路图;

58.图4是本发明所述一种高速跨阻放大器的低功耗设计方法的原理图;

59.图5是本发明尾电流注入方案一;

60.图6是本发明尾电流注入方案二;

61.图7是本发明尾电流注入方案三;

62.图8是本发明尾电流注入方案四;

63.图9是方案一的具体实施例电路;

64.图10是方案二的第一种具体实施例电路;

65.图11是方案二的第二种具体实施例电路;

66.图12是方案三的具体实施例电路;

67.图13是方案四的第一种具体实施例电路;

68.图14是方案四的第二种具体实施例电路。

具体实施方式

69.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动的前提下所获得的所有其它实施例,都属于本发明保护的范围。

70.需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

71.下面结合附图和具体实施例对本发明作进一步说明,但不作为本发明的限定。

72.具体实施方式一:下面结合图4~14说明本实施方式,本实施方式所述一种高速跨阻放大器的低功耗设计方法为:将输出驱动级buff的尾电流注入至前置放大器tia的输入管mn1漏端,来降低或杜绝通过电阻或电流源注入输入管mn1漏端的大电流,以实现低功耗。

73.在阐述常用的前置放大器和输出驱动电路中,输入管mn1的漏端注入电流和尾电流源mn7的电流各消耗10ma电流(大电流),且无法相互间重复利用,增大了整体 tia的功耗。图4为本发明提出的输出驱动尾电流重注入前置跨阻放大器技术,解决了这两束电流无法互相重复利用的问题,能够减小电路10ma的总体功耗。

74.本发明方案中,尾电流源mn7的源端不再接地,通过mn8重新注入到前置放大器 tia中输入管mn1的漏端,代替了电流源i0或电阻r5的大电流注入的功能。增加mn8 来引出尾电流的原因是:当前置放大器的输入端tinp接收到小幅值的光电信号,经过逐级放大器的增益放大,在输出驱动级buff的输出端口outp和outn产生大幅值信号,相对应的x节点将会产生电压纹波,即输出会影响输入。因此增加晶体管mn8,令输入管mn1和nmos晶体管mn8和nmos晶体管mn7构成三层共源共栅结构,提高x节点的输出阻抗,屏蔽x节点乃至输出端口outp和outn对输入管mn1的漏端影响。保证了高速tia在小光电流输入情况下的灵敏度不受影响。

75.增加起到电屏蔽作用的晶体管mn8,虽然能够消除输出对输入的影响,但是前置放大器输入管mn1和mn8、mn7共同组合成了三层共源共栅结构,该结构会严重的放大输入管mn1栅极的光电流信号,在x节点产生超大电压纹波,影响到了输出端outp 和outn的输出电压波形,产生码间干扰和大抖动。即输入会影响输出。因此需要额外的辅助电路稳定x点电压。

76.将该级输入信号vinp和vinn划分为交流信号和直流信号,交流信号通过电容c1 和c2耦合到晶体管mn5和mn6的栅极,该信号是有效的交流数据信息。直流信号经过低通滤波器lpf,滤除高频信号保留低频信号,经过晶体管mp3和mp4,电阻r7和 r8之后对晶体管mn5和mn6的栅极直流偏置。

77.当x节点电压受到输入信号tinp影响增大时,形成负反馈环路的运放amp输出电压

的输出管mn1的漏端;

100.电容c3的另一端、pmos晶体管mp4和mp3的漏端连接地;

101.电阻r3、r4、r5和r6的另一端、电流源i2和i3的正端连接电源电压vdd。

102.所述尾电流引出单元为nmos晶体管mn8,mn8的漏端连接电容c3的一端和mn7 的源极,mn8的栅极连接电压偏置端口vb4,mn8的源极连接mn1的漏端。

103.为了稳定x节点电压,引入了稳压辅助电路,所述稳压辅助电路所占面积只有 0.1mm*0.1mm,占芯片总面积1mm*1mm的很小一部分,同时,稳压辅助电路的能耗只有0.5ma,对芯片整体能耗而言,可以忽略不计。

104.方案二、参见图6所示,将输出驱动级buff的尾电流全部注入至前置放大器tia 的输入管mn1漏端,输入管mn1漏端还同时注入补充注入电流,所述补充注入电流采用电阻或电流源注入方式;

105.且存在关系式:

106.i1=i7+is107.其中,i1为输入管mn1漏端的注入电流,i7为输出驱动级buff的尾电流,is为补充注入电流。

108.所述低功耗设计方法将尾电流通过nmos晶体管mn8引出并注入至前置放大器tia 中输入管mn1的漏端;同时,nmos晶体管mn8的漏端通过电容c3接地;

109.所述低功耗设计方法还将电阻或电流源方式形成的补充注入电流同步注入前置放大器tia中输入管mn1的漏端;

110.本方案中,将尾电流全部注入mn1漏端,但不能满足注入电流的要求,比如尾电流10ma,但mn1漏端需要注入15ma,那么剩余的5ma由电阻或电流源注入方式实现,虽然本方案中仍采用现有方案注入电流,由于尾电流的参与,采用电阻或电流源方案注入的补充注入电流已不是大电流,这样可以大幅度降低芯片的整体功耗。

111.作为实施例,请参见图10和图11,图10为补充注入电流采用电阻注入方式,图11 为补充注入电流采用电流源注入方式,同样的,输出驱动级buff还包括用于稳定x点电压的稳压辅助电路,稳压辅助电路结构与方案一相同。

112.方案三、参见图7所示,将输出驱动级buff的尾电流部分注入至前置放大器tia 的输入管mn1漏端;

113.输出驱动级buff的尾电流i7分为两部分i7=i

71

+i

72

,i

71

为注入输入管mn1漏端的尾电流,i

72

为接地的尾电流,

114.存在关系式:

115.i1=i

71

116.其中,i1为输入管mn1漏端的注入电流。

117.所述低功耗设计方法将尾电流分成两部分,一部分尾电流通过nmos晶体管mn8 引出并注入至前置放大器tia中输入管mn1的漏端,且nmos晶体管mn8的漏端通过电容c3接地;另一部分尾电流通过nmos晶体管mn9接地,具体的,mn9的漏端连接mn5、mn6的源极(x点),mn9的源极接地,mn9的栅极连接电压偏置端口vb5。

118.本方案中,若尾电流为20ma,分成两部分,其中10ma注入至输入管mn1的漏端,已满足tia注入电流要求,则将剩余10ma尾电流接地处理,不用再采用电阻或电流源方式注入大

电流,节约了芯片能耗。

119.作为实施例,参见图12所示,同样的,输出驱动级buff还包括用于稳定x点电压的稳压辅助电路,稳压辅助电路结构与方案一相同。

120.方案四、参见图8所示,将输出驱动级buff的尾电流部分注入至前置放大器tia 的输入管mn1漏端;

121.输出驱动级buff的尾电流i7分为两部分i7=i

71

+i

72

,i

71

为注入输入管mn1漏端的尾电流,i

72

为接地的尾电流;

122.输入管mn1漏端还同时注入补充注入电流,所述补充注入电流采用电阻或电流源注入方式;

123.且存在关系式:

124.i1=i

71

+is125.其中,i1为输入管mn1漏端的注入电流,is为补充注入电流。

126.所述低功耗设计方法将尾电流分成两部分,一部分尾电流通过nmos晶体管mn8 引出并注入至前置放大器tia中输入管mn1的漏端,且nmos晶体管mn8的漏端通过电容c3接地;另一部分尾电流通过nmos晶体管mn9接地;具体的,mn9的漏端连接mn5、mn6的源极(x点),mn9的源极接地,mn9的栅极连接电压偏置端口vb5。

127.所述低功耗设计方法还将电阻或电流源方式形成的补充注入电流同步注入前置放大器tia中输入管mn1的漏端;

128.本方案中,将尾电流的一部分作为tia注入电流的一部分,比如尾电流为20ma, tia注入电流需求为10.5ma,则将尾电流分出10ma注入tia中,tia所需注入电流剩余的0.5ma则采用电阻或电流源的方式注入,这种电阻或者电流源部分注入方式能够随意的修调注入电流的大小,之所以没有全部采用尾电流注入是因为尾电流是用mn8、 mn9将尾电流进行拆分,而要拆分出0.5ma小电流这种微小调整是不容易实现的,本实施方式采用这种方式调整精度高,使得tia达到最佳性能,采用这种方案也能实现避免采用电阻或电流源的方式注入大电流,节约芯片能耗。

129.作为实施例,请参见图13和图14,图13为补充注入电流采用电阻注入方式,图14 为补充注入电流采用电流源注入方式,同样的,输出驱动级buff还包括用于稳定x点电压的稳压辅助电路,稳压辅助电路结构与方案一相同。

130.虽然在本文中参照了特定的实施方式来描述本发明,但是应该理解的是,这些实施例仅仅是本发明的原理和应用的示例。因此应该理解的是,可以对示例性的实施例进行许多修改,并且可以设计出其他的布置,只要不偏离所附权利要求所限定的本发明的精神和范围。应该理解的是,可以通过不同于原始权利要求所描述的方式来结合不同的从属权利要求和本文中所述的特征。还可以理解的是,结合单独实施例所描述的特征可以使用在其它所述实施例中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1