包括防篡改电路的芯片及防篡改系统的制作方法

1.本公开涉及微电子电路,并且更具体地,涉及用于检测集成电路(ic)的篡改的电路和方法,包括防篡改电路的芯片及防篡改系统。

背景技术:

2.ic的篡改(即,芯片篡改)可包括有意地改变芯片的一部分。该改变可包括使用工具(例如,钻头、锉刀等)或化学品(例如,溶剂、蚀刻剂等)来移除材料(例如,封装)以便暴露下面的电路。一旦暴露,就可电探测电路(例如,微处理器、存储器、逻辑等)以感测信号和确定敏感信息(例如,密钥、凭证、加密货币等)。例如,通过感测暴露电路中的信号,有可能确定芯片所使用的硬件和/或软件安全措施。一旦已知,就可开发非法入侵以规避芯片上或其他类似芯片上的安全措施。在另一个示例中,通过感测暴露电路中的信号,有可能获得用于加密或通信的密钥。一旦已知,密钥就可重新用于获得对数据和/或通信的访问。可采取防篡改措施以检测芯片并且随后保护芯片免遭篡改。例如,当检测到篡改时,芯片可被配置为改变/删除敏感信息(即,数据)。为了该目的以及其他目的,重要的是提供一种用于检测篡改的装置,该装置是敏感的并且抵制被规避。本公开的实施方式就是在这种背景下出现的。

技术实现要素:

3.本实用新型旨在采取防篡改措施以检测芯片并且随后保护芯片免遭篡改。

4.在至少一个方面,本公开总体上描述了一种包括防篡改电路的芯片(即,微芯片)。该芯片包括设置在第一芯片层上的集成电路。该芯片还包括电阻器

‑

电容器电路,该电阻器

‑

电容器电路包括设置在第二芯片层上的电容器。第二芯片层上的电容器覆盖第一芯片层上的集成电路的一部分。电容器被配置为当电阻器

‑

电容器电路被物理地改变(例如,通过芯片篡改)时改变其时间常数。

5.在该方法的可能实施方式中,电阻器

‑

电容器电路包括耦接在电阻器

‑

电容器电路的输入端与输出端之间的电阻器。此外,电阻器电容器电路包括电容器,该电容器具有耦接到电阻器

‑

电容器电路的输出端的第一电极、耦接到接地电压的第二电极以及设置在第一电极与第二电极之间的绝缘体。在该可能实施方式中,电容器可以是金属氧化物金属电容器。

6.在该方法的另一个可能实施方式中,输出信号匹配至少一个标准的时间包括输入信号的转变时间与输出信号等于阈值的时间之间的时间。

7.在该方法的另一个可能实施方式中,该方法还包括对附加电阻器

‑

电容器电路重复探测、接收、测量和检测。在该可能实施方式中,基于时间检测芯片篡改可包括比较对每个电阻器

‑

电容器电路测量的时间以获得结果,以及基于该结果确定芯片篡改。

8.在另一方面,本公开总体上描述了一种系统(即,防篡改系统)。该系统包括集成电路和多个电阻器

‑

电容器电路。每个电阻器

‑

电容器电路包括覆盖集成电路的一部分的电容器。每个电容器被配置为当对应的电阻器

‑

电容器电路被物理地改变时改变其时间常数。该

系统还包括驱动器电路和计数器电路,该驱动器电路被配置为将输入信号施加到每个电阻器

‑

电容器电路,该计数器电路被配置为测量来自每个电阻器

‑

电容器电路的每个输出信号匹配一个或多个标准(即,至少一个标准)的时间。该系统还包括处理器。该处理器被配置为基于由计数器测量的时间(例如,通过比较时间)来检测芯片篡改。

9.在该系统的一个可能实施方式中,电容器是具有由氧化物隔开的叉指式电极的金属氧化物金属电容器。

10.在该系统的另一个可能实施方式中,基于由计数器测量的时间来检测芯片篡改包括比较多个电阻器

‑

电容器电路匹配至少一个标准的时间。

11.在该系统的另一个可能实施方式中,处理器进一步被配置为响应于检测到芯片篡改而改变(例如,删除)存储在系统的存储器中的数据(例如,加密密钥、密码等)。

12.本实用新型提供的包括防篡改电路的芯片及防篡改系统能够采取防篡改措施以检测芯片并且随后保护芯片免遭篡改。在以下具体实施方式及其附图内进一步解释了前述说明性实用新型内容,以及本公开的其他示例性目标和/或优点、以及实现方式。

附图说明

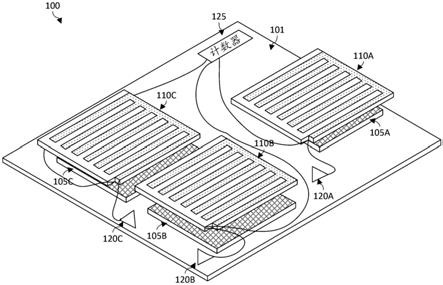

13.图1是根据本公开的可能实施方式的包括防篡改电路的芯片的透视剖面图。

14.图2是根据本公开的可能实施方式的包括防篡改电路的芯片的部分在篡改之后的横截面侧视图。

15.图3是根据本公开的可能实施方式的包括金属氧化物金属电容器的电阻器

‑

电容器电路的示意图。

16.图4是根据本公开的实施方式的防篡改系统的框图。

17.图5示意性地示出了根据本公开的防篡改电s路的第一可能实施方式。

18.图6示意性地示出了根据本公开的防篡改电路的第二可能实施方式。

19.图7a是根据本公开的可能实施方式的电阻器

‑

电容器电路在篡改之前的输出信号的基于时间的图。

20.图7b是根据本公开的可能实施方式的电阻器

‑

电容器电路在篡改之后的输出信号的基于时间的图。

21.图8包括根据本公开的实施方式的来自防篡改系统的信号的基于时间的曲线图。

22.图9是示出根据本公开的实施方式的用于检测芯片篡改的方法的流程图。

23.附图中的部件未必相对于彼此按比例绘制。相似附图标记在若干附图中表示相应的零件。

具体实施方式

24.本公开描述了用于检测芯片篡改的电路和方法。所公开的电路使用基于对输入信号的响应的主动检测。与诸如简单地使用断开的连接来检测篡改的那些其他方法相比,主动检测可是更敏感和更难规避的。所公开的芯片篡改检测方法还可保护集成电路的敏感部分(即,区域),同时使集成电路的其他部分不受保护。与试图保护整个集成电路的方法相比,该针对性的保护方法可对误警报不太敏感。此外,该方法可扩展并且可根据需要保护集成电路的尽可能多或尽可能少的部分。例如,多个电容器可覆盖集成电路的不同(即,相互

排斥的)部分。在一些实施方式中,所公开的芯片篡改检测可基于相对比较而不是基于与固定值的比较。该相对比较方法可消除对初步校准(例如,出厂设定)的需要,并且可有助于减少芯片篡改检测对电路条件(例如,温度)的变化。所公开的芯片篡改电路可使用生产集成电路已需要的工艺步骤来制造。因此,所公开的芯片篡改电路可比利用附加和/或非标准工艺步骤的其他方法更高在制造上更具成本效益。

25.图1是包括防篡改电路的芯片的透视剖面图。芯片100包括设置在第一芯片层101上的集成电路。第一芯片层101上的集成电路包括被指定用于保护(即,受保护区域)的部分105a、105b、105c(即,敏感部分)。芯片还包括防篡改电路以保护部分105a、105b、105c,该防篡改电路包括针对每个部分的电阻器

‑

电容器电路。每个电阻器

‑

电容器电路包括设置在第二芯片层上的电容器110a、110b、110c以覆盖集成电路的相应部分。如图所示,覆盖集成电路的相应部分的电阻器电容器电路可包括设置在集成电路的一部分之上的电阻器

‑

电容器电路。换句话讲,覆盖物可包括当电阻器

‑

电容器电路的占有面积被投影到集成电路上时集成电路位于电阻器

‑

电容器电路的占有面积内的部分。在一些可能实施方式中,每个电阻器

‑

电容器电路的电阻器与第二芯片层上的电容器110a、110b、110c结合,而在其他可能实施方式中,每个电阻器

‑

电容器电路的电阻器与第一芯片层101上的集成电路结合。

26.在可能实施方式中,芯片包括被配置为生成输入信号并且将其传输至电阻器

‑

电容器电路的输入端的一个或多个(即,至少一个)驱动器电路120a、120b、120c。例如,第一芯片层101上的集成电路可包括一个或多个驱动器电路120a、120b、120c,如图1所示。另外,集成电路可包括一个或多个计数器电路。如图1所示,计数器电路125耦接到电阻器

‑

电容器电路的输出端。计数器电路125被配置为基于来自每个电阻器

‑

电容器电路的输出信号来测量对应于每个电阻器

‑

电容器电路的rc时间常数(即,时间常数)的时间。在可能实施方式中,控制驱动器电路和计数器电路依次驱动(即,探测)和测量(即,感测)所有电阻器

‑

电容器电路。在另一个可能实施方式中,每个电阻器

‑

电容器电路耦接到专用驱动器电路和专用计数器电路。在该实施方式中,可同时驱动和测量(即,并行)所有电阻器

‑

电容器电路。在又一个可能实施方式中,可仅驱动和测量(即,依次或并行)电阻器

‑

电容器电路的子集(例如,一个)。例如,当仅集成电路的一部分包括敏感数据时,则可能仅需要驱动和测量保护该一部分的电阻器

‑

电容器电路。

27.图2是根据本公开的可能实施方式的芯片的一部分的横截面侧视图。如前所述,集成电路设置在第一芯片层201上。集成电路包括用于保护(即,受保护区域、敏感区域等)的集成电路部分206。例如,集成电路部分206可包括可被探测以获得被存储和/或传送的敏感数据(例如,密码、密钥等)的器件(例如,存储器)和/或电路迹线。芯片还可包括封装件203,该封装件包含、保护和/或支持集成电路。

28.芯片篡改可包括获得对受保护区域205中第一芯片层201的物理访问,以使得探针221可与电路特征部(例如,迹线、焊盘、通孔、引脚、导线等)接触以将电信号耦接到集成电路部分206或从其耦接。为了检测该芯片篡改,芯片还包括第二芯片层202,该第二芯片层包括电容器210。电容器210覆盖(例如,在其上方)受保护区域205,以获得对集成电路部分206的物理访问,需要在封装件203中创建孔220a,以及进一步在电容器210中创建孔220b。孔220b可改变电容器210的电特性(例如,电阻、电容)。因此,电容器210的电特性的改变可对应于芯片篡改。此外,电容器210的电特性的改变程度可对应于芯片篡改的程度。

29.图3是根据本公开的可能实施方式的电阻器

‑

电容器电路300的示意图。电阻器

‑

电容器电路300包括电阻器305。电阻器305耦接在电阻器

‑

电容器电路300的输入端301与输出端302之间。电阻器可以各种方式实现。电阻器可包括在集成电路中,包括在集成电路与电容器之间的连接中,或者作为电容器本身的一部分被包括。电阻器

‑

电容器电路300还包括电容器310。电容器包括耦接到电阻器

‑

电容器电路300的输出端302的第一电极315。电容器还包括耦接到接地电压303的第二电极316。电容器还包括第一电极315与第二电极316之间的绝缘体。

30.在可能实施方式中,第一电极315具有第一多个指状部分(例如,如图3所示的水平部分),并且第二电极具有第二多个指状部分(例如,如图3所示的水平部分)。第一多个指状部分和第二多个指状部分彼此交叉并且在同一平面内。第一多个指状部分和第二多个指状部分具有设置在相邻指状部分之间的氧化物层。换句话讲,电容器为金属氧化物金属电容器(即,mom),其具有由氧化物隔开的叉指式电极,诸如图3所示。金属氧化物金属电容器可有利地具有平面区域,该平面区域的尺寸可被设定成覆盖第一芯片层的特定部分。当电阻器

‑

电容器电路包括金属氧化物金属电容器时,电阻器

‑

电容器电路可称为r

‑

mom。

31.本公开不限于mom的交叉指状实施方式,因为存在由氧化物隔开的第一电极和第二电极的许多可能平面构型,该氧化物可用作电阻器

‑

电容器电路300中的电容器。例如,具有由氧化物隔开的两个电极的平面螺旋(例如,正方形螺旋)可形成mom。在另一个示例中,具有相同形状(例如,正方形、矩形、三角形、圆形等)的由氧化物隔开的一对平面同心电极可形成mom。

32.可用输入信号350探测电阻器

‑

电容器电路以生成对应的输出信号360,该输出信号可由其形状表征。例如,输入信号可以是阶跃函数,而输出信号可以是低通滤波(例如,延迟的)版本的阶跃函数(即rc阶跃响应)。例如,如果输入信号是从零伏(即,低)阶跃到电压(vs)(即,高)的电压,则输出信号(vout)可由以下等式给出。

33.vout=vs(1

‑

e

‑

t/rc

)

ꢀꢀ

(1)

34.电阻器

‑

电容器电路的时间常数可被定义为输出信号达到其最大值的63.2%(即,1

‑

exp(

‑

1)

×

100%)所花费的时间(来自输入信号的阶跃转变)。也就是说,电阻器

‑

电容器电路的时间常数为电阻(r)乘以电容(c)(即,时间常数=rc)。因此,由于前述篡改,电阻器

‑

电容器电路的电容和/或电阻的改变可被感测为输出信号满足这些标准所需时间的对应改变(即,可被感测为时间常数的改变)。用于测量对应于时间常数的时间的标准(例如,阈值)可随实施方式而变化,并且不限于上述标准。此外,输入信号可不同于上述阶跃函数。例如,输入信号可为脉冲(例如,电压脉冲),并且计数器可测量输出信号衰减到阈值(例如,电压)所花费的时间(来自脉冲)。

35.图4是根据本公开的实施方式的防篡改系统(即,系统)的框图。系统400包括多个电阻器

‑

电容器电路410a、410b、410c。系统400还包括驱动器电路420和计数器电路430,该驱动器电路被配置为将输入信号施加到电阻器

‑

电容器(rc)电路410a、410b、410c中的每一个电阻器

‑

电容器(rc)电路,该计数器电路被配置为响应于输入信号而从电阻器

‑

电容器电路410a、410b、410c中的每一个电阻器

‑

电容器电路接收输出信号。计数器电路430可被进一步配置为基于至少一个标准来测量与输出信号相关联的时间。测量的时间与电阻器

‑

电容器电路的相应时间常数相关(例如,相等)。一个或多个标准可包括启动计数器的阈值(例

如,输入信号从低转变成高)和停止计数器的阈值(例如,输出信号匹配预定值)。该系统还可包括处理器440。处理器440可被软件指令(即,应用程序)配置为协调和控制时间的测量并且基于测量的时间来检测芯片篡改。

36.处理器440可被不同地实施以执行上述功能。例如,处理器可实现为微处理器、控制器、状态机或逻辑电路。处理器可与存储器450通信并且利用该存储器。例如,存储器450可以是被配置为存储软件指令、测量标准以及来自当前和过去测量的结果的非暂态计算机可读介质。在可能实施方式中,防篡改系统包括替代处理器的状态机(即,处理器实现为状态机)。在另一个可能实施方式中,防篡改系统包括处理器和状态机。

37.处理器440可被配置为使用多种算法来检测芯片篡改。例如,可比较测量的时间以检测篡改。在通过相对比较方法的检测中,可假设所有电阻器

‑

电容器电路410a、410b、410c被制造成具有大致相同的时间常数。处理器被配置为比较测量的时间以确定一个或多个测量的时间是否与大多数测量的时间不同(例如,通过阈值量)。在另一个示例中,测量的时间可与参考时间比较。在通过固定比较方法的检测中,处理器可被配置为比较每个测量的时间与预定时间,并且当测量的时间从预定时间偏离(例如,偏离了阈值量)时检测篡改。虽然可使用任一种方法,但是通过相对比较的检测可提供一些优点。例如,影响所有电阻器

‑

电容器电路的变化(例如,由于老化、温度等)可能不影响检测。此外,不需要测量和存储参考时间。

38.如所提及,处理器440可被配置为基于芯片篡改的检测来采取动作。例如,在检测到芯片篡改时,处理器可被配置为改变芯片的功能(例如,关断、传输警报等),或者可改变/删除敏感数据(例如,存储在系统的存储器450中)。

39.图5示意性地示出了防篡改电路的第一可能实施方式。防篡改电路500包括耦接到多个电阻器

‑

电容器电路520的输入端的驱动器电路510,同时多个电阻器

‑

电容器电路520的输出端耦接到计数器电路530。驱动器电路510包括至少一个数字信号源511a、511b、511c。数字信号源511a、511b、511c被配置为生成输入信号,每个输入信号包括信号改变,诸如第一信号电平(例如,低)与第二信号电平(例如,高)之间的数字转变。数字信号源可各自实现为锁存器或触发器。另选地,时钟可根据测试协议提供信号改变(例如,低/高、高/低)以确定是否已发生对电阻器

‑

电容器电路520的篡改。测试协议可包括测试电阻器

‑

电容器电路以用于篡改的时间,并且可进一步指定对电阻器

‑

电容器电路进行充电和放电以测量电阻器

‑

电容器电路的时间常数的时间(在每次测试期间)。每个电阻器

‑

电容器电路被配置为将信号改变延迟了(例如,减慢、lp滤波)对应于电阻器

‑

电容器电路的时间常数(即,rc)的量。计数器电路530包括输出复用器531,该输出复用器被配置为基于输出复用器的状态将输出信号从多个电阻器

‑

电容器电路路由至计数器532。例如,输出复用器531可设为处于第一状态(例如,由选择器信号)以将输出信号从第一电阻器

‑

电容器电路输出到计数器,设为处于第二状态以将输出信号从第二电阻器

‑

电容器电路输出到计数器,等等。计数器电路530还包括计数器532,该计数器可基于第一事件(例如,输入信号的信号改变)而触发以启动计数,和基于第二事件(例如,匹配值的输出信号)而触发以停止计数。计数器532可输出对应于时间测量的计数。

40.图6示意性地示出了防篡改电路600的第二可能实施方式。防篡改电路600包括耦接到多个电阻器

‑

电容器电路620的输入端的驱动器电路610,同时多个电阻器

‑

电容器电路

620的输出端耦接到计数器电路630。驱动器电路610可包括输入复用器612,该输入复用器被配置为基于输入复用器612的状态将输入信号(rc_in)从数字信号源611路由至电阻器

‑

电容器电路的输入端。另选地,不包括输入复用器,并且每个电阻器

‑

电容器电路由对应的驱动器电路独立地(例如,并行地)驱动。计数器电路630可包括输出复用器631,该输出复用器被配置为基于输出复用器631的状态将输出信号(rc_out)从电阻器

‑

电容器电路的输出端路由至计数器632。另选地,不包括输出复用器,并且每个电阻器

‑

电容器电路将输出独立地(例如,并行)传输至对应的计数器。输入多路复用器和输出多路复用器的状态可由选择器源621生成的选择器信号(选择器)控制,该选择器源可实现为锁存器或触发器。通过使用来自控制源613和逻辑门(例如,与门)614的控制信号(控制),计数器可在输入信号(例如,从低到高)转变的同时启动(即,触发)。

41.图7a是根据本公开的可能实施方式的电阻器

‑

电容器电路(r

‑

mom)在篡改之前的输出信号的基于时间的曲线图。在曲线图中,计数器的状态在输入信号703和输出信号702下方示出。计数器在来自驱动器的输入信号从低电平转变到高电平的开始时间705之前处于零状态701a。在开始时间705之后,计数器进入计数状态701b(计数),在此期间计数器以固定速率计数。计数器继续计数,直到输出信号702达到阈值或改变了阈值量(v

t

)的停止时间710。在停止时间之后,计数器进入固定状态701c,其中计数器在篡改之前输出对应于r

‑

mom的时间常数的值(val_y)。

42.图7b是根据本公开的可能实施方式的电阻器

‑

电容器电路在篡改之后的输出信号的基于时间的曲线图。在曲线图中,计数器的状态在输入信号703和输出信号702下方示出。计数器在来自驱动器的输入信号从低电平转变到高电平的开始时间705之前处于零状态701a。在开始时间705之后,计数器进入计数状态701b(计数),在此期间计数器以固定速率计数。计数器继续计数,直到输出信号702达到阈值或改变了阈值量(v

t

)的停止时间710。在停止时间之后,计数器进入固定状态701c,其中计数器在篡改之后输出对应于r

‑

mom的时间常数的值(val_x)。在篡改之前和之后返回的计数(即,测量的时间)可基于r

‑

mom中的电容改变而不同(即,val_y≠val_x)。例如,r

‑

mom中的孔可减小电容,从而减小篡改之后的时间常数。

43.图8包括根据本公开的实施方式的来自防篡改系统的信号的基于时间的曲线图。仅作为示例,信号示出了另选方式以确定测量时间,并且还示出了通过相对比较如何执行检测。输入信号被示出为具有第一转变810,然后(在时段815之后)是第二转变811。还示出了三个输出信号。第一输出信号821来自具有零(0)百分比(%)篡改的r

‑

mom。第二输出信号822来自具有5%篡改的r

‑

mom。第三输出信号823来自具有50%篡改的r

‑

mom。具有由氧化物隔开的叉指式电极的金属氧化物金属电容器的篡改百分比可以是指状部分由于篡改而短路或断开的数量(作为百分比)。

44.每个输出信号可与阈值电平820比较以生成相应的计数器开/关信号(例如,用于计数器)。例如,当输出信号高于阈值电平时,计数器开/关信号可为高电平(即,高),并且当输出信号低于阈值电平时,计数器开/关信号可为低电平(即,低)。计数器可被配置为仅在计数器开/关信号为低时进行计数。由于篡改造成的电容差值,由每个计数器开/关信号导致的每个计数不同。例如,0%改变的mom的第一计数为38,5%改变的mom的第二计数为36,并且50%改变的mom的第三计数为20。曲线图示出了篡改的数量可被表征,并且更多的篡改

产生更多的计数差值。因此,当计数差值大时,可检测到篡改。例如,当计数与平均计数之间的差值高于阈值时,可对与计数异常值相关联的mom检测篡改。

45.图9是示出根据本公开的实施方式的用于检测芯片篡改的方法的流程图。方法900包括用输入信号探测910电阻器

‑

电容器电路,以及从电阻器

‑

电容器电路接收920对应的输出信号。该方法还包括测量930输出信号匹配至少一个标准的时间。例如,当输出信号高于或低于阈值时,可触发计数器进行计数。在测量时间之后,该方法还可包括选择940附加电阻器

‑

电容器电路(例如,一个尚未探测的),以及重复探测910、接收920和测量930。可重复该过程,直到已测量到来自所有电阻器

‑

电容器电路的时间。该方法还包括基于时间检测950芯片篡改。例如,该方法还可包括比较对每个电阻器

‑

电容器电路测量的时间以获得结果(例如,与平均值的差值),以及基于该结果确定芯片篡改。

46.本公开上描述了一种用于检测芯片篡改的方法。该方法包括探测电阻器

‑

电容器电路,该电阻器

‑

电容器电路包括用输入信号覆盖集成电路的一部分的电容器。该方法还包括从电阻器

‑

电容器电路接收输出信号。该方法还包括测量输出信号匹配至少一个标准的时间。该时间对应于电阻器

‑

电容器电路的时间常数。该方法包括基于时间检测芯片篡改(即,因为时间对应于时间常数,并且时间常数可通过篡改电容器而从初始值改变)。

47.在说明书和/或附图中,已经公开了典型的实施方案。本公开不限于此类示例性实施方案。术语“和/或”的使用包括一个或多个相关联列出条目的任意组合和所有组合。附图是示意性表示并且因此未必按比例绘制。除非另有说明,否则特定术语已用于通用和描述性意义,而非用于限制的目的。

48.除非另外定义,否则本文所用的所有技术和科学术语具有与本领域的普通技术人员通常理解的含义相同的含义。可以在本公开的实践或测试中使用与本文所述的那些类似或等同的方法和材料。如本说明书中以及所附权利要求书中所用,单数形式“一个”、“一种”、“该”包括多个指代物,除非上下文另有明确规定。如本文所用的术语“包含”及其变型形式与术语“包括”及其变型形式同义地使用,并且是开放式的非限制性术语。本文所用术语“任选的”或“任选地”是指随后描述的特征、事件或情况可能发生或可能不发生,并且该描述包括所述特征、事件或情况发生的实例和不发生的实例。范围在本文中可以表达为从“约”一个特定值,和/或到“约”另一个特定值。当表达这样的范围时,一个方面包括从一个特定值和/或到另一个特定值。类似地,当值通过使用先行词“约”表达为近似值时,应当理解,该特定值形成另一个方面。还应当理解,每个范围的端点相对于另一个端点是重要的,并且独立于另一个端点。

49.一些实施方式可使用各种半导体处理和/或封装技术来实现。一些实施方式可使用与半导体衬底相关联的各种类型的半导体处理技术来实现,该半导体衬底包含但不限于,例如硅(si)、砷化镓(gaas)、氮化镓(gan)、碳化硅(sic)等。

50.虽然所描述的实施方式的某些特征已经如本文所述进行了说明,但是本领域技术人员现在将想到许多修改形式、替代形式、变化形式和等同形式。因此,应当理解,所附权利要求书旨在涵盖落入实施方式的范围内的所有此类修改形式和变化形式。应当理解,这些修改形式和变化形式仅仅以举例而非限制的方式呈现,并且可以进行形式和细节上的各种变化。除了相互排斥的组合以外,本文所述的装置和/或方法的任何部分可以任意组合进行组合。本文所述的实施方式可包括所描述的不同实施方式的功能、部件和/或特征的各种组

合和/或子组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1