传输电路的制作方法

1.本公开涉及被绝缘的两区域间的信号传输。

背景技术:

2.在商用电源、电机、计测器等的车载、工业、医疗设备等的系统中,以(i)为了保护人体或设备不受浪涌电流或高电压,或(ii)防止噪声的分离引起的错误动作、(iii)保护电位差较大的区域间的信号传输中的晶体管等为目的,半导体芯片间的数字信号传输被要求较高的电气绝缘性。

3.作为保证绝缘性的信号传输,提出了无线方式、光耦合方式、电容器方式、变压器方式、gmr(giant magneto resistive:巨磁电阻效应)方式等。

4.在介在有绝缘隔层的数字信号传输中,即使在输入逻辑信号没有转变的情况下,也可能因公共电压(基准电压)的较大变化等的外来噪声而导致错误动作发生,在初级侧(发送tx侧)和次级侧(接收rx侧)之间的逻辑信号电平可能会发生失配性的问题。

5.在医疗设备、航空/宇宙设备或车载/工业设备等被要求可靠性的系统中,难以允许该问题。

6.因此,通过绝缘隔层间的通信ic,实施为了提高共模瞬变抗扰度(cmti:common mode transient immunity)的电气对策,并采取系统性的对策。

7.作为系统性的对策,提出了以下的方案。

8.(现有例1)

9.现有例1,即使在一定期间没有输入逻辑转变,tx侧通过发送基于计时器的定期性的刷新脉冲,来补充发送失败或无信号时的tx-rx间逻辑失配。在rx侧,在一定期间没有逻辑信号转变的情况下,通过监视计时器将输出设定为预先决定的安全电平。

10.(现有例2)

11.在现有例2中,采用ook(on-off keying:通断键控)或fsk(frequency shift keying:频移键控),通常能够判定为l/h任一个的逻辑状态。即使是错误动作导致的信号变化,也可以立即订正为正确的值。

12.作为电气对策,通常采用以下的方案。

13.·

采用以不会发生电场导致的初级-次级间噪声传递的方式的磁场耦合的变压器。

14.·

通过差动信号进行初级-次级间的信号发送。这在cmti较低的电容器方式(电场耦合)中几乎是必须的。

15.·

增大发送功率,提高s/n比。该方法由于电力增大而存在限制。

16.·

基于滤波器除去噪声、采用磁滞电路等,以标准的电路设计应对。但是,在频率或电压电平的s/n比较低的情况下存在限制。

17.现有技术文献

18.专利文献

19.专利文献1:美国专利第8873644号公报

20.专利文献2:美国专利第9853749号公报

21.非专利文献

22.非专利文献1:wei zhang,mateo begue,"common mode transient immunity(cmti)for ucc2122x isolated gate drivers",texas instruments,application report:slua909,august 2018

技术实现要素:

23.发明要解决的技术问题

24.本发明的发明人针对现有的对策进行研究,最终认识到以下的技术问题。

25.(现有例1)

26.初级-次级间的逻辑失配时,会发生计时器周期导致的回复延迟。此外,在刷新周期较长的情况下,需要允许长时间的逻辑失配状态。另一方面,若缩短刷新周期,则电力消耗会增加。而且,难以根据状况决定变化的其最适合周期。

27.此外,即使持续发送失败,rx侧也没有被订正为正确的信号电平。原本rx侧监视计时器并不是以逻辑匹配为目的,是为了故障等发送不能状态的fail-safe功能而设置的。

28.tx、rx均需要计时器用的稳定工作的周边电路(振荡器等),在无信号时也消耗电力,面积成本也增大。

29.(现有例2)

30.为了发送载波频率而电力消耗增大,即便在无信号时也会发生电力消耗。此外解调电路中,偏置电路等需要恒定电流,面积成本也增大。并且,载波频率导致的emi(electro magnetic interference:电磁干扰)的恶化、或者对策电路(扩频)的电力消耗或电路面积的增大是不可避免的。

31.这样,现有的方法过度复杂,需要大量部件,需要较大面积等,存在许多缺点。因此,这些电路实现困难,成为低成本化、低电力消耗化的障碍。

32.本公开是鉴于这样的技术问题而得到的,其一方案的例示性的目的之一在于,提供一种能够以低电力消耗消除逻辑失配的绝缘信号传输电路。

33.用于解决技术问题的方法

34.本公开的一方案涉及传输电路。传输电路包括:绝缘隔层;初级侧发射器,响应于输入信号的转变,驱动绝缘隔层的初级侧输入;次级侧接收器,生成具有与在绝缘隔层的次级侧输出产生的信号对应的逻辑值的输出信号;次级侧发射器,根据输出信号,驱动绝缘隔层的次级侧输入;以及初级侧接收器,生成具有与在绝缘隔层的初级侧输出产生的信号对应的逻辑值的返回信号。初级侧发射器重复绝缘隔层的初级侧输入的驱动,直到输入信号与返回信号的逻辑值一致为止。

35.此外,上述构成要素的任意组合、或将本公开的表现在方法、装置等之间转换的方案作为本发明的方案也是有效的。

36.发明效果

37.根据本公开的一方案,可以低电力消耗地解除逻辑失配。

附图说明

38.图1是实施方式的传输电路的电路图。

39.图2是图1的传输电路的正常时的时序图。

40.图3是图1的传输电路的错误时的时序图。

41.图4是实施例1的传输电路的框图。

42.图5是说明实施例1的信号传输的时序图。

43.图6是示出初级侧发射器的结构例的电路图。

44.图7是示出初级侧发射器的具体的结构例的电路图。

45.图8是示出次级侧接收器的结构例的电路图。

46.图9是示出传输电路的整体的结构例的电路图。

47.图10的(a)~(c)是示出图9的传输电路的动作的时序图。

48.图11的(a)、(b)是实施例2的传输电路的电路图。

49.图12的(a)、(b)是说明在图9的传输电路中产生的问题的时序图。

50.图13是示出实施例3的传输电路的初级侧的结构的电路图。

51.图14是示出实施例3的传输电路的次级侧的结构的电路图。

52.图15是示出实施例3的传输电路的动作的时序图。

53.图16是变形例1的次级侧接收器的电路图。

54.图17是变形例2的次级侧接收器的电路图。

55.图18是具备传输电路的绝缘转换器的电路图。

56.图19是具备传输电路的半桥式转换器的电路图。

具体实施方式

57.(实施方式的概要)

58.说明本公开的几个例示性的实施方式的概要。该概要作为后续的详细说明的前言,以实施方式的基本性理解为目的,简要说明1个或多个实施方式的几个概念,并不在于限定发明或公开的范围。此外,该概要并不是应考虑的所有的实施方式的统括性的概要,并不在于限定实施方式的不可或缺的构成要素。为了方便起见,“一实施方式”有时用作指示本说明书公开的一个实施方式(实施例或变形例)或多个实施方式(实施例或变形例)。

59.一实施方式的传输电路包括:绝缘隔层;初级侧发射器,响应于输入信号的转变,驱动绝缘隔层的初级侧输入;次级侧接收器,生成具有与在绝缘隔层的次级侧输出产生的信号对应的逻辑值的输出信号;次级侧发射器,根据输出信号,驱动绝缘隔层的次级侧输入;以及初级侧接收器,生成具有与在绝缘隔层的初级侧输出产生的信号对应的逻辑值的返回信号。初级侧发射器重复绝缘隔层的初级侧输入的驱动,直到输入信号和返回信号的逻辑值一致。

60.在该传输电路中,通过追加从次级侧向初级侧回发信息的返回信道,初级侧发射器能够知道信息是否正确地传递。而且,通过重复信号的传输直到正确地传递信息为止,能够可靠地向次级侧传递信号。因信号的再发送为最小限度,从而能够以较小的电力消耗,取得匹配。此外,绝缘隔层的初级侧输入与初级侧输出可以是独立的端口,也可以是同一端口。同样地,绝缘隔层的次级侧输入与次级侧输出可以是独立的端口,也可以是同一端口。

61.在一实施方式中,初级侧发射器可以包括:第一比较电路,比较输入信号与返回信号的逻辑值;第一振荡电路,根据第一比较电路的比较结果,控制振荡、停止;以及第一输出部,根据输入信号与第一振荡电路生成的第一脉冲信号而驱动绝缘隔层的初级侧输入。根据该结构,可以在输入信号和返回信号不一致的期间,反复驱动绝缘隔层的初级侧输入。

62.在一实施方式中,第一振荡电路也可以包含环形振荡器。

63.在一实施方式中,也可以是,初级侧发射器在输入信号为高时,以第一极性,对绝缘隔层的初级侧进行脉冲驱动,当输入信号为低时,以第二极性,对绝缘隔层的初级侧进行脉冲驱动。

64.在一实施方式中,绝缘隔层也可以包含第一变压器,其初级绕组与初级侧发射器连接,次级绕组与次级侧接收器连接。初级侧发射器可以在输入信号为高时,向第一变压器的初级绕组供给第一极性的脉冲电流,当输入信号为低时,生成第二极性的脉冲电流。次级侧接收器可以包括:锁存电路,置位端子与第一变压器的次级绕组的一端连接,复位端子与变压器的次级绕组的另一端连接;第一开关,被设置于产生公共电压的公共电压节点与置位端子之间,在锁存电路的输出为高时接通;以及第二开关,被设置于公共电压节点和复位端子之间,当锁存电路的输出为低时接通。

65.根据该结构,根据锁存电路的状态,控制第一开关及第二开关,通过控制第一变压器的次级绕组的状态,能够以一个变压器,实现与脉冲置位/复位型的传输电路等价的动作。该结构具有脉冲置位/复位型的优点,并且变压器为一个即可,从而可以减小电路面积,此外还从两个变压器间的时滞偏差导致的传输速度限制中解放,因此能够进行进一步的高速传输。

66.在一实施方式中,次级侧接收器还可以具备开关控制部,其根据锁存电路的状态控制第一开关及第二开关。开关控制部在第一极性的脉冲电流的转变结束后断开第二开关,在第二极性的脉冲电流的转变结束后断开第一开关。由此,可以抑制次级绕组的端子电压跳变,可以提高稳定性。

67.在一实施方式中,开关控制部可以在第一开关接通后,在经过规定时间后断开第二开关,在第二开关接通后,在经过规定时间后断开第一开关。由此,通过插入第一开关和第二开关双方接通的期间,固定置位端子、复位端子的电压,从而可以禁止锁存电路的状态转变,可以使电路动作进一步稳定。

68.在一实施方式中,初级侧发射器也可以在输入信号与返回信号的逻辑值一致后,追加地进行一次绝缘隔层的初级侧输入的驱动。次级侧发射器可以在当前的输出信号与前一次的输出信号不一致的期间,重复绝缘隔层的次级侧输入的驱动。根据该结构,次级侧发射器在正确地传输返回信号后,停止动作,对返回信道的异常也能够具有耐性。

69.在一实施方式中,次级侧发射器可以包括:第二比较电路,比较输出信号的前次的逻辑值与输出信号的当前的逻辑值;第二振荡电路,根据第二比较电路的比较结果,控制振荡、停止;以及第二输出部,在第二振荡电路的振荡时,根据第二振荡电路生成的第二脉冲信号驱动绝缘隔层的次级侧输入。

70.在一实施方式中,传输电路还可以进一步具备从次级侧接收器的输出中除去尖峰脉冲的尖峰脉冲除去电路。

71.在一实施方式中,也可以是,公共电压为接地电压,第一开关及第二开关为nmos晶

体管。

72.在一实施方式中,也可以是,公共电压为电源电压,第一开关及第二开关为pmos晶体管。

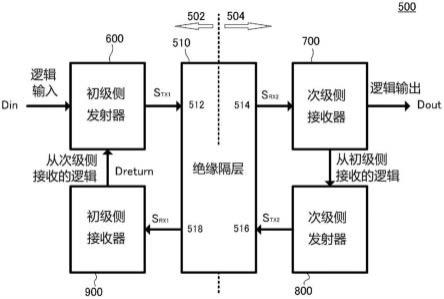

73.在一实施方式中,锁存电路可以包括斜交叉连接的第一nor门以及第二nor门。

74.在一实施方式中,锁存电路可以包括斜交叉连接的第一nand门以及第二nand门。

75.在一实施方式中,也可以是,公共电压为接地电压,第一开关及第二开关为nmos晶体管。传输电路还可以包括:第一逆变器,在输入节点接收锁存电路的反相输出,输出节点与第一开关的栅极连接;以及第二逆变器,在输入节点接收锁存电路的输出,输出节点与第二开关的栅极连接。

76.在一实施方式中,也可以是,公共电压为接地电压,第一开关及第二开关为nmos晶体管。传输电路还可以包括:第一nand门,在第一输入节点接收锁存电路的反相输出,输出节点与第一开关的栅极连接;第一延迟电路,延迟第一nand门的输出;第二nand门,在第一输入节点接收锁存电路的输出,在第二输入节点接收第一延迟电路的输出,输出节点与第二开关的栅极连接;以及第二延迟电路,延迟第二nand门的输出,供给至第一nand门的第二输入节点。

77.在一实施方式中,也可以是,公共电压为电源电压,第一开关及第二开关为pmos晶体管。传输电路还可以包括:第三逆变器,在输入节点接收锁存电路的输出,输出节点与第一开关的栅极连接;以及第四逆变器,在输入节点接收锁存电路的反相输出,输出节点与第二开关的栅极连接。

78.(实施方式)

79.下面,针对优选的实施方式参照附图进行说明。对于各附图所示的相同或同等的构成要素、部件、处理,标注相同的附图标记,适当省略重复的说明。另外,实施方式并不用于限定发明而是例示,并非实施方式记述的所有特征或其组合都是发明的本质部分。

80.在本说明书中,所谓“部件a与部件b连接的状态”,包括部件a和部件b物理地直接地连接的情况,还包括部件a和部件b经由对它们的电连接状态不产生实质影响的、或不损害通过它们的耦合所实现的功能或效果的其他部件间接地连接的情况。

81.同样地,所谓“部件c被设置在部件a和部件b之间的状态”是指,除直接连接部件a和部件c,或直接连接部件b和部件c的情况外,还包含对它们的电连接状态不产生实质影响地、或不损害通过它们的耦合所实现的功能或效果地、经由其他部件间接地连接的情况。

82.图1是实施方式的传输电路500的电路图。传输电路500包括绝缘隔层510、初级侧发射器600、次级侧接收器700、次级侧发射器800、初级侧接收器900。传输电路500在初级侧502接收输入信号d

in

,在次级侧504产生具有与输入信号d

in

对应的逻辑值的输出信号d

out

。

83.绝缘隔层510由变压器或电容器等无源元件所构成,确保初级侧502与次级侧504之间的电气绝缘。绝缘隔层510具有初级侧输入512、次级侧输出514、次级侧输入516、初级侧输出518。驱动初级侧输入512时,次级侧输出514的电气状态变化。同样地驱动次级侧输入516时,初级侧输出518的电气状态变化。此外,初级侧输入512与初级侧输出518可以为同一端口,次级侧输出514与次级侧输入516可以为同一端口。

84.初级侧发射器600响应于输入信号d

in

的转变,驱动绝缘隔层510的初级侧输入512。在绝缘隔层510的次级侧输出514,产生与初级侧发射器600的驱动对应的电气信号s

rx2

。初

级侧发射器600的驱动形态(其可以作为驱动信号s

tx1

的图案、波形、极性来理解)在输入信号d

in

从低转变为高的情况、及输入信号d

in

从高转变为低的情况下是不同的,其结果,在次级侧输出514,产生能够区别的不同形式的电气信号s

rx2

。

85.次级侧接收器700生成在绝缘隔层510的次级侧输出514产生的电气信号s

rx2

的形态,即具有与次级侧输出514的电气状态对应的逻辑值的输出信号d

out

。信号正常传输时,输出信号d

out

的逻辑值与输入信号d

in

的逻辑值是一致的。

86.初级侧发射器600及次级侧接收器700形成将输入信号d

in

从初级侧502传输给次级侧504的前向信道。

87.次级侧发射器800在输出信号d

out

变化时,驱动绝缘隔层510的次级侧输入516。在绝缘隔层510的初级侧输出518,产生与次级侧发射器800的驱动对应的电气信号s

rx1

。次级侧发射器800的驱动形式(作为驱动信号s

tx2

的图案、波形或极性进行把握)在输出信号d

out

从低转变到高的情况、及输出信号d

out

从高转变到低的情况下是不同的,其结果,在初级侧输出518产生能够区别的不同形式的电气信号s

rx1

。

88.初级侧接收器900生成与在绝缘隔层510的初级侧输出518产生的信号s

rx1

的形式,即具有与初级侧输出518的电气状态对应的逻辑值的返回信号d

return

。

89.次级侧发射器800及初级侧接收器900形成将输出信号d

out

从次级侧504返回至初级侧502的返回信道。

90.初级侧发射器600重复绝缘隔层510的初级侧输入512的驱动,直到输入信号d

in

与返回信号d

return

的逻辑值一致。

91.此外,电气信号s

tx1

、s

rx2

、s

tx2

、s

rx1

可以是电压信号,也可以是电流信号。

92.以上为传输电路500的基本结构。接着说明其动作。

93.图2是图1的传输电路500的正常时的时序图。在时刻t0,输入信号d

in

从低转变到高时,初级侧发射器600生成第一状态的电气信号s

tx1

。其结果,在绝缘隔层510的次级侧输出514,产生第一状态的电气信号s

rx2

。次级侧接收器700在检测到第一状态的电气信号s

rx2

后,输出高的输出信号d

out

。

94.次级侧发射器800在输出信号d

out

转变到高后,产生第一状态的电气信号s

tx2

。其结果,在绝缘隔层510的初级侧输出518,产生第一状态的电气信号s

rx1

。初级侧接收器900检测到第一状态的电气信号s

rx1

后,输出高的返回信号d

return

。

95.当传输电路500正常工作时,输入信号d

in

转变为高后,返回信号d

return

立即转变为高,输入信号d

in

与返回信号d

return

的逻辑值一致。因此,初级侧发射器600停止第一状态的电气信号s

tx1

的生成,等待下一输入信号d

in

的转变。

96.在时刻t1,输入信号d

in

从高转变到低时,初级侧发射器600生成第二状态的电气信号s

tx1

。其结果,在绝缘隔层510的次级侧输出514,产生第二状态的电气信号s

rx2

。次级侧接收器700在检测到第二状态的电气信号s

rx2

后,输出低的输出信号d

out

。

97.次级侧发射器800在输出信号d

out

转变为低时,产生第二状态的电气信号s

tx2

。其结果,在绝缘隔层510的初级侧输出518,产生第二状态的电气信号s

rx1

。初级侧接收器900在检测到第二状态的电气信号s

rx1

后,输出低的返回信号d

return

。

98.当传输电路500正常工作时,输入信号d

in

转变到低后,返回信号d

return

立即转变为低,输入信号d

in

与返回信号d

return

的逻辑值一致。因此,初级侧发射器600停止第二状态

的电气信号s

tx1

的生成,将下一输入信号d

in

的转变待机。

99.图3是图1的传输电路500的错误时的时序图。在时刻t0,输入信号d

in

从低转变至高时,初级侧发射器600生成第一状态的电气信号s

tx1

。

100.假定由于某种异常,在绝缘隔层510的次级侧输出514,没有产生第一状态的电气信号s

rx2

。次级侧接收器700由于没有检测到第一状态的电气信号s

rx2

,因此次级侧接收器700的输出信号d

out

维持为低。

101.此时,由于没有发生输出信号d

out

的变化,次级侧发射器800不驱动绝缘隔层510的次级侧输入516。因此,绝缘隔层510的初级侧输出518没有产生状态变化,初级侧接收器900的输出即返回信号d

return

维持为低。

102.返回信号d

return

与输入信号d

in

的逻辑值不一致。因此,初级侧发射器600在时刻t1再次产生第一状态的电气信号s

tx1

。假定此时也由于某种异常,在绝缘隔层510的次级侧输出514,没有产生第一状态的电气信号s

rx2

。此时也与前一次同样地,次级侧接收器700由于不能检测到第一状态的电气信号s

rx2

,输出信号d

out

维持为低。

103.由于没有产生输出信号d

out

的变化,次级侧发射器800不驱动绝缘隔层510的次级侧输入516,初级侧接收器900的输出即返回信号d

return

维持为低。

104.返回信号d

return

与输入信号d

in

的逻辑值为不一致。因此,初级侧发射器600在时刻t2,产生第一状态的电气信号s

tx1

。该电气信号s

tx1

正常地传输给次级侧后,在绝缘隔层510的次级侧输出514,产生第一状态的电气信号s

rx2

,次级侧接收器700输出高的输出信号d

out

。

105.次级侧发射器800在输出信号d

out

转变为高后,产生第一状态的电气信号s

tx2

。其结果,在绝缘隔层510的初级侧输出518,产生第一状态的电气信号s

rx1

。初级侧接收器900在检测到第一状态的电气信号s

rx1

后,输出高的返回信号d

return

。

106.其结果,返回信号d

return

与输入信号d

in

的逻辑值一致。这样,初级侧发射器600停止第一状态的电气信号s

tx1

的生成。

107.以上为传输电路500的动作。在该传输电路500中,通过追加从次级侧504向初级侧502返回信息的返回信道,从而初级侧发射器600可知信息是否正确地传达。而且,通过重复信号的传输直到正确地传递信息为止,从而能够可靠地向次级侧504传递信号。

108.该传输电路500在信号正确传输后,停止动作,因此存在电力消耗的增加较小,此外还可以抑制emi的优点。

109.本公开或本发明可以作为图1的框图或电路图进行理解,或者涉及从上述的说明中导出的各种装置、方法,但并不限定于特定的结构。下面,并不在于缩窄本发明的范围,而是为了辅助发明的本质或动作的理解,或者为了将其明确,说明更具体的结构例或实施例。

110.(实施例1)

111.图4是实施例1的传输电路500a的框图。绝缘隔层510包括前向信道用的变压器t1、返回信道用的变压器t2。变压器t1及t2分别具有初级绕组wp及次级绕组ws。变压器t1的初级绕组wp对应于初级侧输入512,变压器t1的次级绕组ws对应于次级侧输出514。变压器t2的次级绕组ws对应于次级侧输入516,变压器t2的初级绕组wp对应于初级侧输出518。

112.初级侧发射器600向变压器t1的初级绕组wp供给驱动信号i

tx1

。在变压器t1的次级绕组ws,产生与电流信号i

tx1

对应的电压信号v

rx2

。电流信号i

tx1

及电压信号v

rx2

对应于图1的

电气信号s

tx1

、r

rx2

。

113.变压器t1的次级绕组ws的产生电压v

rx2

以式(1)表示。

[0114]vrx2

=m

·

di

tx1

/dt

…

(1)

[0115]

m为互导,以m=k√(l

tx

l

rx

)表示,k为耦合系数。l

tx

、l

rx

为初级绕组wp及次级绕组ws的自感。

[0116]

图5是说明实施例1的信号传输的时序图。在本实施例中,初级侧发射器600将响应于输入信号d

in

的电平变化而极性(朝向)变化的电流信号i

tx1

供给至初级绕组wp。具体而言,输入信号d

in

从低转变到高时,电流信号i

tx1

为第一极性的脉冲电流ip,其对应于电气信号s

tx1

的第一状态相反地,输入信号d

in

从高转变到低时,电流信号i

tx1

为第二极性的脉冲电流in,其对应于电气信号s

tx1

的第二状态

[0117]

在变压器t1的次级绕组ws,产生具有与驱动电流i

tx1

的极性对应的极性的脉冲状的电压信号v

rx2

。次级侧接收器700检测电压信号v

rx2

的极性,根据检测到的极性,改变输出信号d

out

的逻辑值。在该示例中,根据正极性的电压信号v

rx2

,输出信号d

out

转变为高,根据负极性的电压信号v

rx2

,输出信号d

out

转变为低。

[0118]

返回图4。初级侧发射器600在产生输入信号d

in

为高、返回信号d

return

为低的不一致的期间,重复产生正极性的脉冲电流ip。此外,初级侧发射器600在产生输入信号d

in

为低、返回信号d

return

为高的不一致的期间,重复产生负极性的脉冲电流in。

[0119]

包括次级侧发射器800、初级侧接收器900及变压器t2的返回信道可以采用与前向信道相同的传输方式。具体而言,次级侧发射器800向变压器t2的次级绕组ws供给驱动电流i

tx2

。输出信号d

out

转变到高时,电流信号i

tx2

为第一极性的脉冲电流ip,其对应于电气信号s

tx2

的第一状态相反地,当输出信号d

out

转变为低时,电流信号i

tx2

为第二极性的脉冲电流,其对应于电气信号s

tx2

的第二状态

[0120]

在变压器t2的初级绕组wp中,产生与电流信号i

tx2

对应的电压信号v

rx1

。初级侧接收器900检测出电压信号v

rx1

的极性,根据检测到的极性,改变返回信号d

return

的逻辑值。例如,根据正极性的电压信号v

rx1

,输出信号d

return

转变为高,根据负极性的电压信号v

rx1

,返回信号d

return

转变为低。

[0121]

图6是示出初级侧发射器600a的结构例的电路图。初级侧发射器600a包括第一比较电路610、第一振荡电路620、第一输出部630。第一比较电路610比较输入信号d

in

和返回信号d

return

的逻辑值。在第一振荡电路620的使能端子中,输入第一比较电路610的比较结果,比较结果为不一致时成为使能状态(振荡),生成规定的频率的第一脉冲信号sp1。比较结果一致时,成为非使能状态(停止)。第一脉冲信号sp1的频率规定信号传输的重试的重复周期,并且第一脉冲信号sp1的脉冲宽度规定脉冲电流ip、in的脉冲宽度。

[0122]

第一输出部630根据输入信号d

in

和第一脉冲信号sp1,驱动绝缘隔层510的初级侧输入512。具体而言,输入信号d

in

为高,第一脉冲信号sp1为有效电平期间,输出第一极性的驱动电流i

tx1

(脉冲信号ip)。输入信号d

in

为低,第一脉冲信号sp1为有效电平期间,输出第二极性的驱动电流i

tx2

(脉冲电流in)。

[0123]

图7是示出初级侧发射器600a的具体的结构例的电路图。第一输出部630为h电桥电路,包括推挽型的输出级(逆变器)的对632、634。一个输出级632将输入信号d

in

反相,供给至初级绕组wp的一端。输入信号d

in

为高的期间,输出级632的输出vo1为低(gnd1),输入信号din

为低的期间,输出级632的输出vo1为高(vdd1)。

[0124]

输出级634将来自第一振荡电路620的控制脉冲d

delay

(图6的脉冲信号sp1)反相,供给至初级绕组wp的另一端。控制脉冲d

delay

为高的期间,输出级634的输出vo2为低(gnd1),控制脉冲d

delay

为低的期间,输出级634的输出vo2为高(vdd1)。

[0125]

第一比较电路610例如包括xor(排他性的异或值)门612,生成表示输入信号d

in

与返回信号d

return

的一致、不一致的信号,供给至第一振荡电路620的使能端子(负逻辑)enb。

[0126]

第一振荡电路620可以作为环形振荡器的一种来理解,在本说明书中,称为脉冲输出型(或间歇振荡型)环形振荡器621。脉冲输出型环形振荡器621在使能端子en输入高的期间振荡,生成控制脉冲d

delay

。脉冲输出型环形振荡器621中,包括规定控制脉冲d

delay

的频率(周期)的至少一个延迟要素d1、d2。

[0127]

and门622、xor门623、624被插入脉冲输出型环形振荡器621中。and门622在使能信号en为低的期间,截断脉冲输出型环形振荡器621,使其停止振荡。此外,通过该and门622与反相延迟要素d3的组合,规定控制脉冲ddelay的占空因数。

[0128]

xor门623根据输入信号d

in

与and门622的输出逻辑值,使控制脉冲d

delay

的极性反相。xor门624根据控制脉冲d

delay

与返回信号d

return

的逻辑值,使控制脉冲d

delay

的极性反相。

[0129]

图8是示出次级侧接收器700的结构例的电路图。次级侧接收器700包括锁存电路710、开关控制部720c、第一开关swp、第二开关swn。

[0130]

锁存电路710中,置位端子(s)与变压器t1的次级绕组ws的一端连接,复位端子(r)与变压器t1的次级绕组ws的另一端连接。

[0131]

锁存电路710只要是具有置位、复位的两输入的锁存电路即可,不限制逻辑极性、结构。在本实施例中,锁存电路710为nor型的sr锁存,包括斜交叉的两个nor门712、714。

[0132]

第一开关swp被设置于产生公共电压v

com

的公共电压节点com与置位端子(s)之间,锁存电路710的输出d

out

为高时成为接通。第二开关swn被设置于公共电压节点com与复位端子(r)之间,锁存电路710的输出为低时成为接通。在该示例中,公共电压v

com

为接地电压gnd2,第一开关swp及第二开关swn为nmos晶体管。此外,也可以将公共电压vcom作为电源电压vdd2,此时,也可以将第一开关swp及第二开关swn作为pmos晶体管。

[0133]

开关控制部720c根据锁存电路710的状态,即输出信号d

out

的逻辑值控制第一开关swp、第二开关swn。

[0134]

开关控制部720c等待到电流脉冲i

tx

的转变(后缘)结束,断开第一开关swp、第二开关swn。即,开关控制部720c在第一极性的脉冲电流i

tx

的转变结束后断开第二开关swn,在第二极性的脉冲电流i

tx

的转变结束后,断开第一开关swp。

[0135]

在此,开关控制部720c可以利用单纯的延迟,但在该实施例中采用基于非重叠电路的延迟,开关控制部720c在第一开关swp接通后,在经过规定时间后断开第二开关swn,第二开关swn接通后,在经过规定时间后断开第一开关swp。由此,通过设定第一开关swp、第二开关swn二者接通的期间,将置位端子、复位端子的电压v

rxs

、v

rxr

二者固定为于接地gnd2,从而进一步使信号稳定。

[0136]

开关控制部720c包括第一nand门726、第一延迟电路728、第二nand门730、第二延迟电路732。

[0137]

第一nand门726在第一输入节点接收锁存电路710的反相输出d

outb

,输出节点与第

一开关swp的栅极连接。第一延迟电路728延迟第一nand门726的输出v

rst1

。第二nand门730在第一输入节点接收锁存电路710的输出d

out

,在第二输入节点接收第一延迟电路728的输出,输出节点与第二开关swn的栅极连接。第二延迟电路732将第二nand门730的输出v

rst2

延迟,并供给至第一nand门726的第二输入节点。

[0138]

图9是示出传输电路500a的整体的结构例的电路图。初级侧发射器600、次级侧接收器700的结构与图7、图8相同。初级侧接收器900可以与次级侧接收器700同样地构成。

[0139]

次级侧发射器800包括预驱动器840及第二输出部830。第二输出部830为h电桥电路,包括推挽型的输出级(逆变器)的对832、834。一个输出级832将输出信号d

out

反相,并供给至变压器t2的次级绕组ws的一端。输出信号d

out

为高的期间,输出级832的输出vo1为低(gnd2),输出信号d

out

为低的期间,输出级832的输出vo1为高(vdd2)。

[0140]

输出级834将来自预驱动器840的控制脉冲d

odelay

反相,供给至变压器t2的次级绕组ws的另一端。控制脉冲d

odelay

为高的期间,输出级834的输出vo2为低(gnd12),控制脉冲d

odelay

为低的期间,输出级834的输出vo2为高(vdd2)。

[0141]

预驱动器840包含延迟输出信号d

out

而生成控制脉冲d

odelay

的延迟电路842。

[0142]

以上为传输电路500a的结构例。接着说明其动作。

[0143]

图10的(a)~(c)是示出图9的传输电路500a的动作的时序图。图10的(a)示出为正常时的动作。输入信号d

in

转变到高时,与返回信号d

return

不一致,因此第一振荡电路620为使能,其结果,生成第一极性的脉冲电流ip。

[0144]

脉冲电流ip被正确地传输给次级侧504时,输出信号d

out

变为高,返回信号d

return

也变为高,输入信号d

in

和返回信号d

return

的逻辑值一致。其结果,第一振荡电路620停止,脉冲电流ip也停止。

[0145]

输入信号d

in

转变至低时,与返回信号d

return

不一致,因此第一振荡电路620成为使能,其结果,生成第二极性的脉冲电流in。脉冲电流in被正确地传输给次级侧504时,输出信号d

out

成为低,返回信号d

return

也成为低,输入信号d

in

与返回信号d

return

的逻辑值一致。其结果,第一振荡电路620停止,脉冲电流in也停止。

[0146]

图10的(b)示出脉冲电流ip1从初级侧发射器600向次级侧接收器700的传输失败时的动作。

[0147]

输入信号d

in

转变至高时,与返回信号d

return

不一致,因此第一振荡电路620成为使能,其结果,生成第一极性的脉冲电流ip1。

[0148]

脉冲电流ip1的传输失败时,输出信号d

out

维持为低,因此输入信号d

in

和表示输出信号d

out

的返回信号d

return

失配持续。其结果,第一振荡电路620持续振荡,因而初级侧发射器600生成第二次脉冲电流ip2。脉冲电流ip2的发送成功时,输出信号d

out

转变至高,输入信号d

in

与表示输出信号d

out

的返回信号d

return

一致。其结果,第一振荡电路620成为非使能状态,停止动作,其以后不会生成脉冲电流ip。

[0149]

图10的(c)示出尽管输入信号din没有变化,但由于噪声等的影响,次级侧接收器700的输入变化时的动作。

[0150]

变压器t1的次级绕组ws的一端v

rxr2

产生噪声nx时,输出信号d

out

转变至低,返回信号d

return

成为低。其结果,输入信号d

in

和返回信号d

return

变得不一致,第一振荡电路620进入使能状态。此时,输入信号d

in

为高,从而生成第一极性的脉冲电流ipx。该脉冲电流ipx被传

输到次级侧504时,输出信号d

out

转变为高,返回信号d

return

也为高。其结果,输入信号din与返回信号d

return

一致,第一振荡电路620成为非使能状态。

[0151]

以上为传输电路500a的动作。根据该传输电路500,在初级侧502和次级侧504产生不一致的情况下,可以通过较少个数的追加的发送脉冲ip、in而取得匹配。

[0152]

此外,由于能够仅以没有流动恒定电流的逻辑电路构成,因而没有信号转变时的消耗电流成为零。因此,可以仅通过与数据传输速度成比例地消耗电流而工作,可以大幅削减消耗电力。

[0153]

(实施例2)

[0154]

图11的(a)、(b)是实施例2的传输电路500b的电路图。在传输电路500b中,次级侧接收器700还具备尖峰脉冲除去电路740。如图11的(b)所示,尖峰脉冲除去电路740包括迟滞触发器742和延迟电路744。

[0155]

延迟电路744将输入信号(即次级侧接收器700的输出)迟延。迟滞触发器742在第一输入节点接收输入信号,在第二输入节点接收延迟电路744的输出。迟滞触发器742还可以被称为穆勒c元件(muller c-element),在两个输入in1、in2的逻辑不一致时保持前一次的输出值,两个输入in1、in2二者为低时,输出低,两个输入in1、in2二者为高时,输出高。

[0156]

根据实施例2,可以除去在图10的(c)这样的状况下在输出信号d

out

产生的、具有比延迟电路744的延迟更短的脉冲宽度的脉冲。

[0157]

(实施例3)

[0158]

在实施例1中,在返回信道产生异常的情况下,可能会产生无用的电力消耗,或无法消除失配的情况。

[0159]

图12的(a)、(b)是说明在图9的传输电路500a发生的问题的时序图。图12的(a)示出不能正确地发送返回信号d

return

的情况。此时,虽然输出信号d

out

与输入信号d

in

的逻辑值一致,但返回信号d

return

与输入信号d

in

不一致,因而初级侧发射器600重复生成脉冲电流ip,会消耗无用的电力。

[0160]

图12的(b)示出由于噪声ny而返回信号d

return

转变至错误的电平的情况。此时,初级侧发射器600重复产生第一极性的脉冲电流ip,消耗无用的电力。

[0161]

此外,图12的(a)或(b)的不匹配在输入信号d

in

转变前没有被消除。

[0162]

在实施例3中,说明能够解决该问题的结构。图13是示出实施例3的传输电路500c的初级侧502c的结构的电路图。

[0163]

在实施例3中,初级侧发射器600c在输入信号d

in

与返回信号d

return

的逻辑值一致后,追加地进行一次绝缘隔层的初级侧输入512的驱动。即,输入信号d

in

为高时,生成追加的脉冲电流ip,输入信号d

in

为低时,生成追加的脉冲电流in。

[0164]

初级侧发射器600c包括第一振荡电路620c以及振荡器控制器640。第一振荡电路620c为带使能的脉冲输出型环形振荡器621,除图7的第一振荡电路620之外,还包括电平敏感型锁存器(d锁存器)626。电平敏感型锁存器626在输入节点d接收返回信号d

return

,在门(反相逻辑)被输入使能信号enb,使能信号enb为低的期间,使返回信号d

return

通过。

[0165]

振荡器控制器640除第一比较电路610之外,还包括d触发器642及or门644。第一比较电路610判断输入信号d

in

和返回信号d

return

的一致、不一致。

[0166]

d触发器642保持前一次的第一比较电路610的输出。or门644输出第一比较电路

610的输出与d触发器642的输出的逻辑和。在两个循环内都连续地输入信号d

in

与返回信号d

return

一致时,or门644的输出即使能信号(负逻辑)enb成为有效(低)。

[0167]

根据该结构,在输入信号d

in

和返回信号d

return

的逻辑值一致后,通过追加进行一次绝缘隔层的初级侧输入512的驱动,可以持续生成控制脉冲d

idelay

,直到输入信号d

in

与返回信号d

return

的逻辑值的一致连续产生两次。

[0168]

图14是示出实施例3的传输电路500c的次级侧504c的结构的电路图。

[0169]

尖峰脉冲除去电路740c除迟滞触发器742、延迟电路744之外,还包括or门746、d触发器748。在变压器t1的次级绕组ws,产生电压信号时,or门746的输出成为高,d触发器748中取入延迟电路744的输出的值。d触发器748中,保持前一次的输出信号d

out

。

[0170]

传输电路500c的次级侧发射器800c在当前的输出信号d

out0

与前一次的输出信号d

out1

不一致的期间,重复绝缘隔层的次级侧、即变压器t2的次级绕组ws的驱动。

[0171]

次级侧发射器800c可以与图7的初级侧发射器600同样地构成,包括第二比较电路810、第二振荡电路820、第二输出部830。第二比较电路810将前一次的输出信号d

out1

与当前的输出信号d

out0

的逻辑值进行比较,生成表示比较结果的使能信号enb。第二振荡电路820是带使能的脉冲输出型环形振荡器。

[0172]

以上为实施例3的传输电路500c的结构。图15是示出实施例3的传输电路500c的动作的时序图。

[0173]

根据实施例3,次级侧发射器800在返回信号d

return

被正确传输后,停止工作,对于返回信道的异常也可以具有耐性。

[0174]

实施方式仅为例示,本领域技术人员应当理解,对这些各构成要素或各处理工艺的组合能够进行多种变形例,并且这样得到的变形例也处于本发明或本公开的范围内。下面,针对这样的变形例进行说明。

[0175]

次级侧接收器700的结构并不限定于图8的情况。此外,下面的变形例也能够针对初级侧接收器900适用。

[0176]

(变形例1)

[0177]

图16是变形例1的次级侧接收器700的电路图。开关控制部720可以由两个逆变器722、724构成。第一逆变器722的输入节点与锁存电路710的反相输出qb连接,输出节点与第一开关swp的栅极连接。第二逆变器724的输入节点与锁存电路710的输出q连接,输出节点与第二开关swn的栅极连接。

[0178]

(变形例2)

[0179]

图17是变形例2的次级侧接收器700的电路图。在上面的说明中,将公共电压v

com

设为接地电压gnd2,但并不限定于此。在该变形例2中,公共电压v

com

设为电源电压vdd2。此外,第一开关swp、第二开关swn由pmos晶体管构成。

[0180]

此外,在变形例2中,锁存电路710包括斜交叉连接的第一nand门716及第二nand门718。该锁存电路710为负逻辑,在置位端子sb的电压v

rx1

从高转变至低时被置位,在复位端子rb的电压v

rx2

从高转变至低时被复位。

[0181]

开关控制部720包括第三逆变器734及第四逆变器736。第三逆变器734在输入节点接收锁存电路710的输出d

out

,输出节点与第一开关swp的栅极连接。第四逆变器736在输入节点接收锁存电路710的反相输出d

outb

,输出节点与第二开关swn的栅极连接。

[0182]

此外,也可以将开关控制部720设为图8的开关控制部720c。

[0183]

(变形例3)

[0184]

次级侧接收器700及初级侧接收器900的结构也并不限定于上述的情况,可以使用公知技术构成。

[0185]

(变形例4)

[0186]

第一振荡电路及第二振荡电路的结构并不限定于上述的情况,可以替换构成要素的顺序,或更换正/负逻辑极性。

[0187]

(变形例5)

[0188]

在实施例1~3中,说明了绝缘隔层510包括两个变压器的情况,但并不限定于此,可以包含电容器。此时,根据作为电容器方式而已知的公知技术,改变初级侧发射器600、次级侧接收器700、次级侧发射器800、初级侧接收器900的结构即可。或者,也可以是,绝缘隔层510包含一个变压器,通过一个变压器双向地收发信号。

[0189]

(用途)

[0190]

最后,说明传输电路500的用途。

[0191]

图18是具备传输电路500的绝缘转换器1000的电路图。控制器1100被配置于次级侧,以输出电压v

out

接近目标值的方式生成脉冲信号。传输电路500将控制器1100生成的脉冲信号sp作为输入信号d

in

接收,传输给绝缘转换器1000的初级侧。栅极驱动器1200通过与传输电路500的输出信号d

out

对应的栅极信号,驱动初级侧的开关晶体管m1。

[0192]

图19是具备传输电路500的半桥式转换器2000的电路图。半桥式转换器2000包括高侧晶体管mh、低侧晶体管ml。栅极驱动器2002根据pwm信号,驱动低侧晶体管ml。

[0193]

高侧晶体管mh是n信道。高侧晶体管mh的驱动电路2004以高侧晶体管mh和开关晶体管ml的连接节点即开关节点的电压v

sw

为基准(接地gnd2)进行动作。此外,驱动电路2004的电源电压(vdd2)由自举电路所生成。

[0194]

传输电路500将pwm信号从以接地电压gnd1为基准的区域,传输给以接地电压gnd2(=vsw)为基准的区域。

[0195]

根据实施方式,使用具体的语句说明了本发明,但实施方式仅示出本发明的原理、应用,对于实施方式,在不脱离权利要求书所规定的本发明的思想的范围内,允许多种变形例或配置的变更。

[0196]

工业上的可利用性

[0197]

本公开可以利用在电子电路中。

[0198]

附图标记说明

[0199]

500 传输电路

[0200]

510 绝缘隔层

[0201]

512 初级侧输入

[0202]

514 次级侧输出

[0203]

516 次级侧输入

[0204]

518 初级侧输出

[0205]

t1 变压器

[0206]

t2 变压器

[0207]

600 初级侧发射器

[0208]

610 第一比较电路

[0209]

612 xor门

[0210]

620 第一振荡电路

[0211]

621 脉冲输出型环形振荡器

[0212]

622 and门

[0213]

623、624 xor门

[0214]

630 第一输出部

[0215]

632、634 输出级

[0216]

700 次级侧接收器

[0217]

swp 第一开关

[0218]

swn 第二开关

[0219]

710 锁存电路

[0220]

720 开关控制部

[0221]

740 尖峰脉冲除去电路

[0222]

742 迟滞触发器

[0223]

744 延迟电路

[0224]

800 次级侧发射器

[0225]

810 第二比较电路

[0226]

820 第二振荡电路

[0227]

830 第二输出部

[0228]

840 预驱动器

[0229]

900 初级侧接收器

[0230]

wp 初级绕组

[0231]

ws 次级绕组

[0232]

com 公共电压节点

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1