增强Δ-∑转换器噪声性能的系统和方法与流程

本发明涉及转换器,更具体地,涉及δ-∑转换器。

背景技术:

1、ab类驱动器、调制器、转换器和放大器等设备可用于扬声器和耳机驱动器等音频设备。这些应用中的大多数是电池驱动的,因此功耗是一个重要参数。这些设备还需要在信噪比(snr)和总谐波失真(thd)方面满足高性能。通常,这些应用程序具有不同的操作模式,使得一种模式可以优化性能,并且另一种模式则可以优化功耗。

技术实现思路

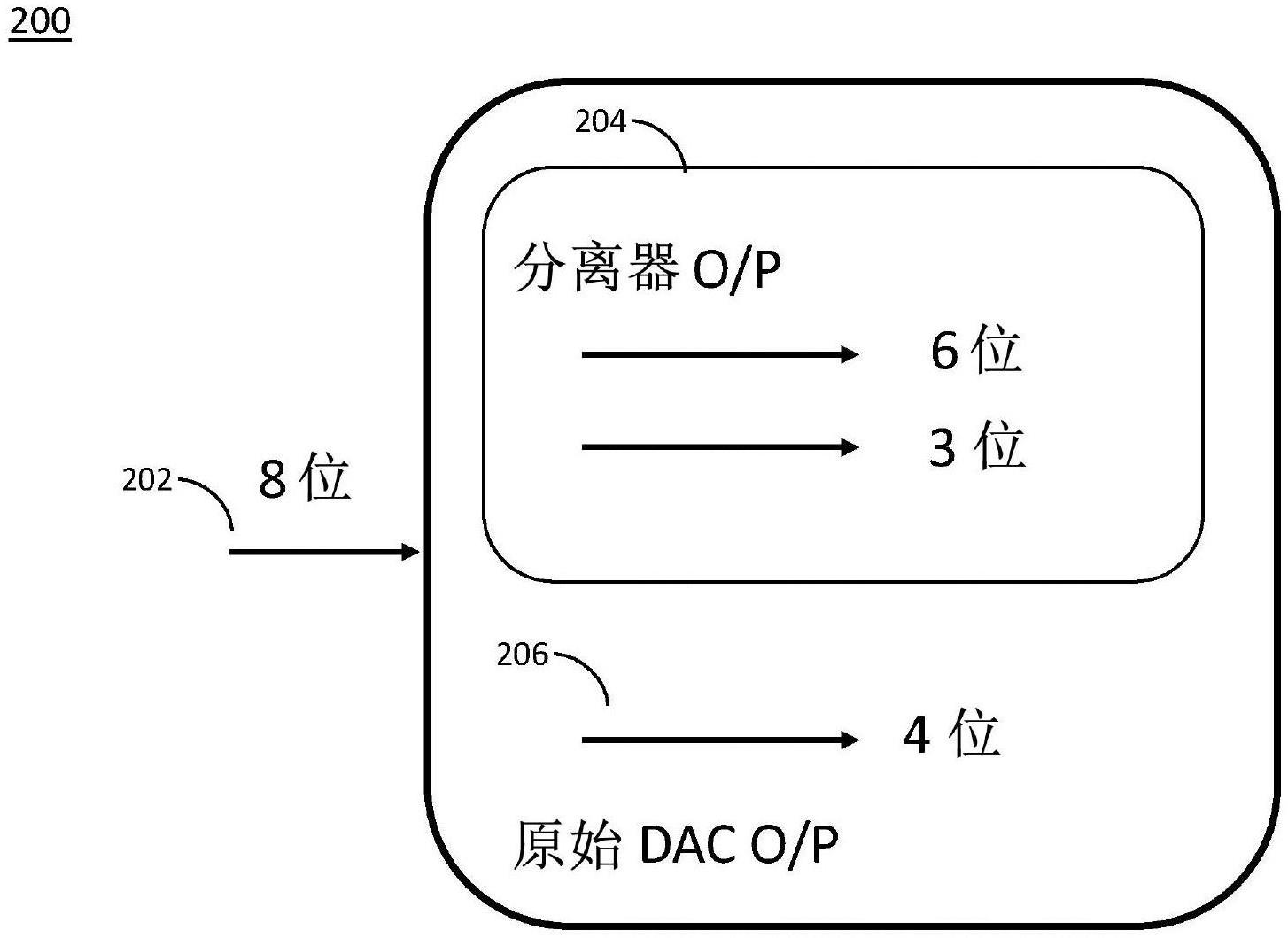

1、本发明提供了用于改进δ-∑调制器中的噪声效率的系统和方法。公开了一种用于噪声分离器的旁路方案,其减少了小信号的切换活动。特别地,旁路方案允许小信号的最低有效位来旁路噪声分离模块,从而提高系统的效率。

2、根据一个方面,一种逐样本旁路噪声分离器包括:噪声分离模块,被配置为将输入信号分离成多个分离信号,其中所述多个分离信号中的每一个都小于所述输入信号;以及旁路线路,被配置为将输入信号直接传递到输出线路;其中高于所选阈值的信号被引导到所述噪声分离模块,并且其中低于所选阈值的信号被引导到所述旁路线路。

3、根据各种实现,旁路线路被配置为将输入信号的一组最低有效位传递到输出线路。在一些示例中,多个分离信号包括包括输入信号的最低有效位的第一信号和包括输入信号的最高有效位的第二信号。在一些实施方式中,旁路噪声分离器还包括被配置为分离输入信号的∑-δ环。在一些实施方式中,噪声分离模块包括被配置为截断输入信号的加法器。在一些实施方式中,噪声分离模块包括被配置为对加法器输出执行一阶∑-δ调制的削波器。在一些实施方式中,噪声分离模块包括寄存器,该寄存器被配置为向削波器输出添加延迟,并且进一步被配置为将误差反馈回下一个周期。

4、根据一些实施方式,旁路噪声分离器还包括噪声分离模块中的第一多路复用器和旁路线路中的第二多路复用器,其中第一多路复用器输出输入信号的经处理的最高有效位,而第二多路复用器输出该输入信号的最低有效位。在一些实施方式中,当信号低于所选阈值时,噪声分离模块被禁用。在一些实施方式中,旁路噪声包括延迟模块,其中低于所选阈值的信号被引导到延迟模块,并且其中延迟模块被配置为在所选时间段内延迟禁用噪声分离模块。

5、根据另一个方面,一种具有增强的噪声性能的转换器包括:内插器,被配置为接收输入信号;噪声分离器,包括噪声分离模块和旁路线路,被配置为接收内插信号并输出多个并行输出信号;耦合到所述噪声分离器的多个旋转扰频器,被配置为对所述多个并行输出信号中的每一个应用离散元件建模并输出相应的多个dem输出信号;以及多个3电平数模转换器(dac),耦合到旋转扰频器,被配置为将所述多个dem输出信号中的每一个转换为相应的模拟信号;其中所述噪声分离器是逐样本旁路分离器,并且其中高于所选阈值的信号被引导到所述噪声分离模块,并且其中低于所选阈值的信号被引导到所述旁路线路。

6、在一些实施方式中,信号低于所选阈值,噪声分离器被配置为禁用噪声分离模块。在一些实施方式中,噪声分离器包括延迟模块,其中低于所选阈值的信号被引导到延迟模块,并且其中延迟模块被配置为在所选时间段内延迟禁用噪声分离模块。

7、附图显示了示例性数字d类驱动器电路和配置。这些电路的变化,例如,改变电路的位置、从电路中添加或移除某些元件,并不超出本发明的范围。所示的回放电路、配置和补充设备旨在补充详细描述中的支持。

8、该概述旨在提供本专利申请的主题的概述。其不旨在提供对本发明的排他性或详尽的解释。通过将这些系统与本申请的其余部分中参照附图所阐述的本发明的一些方面进行比较,常规和传统方法的进一步限制和缺点对于本领域技术人员来说将变得显而易见。

技术特征:

1.一种逐样本旁路噪声分离器,包括:

2.根据权利要求1所述的旁路噪声分离器,其中所述旁路线路被配置为将所述输入信号的一组最低有效位传递到所述输出线路。

3.根据权利要求1所述的旁路噪声分离器,其中所述多个分离信号包括包括所述输入信号的最低有效位的第一信号和包括所述输入信号的最高有效位的第二信号。

4.根据权利要求1所述的旁路噪声分离器,其中所述噪声分离模块包括被配置为分离所述输入信号的∑-δ环。

5.根据权利要求4所述的旁路噪声分离器,其中:

6.根据权利要求1所述的旁路噪声分离器,其中所述噪声分离模块包括加法器,所述加法器被配置为将第二信号与所述输入信号相加。

7.根据权利要求6所述的旁路噪声分离器,其中所述加法器是第一加法器,并且其中所述噪声分离模块包括第二加法器和量化器,所述量化器被配置为截断第二加法器输出以提供第一输出。

8.根据权利要求7所述的旁路噪声分离器,其中所述噪声分离模块包括寄存器,所述寄存器被配置为对量化器输出进行滤波,并且还被配置为反馈回滤波的量化器输出并将滤波的量化器输出与第一加法器输出相加。

9.根据权利要求8所述的旁路噪声分离器,其中所述寄存器被配置为在随后的周期上利用第二加法器将所述滤波的量化器输出与所述第一加法器输出相加。

10.根据权利要求1所述的旁路噪声分离器,其中所述旁路线路还包括第三加法器,所述第三加法器被配置为处理所述输入信号和第一输出以生成第二输出。

11.根据权利要求1所述的旁路噪声分离器,其中:

12.根据权利要求11所述的旁路噪声分离器,其中当信号低于所述选定阈值时,所述噪声分离模块被禁用,并且所述第一多路复用器被配置为输出零,而所述第二多路复用器配置为输出所述输入信号的最低有效位。

13.根据权利要求1所述的旁路噪声分离器,其中当信号低于所选阈值时,所述噪声分离器模块被禁用。

14.根据权利要求13所述的旁路噪声分离器,还包括延迟模块,其中低于所述选定阈值的信号被引导到所述延迟模块,并且其中所述延迟模块被配置为在选定的时间段内延迟禁用所述噪声分离模块。

15.根据权利要求1所述的旁路模块,其中所述多个分离信号中的第一分离信号包括第一数量的最低有效位,其中所述旁路线路被配置为通过所述输入信号的第二数量的最低有效位,并且其中所述第一数量的最低有效位不同于所述第二数量的最低有效位。

16.一种具有增强的噪声性能的转换器,包括:

17.根据权利要求16所述的转换器,其中当信号低于所选阈值时,所述噪声分离器被配置为禁用所述噪声分离模块。

18.根据权利要求17所述的转换器,其中所述噪声分离器包括延迟模块,其中低于所述选定阈值的信号被引导到所述延迟模块,并且其中所述延迟模块被配置为将禁用所述噪声分离模块推迟选定时间段。

19.一种用于逐样本旁路噪声分离器的方法,包括:

20.根据权利要求19所述的方法,其中将所述输入信号直接传递到输出线路包括将所述输出信号的一组最低有效位传递到输出线路。

技术总结

用于改进Δ∑调制器中的噪声效率的系统和方法。公开了一种用于噪声分离器的旁路方案,其减少了小信号的切换活动。具体地,公开了一种逐样本旁路噪声分离器,包括噪声分离模块和旁路线路。当信号低于所选阈值时,旁路线路旁路噪声分离模块,从而提高系统的效率。

技术研发人员:A·班德约帕得哈,P·伯德桑,A·R·斯拜尔

受保护的技术使用者:美国亚德诺半导体公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!