包括选择电路的发射器电路以及操作选择电路的方法与流程

包括选择电路的发射器电路以及操作选择电路的方法

1.相关申请的交叉引用

2.本技术基于并且要求在韩国知识产权局于2021年5月27日提交的韩国专利申请no.10-2021-0068611和于2021年9月9日提交的韩国专利申请no.10-2021-0120542的优先权,上述申请中的每一个的公开以引用方式全文并入本文中。

技术领域

3.本发明构思的技术思想涉及一种包括选择电路的发射器电路,并且更具体地说,涉及用于执行低功率操作的选择电路以及该选择电路的操作方法。

背景技术:

4.发射器电路可包括通过按次序输出多个并行数据信号生成串行数据信号的串行化器。串行化器可以基于具有不同相位的多个时钟信号按次序输出多个并行数据信号。随着所述多个时钟信号切换,发射器电路中包括的多个晶体管可高速地开关,而随着开关的晶体管的数量增加,发射器电路消耗的功率会增大。

技术实现要素:

5.本发明构思的技术思想涉及一种发射器电路,并且提供一种仅用部分切换的数据选择信号执行低功率串行化操作的选择电路、一种操作该选择电路的方法,以及一种包括选择电路的发射器电路。

6.根据示例实施例,一种发射器电路可包括:时钟生成器,其被配置为基于参考时钟信号生成彼此具有不同相位的多个时钟信号;以及多个选择电路,其连接至输出节点。多个选择电路被配置为:接收多个并行数据信号,以及基于多个时钟信号和接收的多个并行数据信号在输出节点输出串行数据信号。多个选择电路中的每一个包括:数据多路复用器,其被配置为基于多个并行数据信号中的接收到的一个并行数据信号与多个时钟信号之间的逻辑运算生成多个数据选择信号;控制信号生成器,其被配置为基于多个数据选择信号之间的逻辑运算生成第一控制信号和第二控制信号;以及输出驱动器,其连接至输出节点,并且被配置为:基于第一控制信号为输出节点预充电,或者基于第二控制信号将输出节点放电。

7.根据示例实施例,一种选择电路可包括:数据多路复用器,其被配置为基于接收的数据信号与多个时钟信号之间的逻辑运算生成多个数据选择信号;控制信号生成器,其被配置为基于多个数据选择信号之间的逻辑运算生成第一控制信号和第二控制信号;以及输出驱动器,其连接至输出节点,并且被配置为通过基于第一控制信号为输出节点预充电或者基于第二控制信号将输出节点放电来驱动输出节点。在接收的数据信号的逻辑电平保持在特定逻辑电平的同时,多个数据选择信号中的一些的逻辑电平转变,并且其它数据选择信号的逻辑电平保持恒定。

8.根据示例实施例,一种操作选择电路的方法可包括:基于接收的数据信号与多个

时钟信号之间的逻辑运算生成多个数据选择信号;基于多个数据选择信号之间的逻辑运算生成第一控制信号和第二控制信号;以及通过基于第一控制信号对输出节点预充电或者基于第二控制信号将输出节点放电来驱动输出节点。在接收的并行数据信号的逻辑电平保持在特定逻辑电平的同时,生成多个数据选择信号的步骤包括:转变多个数据选择信号中的一些的逻辑电平;以及保持其它数据选择信号的逻辑电平恒定。

附图说明

9.将从下面结合附图的详细描述中更清楚地理解本发明构思的实施例,其中:

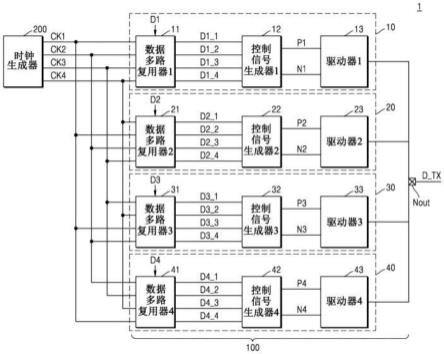

10.图1是用于解释根据本发明构思的示例实施例的发射器电路的图;

11.图2是用于解释根据本发明构思的示例实施例的串行化操作的图;

12.图3a和图3b是用于解释根据本发明构思的示例实施例的时钟生成器的图;

13.图4是用于解释根据本发明构思的示例实施例的多路复用器的结构的图;

14.图5a至图5c是根据本发明构思的示例实施例的图4的多路复用器的时序图;

15.图6是示出根据本发明构思的示例实施例的操作选择电路的方法的流程图;

16.图7是用于解释根据本发明构思的示例实施例的多路复用器的结构的图;

17.图8a至图8c是根据本发明构思的示例实施例的图7的多路复用器的时序图;

18.图9是用于解释根据本发明构思的示例实施例的多路复用器的结构的图;以及

19.图10是用于解释根据本发明构思的实施例的包括多路复用器的半导体存储器装置的示图。

具体实施方式

20.下文中,参照附图描述本发明构思的各实施例。

21.图1是用于描述根据本发明构思的示例实施例的发射器电路的图。图2是用于解释根据本发明构思的示例实施例的串行化操作的图。

22.参照图1,发射器电路1可以并行地接收第一并行数据信号d1至第四并行数据信号d4,并且输出串行数据信号d_tx。第一并行数据信号d1至第四并行数据信号d4中的每一个可通过不同的信道被发送至多路复用器100,并且串行数据信号d_tx可通过一个信道向外输出。虽然示出了接收到四个并行数据信号,但是实施例不限于此,并且可接收n(n是大于或等于2的整数)个并行数据信号。例如,发射器电路1可以从半导体存储器装置(例如,图10的1300)的存储器单元阵列接收第一并行数据信号d1至第四并行数据信号d4。

23.发射器电路1可包括多路复用器100和时钟生成器200。

24.多路复用器100可以响应于第一时钟信号ck1至第四时钟信号ck4按次序输出第一并行数据信号d1至第四并行数据信号d4。详细地说,参照图2,多路复用器100可以响应于第一时钟信号ck1的有效边缘(例如,上升边缘)输出第一并行数据信号d1,可以响应于第二时钟信号ck2的有效边缘输出第二并行数据信号d2,可以响应于第三时钟信号ck3的有效边缘输出第三并行数据信号d3,并且可以响应于第四时钟信号ck4的有效边缘输出第四并行数据信号d4。例如,多路复用器100可以执行用于将第一并行数据信号d1至第四并行数据信号d4转换为一个串行数据信号d_tx的串行化操作。然而,实施例不限于此,并且多路复用器100可将n个并行数据信号转换为一个串行数据信号d_tx。

25.多路复用器100可包括第一选择电路10、第二选择电路20、第三选择电路30和第四选择电路40。第一选择电路10、第二选择电路20、第三选择电路30和第四选择电路40中的每一个可以接收第一时钟信号ck1至第四时钟信号ck4,并且输出对应的并行数据信号。例如,第一选择电路10可以响应于第一时钟信号ck1的有效边缘输出第一并行数据信号d1。第二选择电路20可以响应于第二时钟信号ck2的有效边缘输出第二并行数据信号d2。第三选择电路30可以响应于第三时钟信号ck3的有效边缘输出第三并行数据信号d3。第四选择电路40可以响应于第四时钟信号ck4的有效边缘输出第四并行数据信号d4。

26.为了便于解释,示出了四个时钟信号,但实施例不限于此,多路复用器100可通过基于n个时钟信号对n个并行数据信号执行串行化操作来生成串行数据信号d_tx。

27.详细地说,第一选择电路10可包括第一数据多路复用器11、第一控制信号生成器12和第一输出驱动器13。

28.第一数据多路复用器11可基于第一并行数据信号d1和第一时钟信号ck1至第四时钟信号ck4之间的逻辑运算生成第一数据选择信号d1_1至第四数据选择信号d1_4。在第一并行数据信号d1保持在特定逻辑电平(例如,逻辑低电平或逻辑高电平)的同时,第一数据选择信号d1_1至第四数据选择信号d1_4中的一些的逻辑电平可保持,并且其它数据选择信号的逻辑电平可通过第一并行数据信号d1和第一时钟信号ck1至第四时钟信号ck4之间的逻辑运算而转变。例如,因为第一数据选择信号d1_1至第四数据选择信号d1_4中的仅一些在串行化操作中切换,所以第一选择电路10消耗的功率可降低。

29.第一控制信号生成器12可基于第一数据选择信号d1_1至第四数据选择信号d1_4之间的逻辑运算生成第一控制信号p1和第二控制信号n1。当第一并行数据信号d1具有逻辑高电平时,第一控制信号生成器12可以基于第一数据选择信号d1_1至第四数据选择信号d1_4执行逻辑运算,使得第一控制信号p1具有逻辑低电平。当第一并行数据信号d1具有逻辑低电平时,第一控制信号生成器12可以基于第一数据选择信号d1_1至第四数据选择信号d1_4执行逻辑运算,使得第二控制信号n1具有逻辑高电平。

30.第一输出驱动器13可以基于第一控制信号p1和第二控制信号n1驱动输出节点nout。例如,当第一控制信号p1处于逻辑低电平时,第一输出驱动器13可为输出节点nout预充电,并且当第二控制信号n1具有逻辑高电平时,输出节点nout可放电。

31.第二选择电路20可包括第二数据多路复用器21、第二控制信号生成器22和第二输出驱动器23。第二数据多路复用器21可生成第一数据选择信号d2_1至第四数据选择信号d2_4。第二控制信号生成器22可生成第一控制信号p2和第二控制信号n2。第三选择电路30可包括第三数据多路复用器31、第三控制信号生成器32和第三输出驱动器33。第三数据多路复用器31可生成第一数据选择信号d3_1至第四数据选择信号d3_4。第三控制信号生成器32可生成第一控制信号p3和第二控制信号n3。第四选择电路40可包括第四数据多路复用器41、第四控制信号生成器42和第四输出驱动器43。第四数据多路复用器41可生成第一数据选择信号d4_1至第四数据选择信号d4_4。第四控制信号生成器42可生成第一控制信号p4和第二控制信号n4。对第一选择电路10的描述也可应用于第二选择电路20、第三选择电路30和第四选择电路40。

32.为了便于解释,示出了四个选择电路,但实施例不限于此。例如,多路复用器100可包括n个选择电路,并且n个选择电路中的每一个可以基于n个时钟信号输出并行数据信号。

详细地说,n个选择电路中的每一个可包括数据多路复用器、控制信号生成电路和输出驱动器。数据多路复用器可以基于n个时钟信号生成n个数据选择信号。在并行数据信号的逻辑电平保持在特定逻辑电平(例如,逻辑低电平或逻辑高电平)的同时,数据多路复用器可以恒定地保持n个数据选择信号中的至少一个数据选择信号的逻辑电平。例如,在并行数据信号的逻辑电平保持在特定逻辑电平(例如,逻辑低电平或逻辑高电平)的同时,n个数据选择信号中的至少一个数据选择信号的逻辑电平可不切换。控制信号生成器可以基于n个数据信号生成用于控制输出驱动器的控制信号。例如,构成控制信号生成器的晶体管中的接收不切换的数据选择信号的晶体管可不操作。因此,选择电路消耗的功率可降低。可在下面参照图5a、图5b、图5c、图8a、图8b和图8c详细地描述数据选择信号的逻辑电平。

33.时钟生成器200可生成第一时钟信号ck1至第四时钟信号ck4。第一时钟信号ck1至第四时钟信号ck4的占空比可为50%。占空比可表示在一个周期中施加有效信号的时间段的比率。第一时钟信号ck1至第四时钟信号ck4可具有不同相位。例如,参照图2,第一时钟信号ck1的相位为0

°

,第二时钟信号ck2的相位为90

°

,第三时钟信号ck3的相位为180

°

,并且第四时钟信号ck4的相位为270

°

。然而,实施例不限于此,并且时钟生成器200可生成具有互相恒定的相位差的n个时钟信号。

34.根据根据本发明构思的示例实施例的发射器电路1,当执行串行化操作时,第一数据选择信号d1_1至第四数据选择信号d1_4中的一些不切换而是保持逻辑电平,从而第一数据选择信号d1_1至第四数据选择信号d1_4消耗的功率可降低。因此,发射器电路1可以以低功率执行串行化操作。

35.图3a和图3b是用于解释根据本发明构思的示例实施例的时钟生成器的图。

36.参照图3a,时钟生成器200a可包括锁相环(pll)51和多相位时钟生成器52a。时钟生成器200a可为图1的时钟生成器200的示例。

37.pll 51可生成参考时钟信号ref_ck并且可以将参考时钟信号ref_ck发送至多相位时钟生成器52a。pll 51可包括振荡器。参考时钟信号ref_ck的占空比可为50%。

38.多相位时钟生成器52a可基于参考时钟信号ref_ck生成彼此具有不同相位的第一时钟信号ck1至第四时钟信号ck4。例如,第一时钟信号ck1的相位可为0

°

,第二时钟信号ck2的相位可为90

°

,第三时钟信号ck3的相位可为180

°

,并且第四时钟信号ck4的相位可为270

°

。多相位时钟生成器52a可包括延迟锁相环(dll)。

39.参照图3b,时钟生成器200b可以从存储器控制器2接收参考时钟信号ref_ck,并且可基于参考时钟信号ref_ck生成第一时钟信号ck1至第四时钟信号ck4。时钟生成器200b可为图1的时钟生成器200的示例。

40.在一些实施例中,时钟生成器200b可被包括在半导体存储器装置(例如,图10的1300)中,并且存储器控制器2可将参考时钟信号ref_ck发送至半导体存储器装置1300。在一些实施例中,参考时钟信号ref_ck可被称作写时钟信号wck。半导体存储器装置1300可通过基于写时钟信号wck执行串行化操作来生成串行数据信号,并且可以将生成的串行数据信号发送至存储器控制器2。

41.图4是用于解释根据本发明构思的示例实施例的多路复用器的结构的图。图5a至图5c是根据本发明构思的示例实施例的图4的多路复用器的时序图。

42.参照图4,多路复用器100a可包括第一选择电路至第四选择电路10a、20a、30a和

40a。多路复用器100a中包括的选择电路的数量不限于此。在图4的描述中,对第一选择电路10a的描述也可应用于第二选择电路至第四选择电路20a、30a和40a。

43.第一选择电路10a可包括第一数据多路复用器11a、第一控制信号生成器12a和第一输出驱动器13。

44.第一数据多路复用器11a可包括第一nand电路111、第二nand电路112、第一nor电路113和第二nor电路114。

45.在第一选择电路10a中,第一nand电路111和第二nand电路112以及第一nor电路113和第二nor电路114可以接收第一并行数据信号d1。另外,在第一选择电路10a中,第一nand电路111可通过对第一时钟信号ck1和第一并行数据信号d1执行nand运算来生成第一数据选择信号d1_1。第二nand电路112可通过对第四时钟信号ck4和第一并行数据信号d1执行nand运算来生成第二数据选择信号d1_2。第一nor电路113可通过对第三时钟信号ck3和第一并行数据信号d1执行nor运算来生成第三数据选择信号d1_3。第二nor电路114可通过对第二时钟信号ck2和第一并行数据信号d1执行nor运算来生成第四数据选择信号d1_4。

46.在示例实施例中,在第二选择电路20a中,第一nand电路211和第二nand电路212以及第一nor电路213和第二nor电路214可以接收第二并行数据信号d2。另外,在第二选择电路20a中,第一nand电路211可以接收第二时钟信号ck2,第二nand电路212可以接收第一时钟信号ck1,第一nor电路213可以接收第四时钟信号ck4,第二nor电路214可以接收第三时钟信号ck3。在第三选择电路30a中,第一nand电路311和第二nand电路312以及第一nor电路313和第二nor电路314可以接收第三并行数据信号d3。另外,在第三选择电路30a中,第一nand电路311可以接收第三时钟信号ck3,第二nand电路312可以接收第二时钟信号ck2,第一nor电路313可以接收第一时钟信号ck1,第二nor电路314可以接收第四时钟信号ck4。在第四选择电路40a中,第一nand电路411和第二nand电路412以及第一nor电路413和第二nor电路414可以接收第四并行数据信号d4。另外,在第四选择电路40a中,第一nand电路411可以接收第四时钟信号ck4,第二nand电路412可以接收第三时钟信号ck3,第一nor电路413可以接收第二时钟信号ck2,第二nor电路414可以接收第一时钟信号ck1。

47.参照图4和图5a,当第一时钟信号ck1具有逻辑低电平时,第一数据选择信号d1_1可经第一nand电路111具有逻辑高电平。当第一时钟信号ck1具有逻辑高电平时,第一数据选择信号d1_1可经第一nand电路111具有第一并行数据信号d1的反相值d1n。当第四时钟信号ck4具有逻辑低电平时,第二数据选择信号d1_2可经第二nand电路112具有逻辑高电平。当第四时钟信号ck4具有逻辑高电平时,第二数据选择信号d1_2可经第二nand电路112具有第一并行数据信号d1的反相值d1n。当第三时钟信号ck3具有逻辑高电平时,第三数据选择信号d1_3可经第一nor电路113具有逻辑低电平。当第三时钟信号ck3具有逻辑低电平时,第三数据选择信号d1_3可经第一nor电路113具有第一并行数据信号d1的反相值d1n。当第二时钟信号ck2具有逻辑高电平时,第四数据选择信号d1_4可经第二nor电路114具有逻辑低电平。当第二时钟信号ck2具有逻辑低电平时,第四数据选择信号d1_4可经第二nor电路114具有第一并行数据信号d1的反相值d1n。

48.第一控制信号生成器12a可基于对第一数据选择信号d1_1至第四数据选择信号d1_4的逻辑运算生成第一控制信号p1和第二控制信号n1。

49.第一控制信号生成器12a可包括第三nor电路121、第一反相器122、第三nand电路

123和第二反相器124。

50.第三nor电路121可对第一数据选择信号d1_1和第二数据选择信号d1_2执行nor运算。第一反相器122可通过将第三nor电路121的输出反相而生成第一控制信号p1。参照图5a,第一控制信号p1可以基本上保持逻辑高电平,并且可响应于第一时钟信号ck1的有效边缘具有第一并行数据信号d1的反相值d1n。

51.第三nand电路123可对第三数据选择信号d1_3和第四数据选择信号d1_4执行nand运算。第二反相器124可通过将第三nand电路123的输出反相生成第二控制信号n1。参照图5a,第二控制信号n1可以基本上保持逻辑低电平,并且可响应于第一时钟信号ck1的有效边缘具有第一并行数据信号d1的反相值d1n。

52.第一输出驱动器13可包括第一晶体管m1和第二晶体管m2。第一晶体管m1可为p型晶体管,第二晶体管m2可为n型晶体管。可将第一控制信号p1输入至第一晶体管m1的栅极端子,可将电源电压节点连接至其源极端子,并且可将输出节点nout连接至其漏极端子。可将第二控制信号n1输入至第二晶体管m2的栅极端子,可将地节点连接至其源极端子,并且可将输出节点nout连接至其漏极端子。当第一晶体管m1导通时,可对输出节点nout预充电,当第二晶体管m2导通时,输出节点nout可放电。

53.参照图5a,第一控制信号p1的默认逻辑电平为逻辑高电平,当第一并行数据信号d1具有逻辑高电平时,第一控制信号p1可响应于第一时钟信号ck1具有逻辑低电平。例如,第一输出驱动器13可通过在第一并行数据信号d1具有逻辑高电平时对输出节点nout预充电而包括串行数据信号d_tx中的第一并行数据信号d1。另外,第二控制信号n1的默认逻辑电平是逻辑低电平,当第一并行数据信号d1具有逻辑低电平时,第二控制信号n1可响应于第一时钟信号ck1具有逻辑高电平。例如,第一输出驱动器13可通过在第一并行数据信号d1具有逻辑低电平时对输出节点nout放电而包括串行数据信号d_tx中的第一并行数据信号d1。

54.图5b是用于解释当第一并行数据信号d1具有逻辑高电平时第一数据选择信号d1_1至第四数据选择信号d1_4以及第一控制信号p1和第二控制信号n1的逻辑电平的图。

55.参照图5b,在第一并行数据信号d1的逻辑电平保持在逻辑高电平的同时,第一数据选择信号d1_1和第二数据选择信号d1_2的逻辑电平可转变。另一方面,第三数据选择信号d1_3和第四数据选择信号d1_4的逻辑电平可保持在逻辑低电平。例如,因为第三数据选择信号d1_3和第四数据选择信号d1_4不切换,所以第三数据信号d1_3和第四数据信号d1_4消耗的功率可减少。

56.图5c是用于解释当第一并行数据信号d1具有逻辑低电平时第一数据选择信号d1_1至第四数据选择信号d1_4以及第一控制信号p1和第二控制信号n1的逻辑电平的示图。

57.参照图5c,在第一并行数据信号d1的逻辑电平保持在逻辑低电平的同时,第三数据选择信号d1_3和第四数据选择信号d1_4的逻辑电平可转变。另一方面,第一数据选择信号d1_1和第二数据选择信号d1_2的逻辑电平可保持在逻辑高电平。例如,因为第一数据选择信号d1_1和第二数据选择信号d1_2不切换,所以由第一数据信号d1_1和第二数据信号d1_2消耗的功率可减少。因此,由第一选择电路10a消耗的功率可减少。

58.图6是示出根据本发明构思的示例实施例的操作选择电路的方法的流程图。操作选择电路的方法可包括多个操作步骤。可参照图4描述图6。

59.在步骤s610中,第一数据多路复用器11a可基于并行数据信号(例如,第一并行数据信号d1)与多个时钟信号(例如,第一时钟信号ck1至第四时钟信号ck4)之间的逻辑运算生成多个数据选择信号(例如,第一数据选择信号d1_1至第四数据选择信号d1_4)。可执行并行数据信号与所述多个时钟信号之间的多个逻辑运算,使得在并行数据信号的逻辑电平恒定地保持在特定逻辑电平(例如,逻辑低电平或逻辑高电平)的同时,所述多个数据选择信号中的一些的逻辑电平保持恒定,并且其它数据选择信号的逻辑电平转变。

60.在步骤s620中,第一控制信号生成器12a可基于所述多个数据选择信号之间的逻辑运算生成第一控制信号p1和第二控制信号n1。当并行数据信号具有逻辑高电平时,第一控制信号生成器12a可以执行所述多个数据选择信号之间的逻辑运算,使得第一控制信号p1具有逻辑低电平。当数据信号具有逻辑低电平时,第一控制信号生成器12a可以对所述多个数据选择信号执行逻辑运算,使得第二控制信号n1具有逻辑高电平。

61.在步骤s630中,第一输出驱动器13可以基于第一控制信号p1和第二控制信号n1驱动输出节点nout。详细地说,第一输出驱动器13可以基于具有逻辑低电平的第一控制信号p1对输出节点nout预充电,并且可基于具有逻辑高电平的第二控制信号n1对输出节点nout放电。

62.根据根据本发明构思的示例实施例的操作选择电路的方法,因为在并行数据信号的逻辑电平保持的同时所述多个数据选择信号中的一些不切换,所以选择电路的功耗可降低。

63.图7是用于解释根据本发明构思的示例实施例的多路复用器的结构的图。图8a至图8c是根据本发明构思的示例实施例的图7的多路复用器的时序图。

64.参照图7,多路复用器100b可包括第一选择电路至第四选择电路10b、20b、30b和40b。然而,多路复用器100b中包括的选择电路的数量不限于此。在图7的描述中,第一选择电路10b的描述也可应用于第二选择电路至第四选择电路20b、30b和40b。

65.第一选择电路10b可包括第一数据多路复用器11b、第一控制信号生成器12b和第一输出驱动器13。与图4的第一数据多路复用器11a不同,第一数据多路复用器11b可包括反相器101。与图4的第一控制信号生成器12a不同,第一控制信号生成器12b可不包括第一反相器122和第二反相器124。

66.第一数据多路复用器11b可包括反相器101、第一nand电路111、第二nand电路112、第一nor电路113和第二nor电路114。

67.反相器101可以接收第一并行数据信号d1并且生成第一并行数据信号d1的第一反相数据信号(或第一反相值)d1n。

68.在第一选择电路10b中,第一nand电路111可通过对第一时钟信号ck1和第一反相数据信号d1n执行nand运算来生成第一数据选择信号d1_1。第二nand电路112可通过对第四时钟信号ck4和第一反相数据信号d1n执行nand运算来生成第二数据选择信号d1_2。第一nor电路113可通过对第三时钟信号ck3和第一反相数据信号d1n执行nor运算来生成第三数据选择信号d1_3。第二nor电路114可通过对第二时钟信号ck2和第一反相数据信号d1n执行nor运算来生成第四数据选择信号d1_4。

69.在示例实施例中,在第二选择电路20b中,反相器201可以接收第二并行数据信号d2并且生成第二并行数据信号d2的第二反相数据信号d2n,第一nand电路211和第二nand电

路212以及第一nor电路213和第二nor电路214可以接收第二反相并行数据信号d2n。另外,在第二选择电路20b中,第一nand电路211可以接收第二时钟信号ck2,第二nand电路212可以接收第一时钟信号ck1,第一nor电路213可以接收第四时钟信号ck4,第二nor电路214可以接收第三时钟信号ck3。在第三选择电路30b中,反相器301可以接收第三并行数据信号d3并且生成第三并行数据信号d3的第三反相数据信号d3n,第一nand电路311和第二nand电路312以及第一nor电路313和第二nor电路314可以接收第三反相并行数据信号d3n。另外,在第三选择电路30b中,第一nand电路311可以接收第三时钟信号ck3,第二nand电路312可以接收第二时钟信号ck2,第一nor电路313可以接收第一时钟信号ck1,第二nor电路314可以接收第四时钟信号ck4。在第四选择电路40b中,反相器401可以接收第四并行数据信号d4并且生成第四并行数据信号d4的第四反相数据信号d4n,第一nand电路411和第二nand电路412以及第一nor电路113和第二nor电路414可以接收第四反相并行数据信号d4n。另外,在第四选择电路40b中,第一nand电路411可以接收第四时钟信号ck4,第二nand电路412可以接收第三时钟信号ck3,第一nor电路413可以接收第二时钟信号ck2,第二nor电路414可以接收第一时钟信号ck1。

70.参照图7和图8a,当第一时钟信号ck1具有逻辑低电平时,第一数据选择信号d1_1可经第一nand电路111具有逻辑高电平。当第一时钟信号ck1具有逻辑高电平时,第一数据选择信号d1_1可经第一nand电路111具有第一并行数据信号d1的值。当第四时钟信号ck4具有逻辑低电平时,第二数据选择信号d1_2可经第二nand电路112具有逻辑高电平。当第四时钟信号ck4具有逻辑高电平时,第二数据选择信号d1_2可经第二nand电路112具有第一并行数据信号d1的值。当第三时钟信号ck3具有逻辑高电平时,第三数据选择信号d1_3可经第一nor电路113具有逻辑低电平。当第三时钟信号ck3具有逻辑低电平时,第三数据选择信号d1_3可经第一nor电路113具有第一并行数据信号d1的值。当第二时钟信号ck2具有逻辑高电平时,第四数据选择信号d1_4可经第二nor电路114具有逻辑低电平。当第二时钟信号ck2具有逻辑低电平时,第四数据选择信号d1_4可经第二nor电路114具有第一并行数据信号d1的值。

71.第一控制信号生成器12b可基于对第一数据选择信号d1_1至第四数据选择信号d1_4的逻辑运算生成第一控制信号p1和第二控制信号n1。

72.第一控制信号生成器12b可包括第三nor电路121和第三nand电路123。

73.第三nor电路121可通过对第一数据选择信号d1_1和第二数据选择信号d1_2执行nor运算来生成第二控制信号n1。参照图8a,第二控制信号n1可以基本上保持逻辑低电平,并且可响应于第一时钟信号ck1的有效边缘具有第一并行数据信号d1的反相值d1n。

74.第三nand电路123可通过对第三数据选择信号d1_3和第四数据选择信号d1_4执行nand运算来生成第一控制信号p1。参照图8a,第一控制信号p1可以基本上保持逻辑高电平,并且可响应于第一时钟信号ck1的有效边缘具有第一并行数据信号d1的反相值d1n。

75.参照图8a,第一控制信号p1的默认逻辑电平可为逻辑高电平,当第一并行数据信号d1具有逻辑高电平时,第一控制信号p1可响应于第一时钟信号ck1具有逻辑低电平。例如,第一输出驱动器13可通过在第一并行数据信号d1具有逻辑高电平时对输出节点nout预充电而包括串行数据信号d_tx中的第一并行数据信号d1。另外,第二控制信号n1的默认逻辑电平可为逻辑低电平,当第一并行数据信号d1具有逻辑低电平时,第二控制信号n1可响

应于第一时钟信号ck1具有逻辑高电平。例如,第一输出驱动器13可通过在第一并行数据信号d1具有逻辑低电平时将输出节点nout放电而包括串行数据信号d_tx中的第一并行数据信号d1。

76.图8b是用于解释当第一并行数据信号d1具有逻辑高电平时第一数据选择信号d1_1至第四数据选择信号d1_4以及第一控制信号p1和第二控制信号n1的逻辑电平的图。

77.参照图8b,在第一并行数据信号d1的逻辑电平保持在逻辑高电平的同时,第一数据选择信号d1_1和第二数据选择信号d1_2的逻辑电平可保持在逻辑高电平。另一方面,第三数据选择信号d1_3和第四数据选择信号d1_4的逻辑电平可转变。例如,因为第一数据选择信号d1_1和第二数据选择信号d1_2不切换,第一数据选择信号d1_1和第二数据选择信号d1_2消耗的功率可减少。

78.图8c是用于解释当第一并行数据信号d1具有逻辑低电平时第一数据选择信号d1_1至第四数据选择信号d1_4以及第一控制信号p1和第二控制信号n1的逻辑电平的示图。

79.参照图8c,在第一并行数据信号d1的逻辑电平保持在逻辑低电平的同时,第三数据选择信号d1_3和第四数据选择信号d1_4的逻辑电平可保持在逻辑低电平。另一方面,第一数据选择信号d1_1和第二数据选择信号d1_2的逻辑电平可转变。例如,因为第三数据选择信号d1_3和第四数据选择信号d1_4不切换,所以第三数据选择信号d1_3和第四数据选择信号d1_4消耗的功率可减少。

80.图9是用于解释根据本发明构思的示例实施例的多路复用器的结构的图。

81.参照图9,多路复用器100c可包括第一选择电路至第四选择电路10c、20c、30c和40c。然而,多路复用器100c中包括的选择电路的数量不限于此。在图9的描述中,对第一选择电路10c的描述也可应用于第二选择电路至第四选择电路20c、30c和40c。

82.第一选择电路10c可包括第一数据多路复用器11a、第一控制信号生成器12c和第一输出驱动器13。与图4的第一控制信号生成器12a和图7的第一控制信号生成器12b不同,第一控制信号生成器12c可包括第四nand电路125和第四nor电路126。同时,第三nor电路121可将对第一数据选择信号d1_1和第二数据选择信号d1_2进行nor运算的结果发送至第四nand电路125。另外,第三nand电路123可将对第三数据选择信号d1_3和第四数据选择信号d1_4进行nand运算的结果发送至第四nor电路126。

83.为了输出具有逻辑低电平的第一并行数据信号d1作为串行数据信号d_tx,需通过第二晶体管m2将输出节点nout放电,从而当第一晶体管m1导通时输出节点nout的信号电平可能变得不稳定。当根据本发明构思的示例实施例的多路复用器100c中包括的第四nand电路125接收具有逻辑低电平的第一并行数据信号d1时,第四nand电路125可生成具有逻辑高电平的第一控制信号p1。因此,因为第一晶体管m1截止,所以输出节点nout被预充电的可能性可减小,并且输出节点nout的信号稳定性可提高。

84.为了输出具有逻辑高电平的第一并行数据信号d1作为串行数据信号d_tx,需通过第一晶体管m1将输出节点nout预充电,从而当第二晶体管m2导通时输出节点nout的信号电平可能变得不稳定。当根据本发明构思的示例实施例的多路复用器100c中包括的第四nor电路126接收具有逻辑高电平的第一并行数据信号d1时,第四nor电路126可生成具有逻辑低电平的第二控制信号n1。因此,因为第二晶体管m2截止,所以输出节点nout被放电的可能性可减小,并且输出节点nout的信号稳定性可提高。

85.图10是用于解释包括根据本发明构思的实施例的多路复用器的半导体存储器装置的示图。

86.参照图10,半导体存储器装置1300可包括控制逻辑1310、刷新地址生成器1315、地址缓冲器1320、分块控制逻辑1330、行地址多路复用器1340、列地址锁存器1350、行解码器、存储器单元阵列、读出放大器单元、列解码器、输入/输出门控电路1390、数据输入/输出(i/o)缓冲器1395和纠错码(ecc)引擎1400。

87.存储器单元阵列可包括第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d。行解码器可包括分别连接至第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d的第一分块行解码器至第四分块行解码器1360a、1360b、1360c和1360d。列解码器可包括分别连接至第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d的第一分块列解码器至第四分块列解码器1370a、1370b、1370c和1370d。读出放大器单元可包括分别连接至第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d的第一分块读出放大器至第四分块读出放大器1385a、1385b、1385c和1385d。第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d、第一分块行解码器至第四分块行解码器1360a、1360b、1360c和1360d、第一分块列解码器至第四分块列解码器1370a、1370b、1370c和1370d以及第一分块读出放大器至第四分块读出放大器1385a、1385b、1385c和1385d可以分别构成第一分块至第四分块。图10示出了包括四个分块的半导体存储器装置1300的示例,但是根据实施例,半导体存储器装置1300可包括任意数量的分块。

88.另外,根据实施例,半导体存储器装置1300可为动态随机存取存储器(dram),诸如双数据速率同步动态随机存取存储器(ddr sdram)、低功率双数据速率(lpddr)sdram、图形双数据速率(gddr)sdram、rambus动态随机存取存储器(rdram),或者可为需要刷新操作的任何易失性存储器装置。

89.控制逻辑1310可以控制半导体存储器装置1300的操作。例如,控制逻辑1310可生成控制信号ctl,以使得半导体存储器装置1300执行写操作或读操作。控制逻辑1310可包括用于解码从存储器控制器接收的命令cmd的命令解码器(未示出),以及用于设置半导体存储器装置1300的操作模式的模式寄存器(未示出)。例如,命令解码器可以通过解码写使能信号/we、行地址选通信号/ras、列地址选通信号(/cas)、芯片选择信号(/cs)等生成对应于命令cmd的控制信号。

90.控制逻辑1310还可接收用于以同步的方式驱动半导体存储器装置1300的时钟信号clk和时钟使能信号cke。控制逻辑1310可以响应于刷新命令控制刷新地址生成器1315执行自动刷新操作,或者可以响应于自刷新进入命令控制刷新地址生成器1315执行自刷新操作。

91.刷新地址生成器1315可生成对应于将对其执行刷新操作的存储器单元行的刷新地址ref_addr。刷新地址生成器1315可按比在半导体存储器装置1300的标准中定义的刷新周期更长的刷新率生成刷新地址ref_addr。因此,半导体存储器装置1300的刷新电流和刷新功率可减小。

92.地址缓冲器1320可以从存储器控制器接收包括分块地址bank_addr、行地址row_addr和列地址col_addr的地址addr。另外,地址缓冲器1320可将接收的分块地址bank_addr提供至分块控制逻辑1330,将接收的行地址row_addr提供至行地址多路复用器1340,并且

将接收的列地址col_addr提供至列地址锁存器1350。

93.分块控制逻辑1330可响应于分块地址bank_addr生成分块控制信号。响应于分块控制信号,第一分块行解码器至第四分块行解码器1360a、1360b、1360c和1360d中的对应于分块地址bank_addr的分块行解码器可被激活,并且第一分块列解码器至第四分块列解码器1370a、1370b、1370c和1370d中的对应于分块地址bank_addr的分块列解码器可被激活。

94.分块控制逻辑1330可响应于确定分块组的分块地址bank_addr生成分块组控制信号。响应于分块组控制信号,第一分块行解码器至第四分块行解码器1360a、1360b、1360c和1360d中的对应于分块地址bank_addr的分块组的行解码器可被激活,并且第一分块列解码器至第四分块列解码器1370a、1370b、1370c和1370d中的对应于分块地址bank_addr的分块组的列解码器可被激活。

95.行地址多路复用器1340可以从地址缓冲器1320接收行地址row_addr并且从刷新地址生成器1315接收刷新行地址ref_addr。行地址多路复用器1340可以响应于从控制逻辑1310生成的第一控制信号ctl1选择性地输出行地址row_addr或者刷新行地址ref_addr。从行地址多路复用器1340输出的行地址可施加至第一分块行解码器至第四分块行解码器1360a、1360b、1360c和1360d。

96.第一分块行解码器至第四分块行解码器1360a、1360b、1360c和1360d中的通过分块控制逻辑1330激活的分块行解码器可对从行地址多路复用器1340输出的行地址解码,以激活对应于行地址的字线。例如,激活的分块行解码器可将字线驱动电压施加至对应于行地址的字线。

97.列地址锁存器1350可以从地址缓冲器1320接收列地址col_addr,并且暂时存储接收的列地址col_addr。列地址锁存器1350可按照突发模式逐渐增大接收的列地址col_addr。列地址锁存器1350可将暂时存储的或逐渐增大的列地址col_addr分别施加至第一分块列解码器至第四分块列解码器1370a、1370b、1370c和1370d。

98.第一分块列解码器至第四分块列解码器1370a、1370b、1370c和1370d中的由分块控制逻辑1330激活的分块列解码器可通过输入/输出门控电路1390激活对应于分块地址bank_addr和列地址col_addr的读出放大器。

99.输入/输出门控电路1390可包括输入数据掩模逻辑、用于存储从第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d输出的数据的读数据锁存器以及用于将数据写至第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d的写驱动器,以及用于门控输入/输出数据的电路。

100.将从第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d之一读取的数据可通过读出放大器感测放大,并且被存储在读数据锁存器中。可通过数据输入/输出缓冲器1395将存储在读数据锁存器中的数据dq提供至存储器控制器。可将将写在第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d之一中的数据dq从存储器控制器提供至数据输入/输出缓冲器1395。提供至数据输入/输出缓冲器1395的数据dq可通过写驱动器写入一个分块阵列中。

101.输入/输出门控电路1390可包括多路复用器1391。多路复用器1391可为上面分别参照图1、图4、图7和图9描述的多路复用器100、100a、100b和100c之一。多路复用器1391可以利用上面参照图1、图2、图3a、图3b、图4、图5a至图5c、图6、图7、图8a至图8c和图9描述的

方法将从第一分块阵列至第四分块阵列1380a、1380b、1380c和1380d并行读取的数据转换为串行数据信号。可响应于从控制逻辑1310生成的第二控制信号ctl2控制ecc引擎1400。

102.虽然已经参照本发明构思的实施例具体示出并描述了本发明构思,但是应该理解,可在不脱离所附权利要求的精神和范围的情况下,在其中作出各种形式和细节上的改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1