一种细步进频率实现方法与流程

1.本发明属于雷达与通信射频系统技术领域,具体地说,是涉及一种细步进频率实现方法。

背景技术:

2.频率合成是雷达射频系统的核心技术,其技术指标直接决定了雷达、电子对抗、通信、仪器仪表等电子系统的整机性能指标。

3.频率合成技术主要考核的技术指标为频率范围、杂散、相位噪声、频率步进等,其实现方法也多种多样,主要可分为直接合成和间接合成两大类。间接合成即锁相式频率合成器具有很高的工作频率,很宽的工作频带及较好的频谱纯度,但锁定时间较长,另外间接频率合成源的频谱分辨率较低。而直接频率合成具有极高的频率分辨率和极短的频率转换时问,但工作频带受限,目前dds(直接数字频率合成器)的直接输出频率在1ghz以下,如果需工作在更高的频段,要采取倍频等方式,使用大量的滤波器,增加了系统的体积及复杂程度。

4.根据现有的技术指标,越来越多的雷达、电子对抗系统对频率合成技术的指标要求更加全面,包括要求频率范围、杂散、相位噪声、频率步进指标的兼顾,而频率实现技术的各个指标往往是相互冲突而不可兼得的。在频率步进很细时,如果杂散指标要求很高,用传统的锁相环(pll)是很难实现的,国内外多个科研单位及院校做过大量的尝试,主要的方法是将直接数字频率合成器(dds)与锁相环(pll)进行各种结合,取长补短。

5.2013年,杨光等人将dds作为pll的参考进行的尝试,通过dds的小步进实现pll的细步进,但是在引入dds后,相比于单pll,尺寸会成2.5倍的增加,无法实现小型化。

6.2019年,韦炜等人将dds与pll进行多次的环外混频并频谱搬移,最终实现宽带细步进的要求,但是多次的混频搬移需要多级开关滤波,在尺寸受限的情况下并不适用。

技术实现要素:

7.本发明的目的在于提供一种细步进频率实现方法,主要解决单锁相环方式在杂散问题上的技术缺陷,将杂散性能进行提升,弥补混合集成方式在功耗、相位噪声指标上的技术缺陷。

8.为实现上述目的,本发明采用的技术方案如下:

9.一种细步进频率实现方法,包括如下步骤:

10.(s1)提供低相位噪声的s波段基准信号作为混频本振信号和低频段多频点的l波段基准信号作为混频中频信号;

11.(s2)将混频本振信号和混频中频信号进行混频实现频率变换得到空间小、损耗小的可变信号;

12.(s3)将可变信号进行分频,并利用锁相源得到系统的主频基准信号;

13.(s4)对主频基准信号进行频率扩展,并对扩展后的信号进行滤波;

14.(s5)对滤波后的宽带信号的输出功率进行补偿及校准,得到平坦度高的细步进频率信号。

15.进一步地,在本发明中,在步骤(s1)中,所述s波段基准信号通过参考电路和基准锁相源相连产生,基准锁相源产生的频率为f1,其中对应的参考分频比为r1,倍频比为m1,即:此处r1、m1均为整数,f

ref

为参考电路产生的信号频率。

16.进一步地,在本发明中,在步骤(s1)中,所述l波段基准信号通过参考电路和可变参考源产生,可变参考源产生的频率为f2,其中对应的参考分频比为r2,倍频比为m2,输出分频比为m3,即:此处r2、m2、m3均为整数,f

ref

为参考电路产生的信号频率。

17.进一步地,在本发明中,所述可变信号通过与基准锁相源和可变参考源相连的频率变换电路获得,其产生的频率f3=f1+f2。

18.进一步地,在本发明中,所述可变信号的分频通过与频率变换电路相连的分频电路实现,其内部共经过两次分频,分别定义为r3和r4,即:其中n1和r3均为整数。

19.进一步地,在本发明中,所述主频基准信号通过与分频电路相连的主锁相源得到,其输出频率定义为f5,倍频比定义为:n1,即f5=f4*n1;其中n1可根据实际输出频率的频率步进及频点选择整数或者小数。

20.进一步地,在本发明中,对所述主频基准信号进行频率扩展通过与主锁相源相连的频率扩展电路实现;其最终输出频率定义f0;

21.当输出频率在高频段时:

22.f0=f5*n2;

23.进一步地:

[0024][0025]

更进一步地:

[0026][0027]

最终地:

[0028]

其中,n2为倍频比,n3分频比:

[0029]

当输出频率在低频段时:

[0030][0031]

进一步地:

[0032][0033]

更进一步地:

[0034][0035]

进一步地,在本发明中,对所述扩展后的信号进行滤波通过与频率扩展电路相连的开关滤波电路实现。

[0036]

进一步地,在本发明中,对所述滤波后的宽带信号的输出功率进行补偿及校准通过与开关滤波电路相连的功率调整电路实现。

[0037]

与现有技术相比,本发明具有以下有益效果:

[0038]

(1)本发明通过多个基准源之间合理的频率变换与选择,巧妙的避开了细步进频率合成方法中遇到的杂散点问题,并且补偿了多个电路的引入带来的相位噪声恶化问题,是对传统细步进频率合成方法的改进,有效提升了单锁相环细步进频率合成方法的杂散和频率步进,可将杂散指标提升至70dbc以下。

[0039]

(2)本发明弥补了单一直接数字频率合成器(dds)激励锁相环(pll)在功耗、杂散空间指标上的技术缺陷,并将分频、倍频的方法引入到频率实现系统中,将分频对于杂散、相位噪声、频率步进的优点进行有效整合,相比原实现方法,技术指标做到最优。

[0040]

(3)本发明是对现有的频率产生方式的进一步提升,使得原有的设计方式在功耗指标上提升50%,具有小型化、细步进、杂散小、输出频带宽等优点,在工作频段内稳定性能好、工作温度范围广,具有广泛应用前景。

[0041]

(4)本发明极大地减小了电路尺寸,具有体积小、性能稳定、指标一致性高等特点,相比原有的设计方法,在尺寸上可提升80%,同时具有良好的输入输出匹配,适合批量化生产,生产成本大大减小,适用于雷达、电子对抗、卫星通信等各类微波系统中。

[0042]

(5)本发明可极大的降低电磁兼容性能的设计难度,采用该方法后使得原有设计变得简单易行,并屏蔽掉可能产生的多种数字串扰信号,从设计方法本身解决数字串扰问题。

附图说明

[0043]

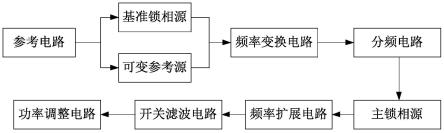

图1为本发明的结构示意图。

[0044]

图2为本发明-实施例中基准锁相源的电路原理框图。

[0045]

图3为本发明-实施例中可变参考源的电路原理框图。

[0046]

图4为本发明-实施例中频率变换电路和分频电路的电路原理框图。

[0047]

图5为本发明-实施例中主锁相源的电路原理框图。

[0048]

图6为本发明-实施例中频率扩展电路的电路原理框图。

[0049]

图7为本发明-实施例中开关滤波电路的电路原理框图。

[0050]

图8为本发明-实施例中功率调整电路的电路原理框图。

具体实施方式

[0051]

下面结合附图说明和实施例对本发明作进一步说明,本发明的方式包括但不仅限于以下实施例。

[0052]

实施例

[0053]

本发明公开的一种细步进频率实现方法,首先提供低相位噪声的s波段基准信号作为混频本振信号和低频段多频点的l波段基准信号作为混频中频信号;将混频本振信号和混频中频信号进行混频实现频率变换得到空间小、损耗小的可变信号;将可变信号进行分频,并利用锁相源得到系统的主频基准信号;对主频基准信号进行频率扩展,并对扩展后的信号进行滤波;对滤波后的宽带信号的输出功率进行补偿及校准,得到平坦度高的细步进频率信号。

[0054]

首先参考电路产生频率定义为:f

ref

。

[0055]

基准锁相源产生的频率为f1,其中对应的参考分频比为r1,倍频比为m1,即:此处r1、m1均为整数。

[0056]

可变参考源产生的频率为f2,其中对应的参考分频比为r2,倍频比为m2,输出分频比为m3,即:此处r2、m2、m3均为整数。

[0057]

频率变换电路实现频率变换,其产生的频率为:f3,即f3=f1+f2。

[0058]

分频电路实现对频率变换电路产生信号的进一步分频,其内部共经过两次分频,分别定义为r3和r4,即:其中n1和r3均为整数。

[0059]

主锁相源实现信号的最终锁定输出,其输出频率定义为f5,倍频比定义为:n1,即f5=f4*n1;其中n1可根据实际输出频率的频率步进及频点选择整数或者小数。

[0060]

频率扩展电路根据频率扩展要求,分别定义为倍频比:n2,分频比:n3。最终输出频率定义为:f0。

[0061]

具体地:

[0062]

将输出频率f0进行分段处理,分为高频段和低频段两段;

[0063]

当输出频率在高频段时:

[0064]

f0=f5*n2。

[0065]

进一步地:

[0066][0067]

更进一步地:

[0068][0069]

最终地:

[0070][0071]

当输出频率在低频段时:

[0072][0073]

进一步地:

[0074]

更进一步地:

[0075][0076]

为更详细的进行说明,对实际频点进行详细说明:

[0077]

当输出频率为高频段时,选取32000mhz进行详细说明:

[0078]

取f

ref

=100(mhz),r1=2,m1=60,

[0079]

则:

[0080]

取f

ref

=100(mhz),r2=10,m2=200,m3=10,

[0081]

则:f3=f1+f2=3200,

[0082]

取r3=32,r4=2,

[0083]

则:

[0084]

取n1=320,

[0085]

则:f5=f4*n1=16000,

[0086]

取n2=2,

[0087]

则:f0=f5*n2=32000,

[0088]

当需要实现小数频点,可对n1、n2、r1、r2、r3、r4、m1、m2进行灵活取值后实现最优的相位噪声及杂散指标。

[0089]

例如,当输出频率偏离1mhz时,即输出频率为32001mhz是,可对相应的值进行修改

后即可实现:

[0090]

取f

ref

=100(mhz),r1=1,m1=39,

[0091]

则:

[0092]

取f

ref

=100(mhz),r2=10,m2=801,m3=80,

[0093]

则:f3=f1+f2=4000.125,

[0094]

取r3=20,r4=2,

[0095]

则:

[0096]

取n1=160,

[0097]

则:f5=f4*n1=16000.5,

[0098]

取n2=2,

[0099]

则:f0=f5*n2=32001,

[0100]

其余频点可在此基础上进行以此类推,尤其是产生更细的频率步进时,可在部分频点对n1设置成小数值,使得小数频点远离最近的整数频点,得到最优秀的杂散指标。

[0101]

当输出频率为低频段时,选取1000mhz进行详细说明:

[0102]

取f

ref

=100(mhz),r1=1,m1=30,

[0103]

则:

[0104]

取f

ref

=100(mhz),r2=1,m2=20,m3=10,

[0105]

则:f3=f1+f2=3200,

[0106]

取r3=50,r4=2,

[0107]

则:

[0108]

取n1=100,

[0109]

则:f5=f4*100=10000,

[0110]

取n3=10,

[0111]

则:

[0112]

当需要实现小数频点,可对n1、n2、r1、r2、r3、r4、m1、m2进行灵活取值后实现最优的相

位噪声及杂散指标。

[0113]

例如,当输出频率偏离1mhz时,即输出频率为1001mhz时,可对相应的值进行修改后即可实现:

[0114]

取f

ref

=100(mhz),r1=1,m1=19,

[0115]

则:

[0116]

取f

ref

=100(mhz),r2=5,m2=102,m3=20,

[0117]

则:

[0118]

f3=f1+f2=2002,

[0119]

取r3=5,r4=2,

[0120]

则:

[0121]

取n1=100,

[0122]

则:f5=f4*n1=20020,

[0123]

取n3=20,

[0124]

则:

[0125]

其余频点可在此基础上进行以此类推,其中在低频段可以实现更细的频率步进。

[0126]

如图1所示,公开了一种实现本发明的电路:包括产生基准信号的参考电路,与参考电路相连用于产生s波段基准信号的基准锁相源,与参考电路相连用于产生l波段基准信号的可变参考源,与基准锁相源和可变参考源相连用于实现频率变换的频率变换电路,与频率变换电路相连用于对频率变换后的信号进行分频的分频电路,与分频电路相连得到整个系统的主频基准的主锁相源,与主锁相源相连对主锁相源的信号进行频率扩展的频率扩展电路,与频率扩展电路相连对频率扩展后的无用信号进行有效滤波,提升系统输出信号的频谱纯度的开关滤波电路,以及与开关滤波电路相连对宽带信号的输出功率进行补偿及校准,提升信号的平坦度性能的功率调整电路。

[0127]

上述电路中,参考电路主要由晶振、功分器、放大器和滤波器构成,晶振产生的信号通过功分器分为两路后,分别通过放大器和滤波器后输入到基准锁相源和可变参考源。如图2所示,基准锁相源包括鉴相器、环路滤波器、压控振荡器、功分器、分频器及滤波器,参考电路产生的参考信号f

ref

进入到鉴相器后经过鉴相器进行r1分频鉴相,该信号经环路滤波进入振荡器,振荡器将该信号进行功分后,一路直接输出f1,一路经分频器进行m1分频后,经过滤波器与鉴相器进行鉴相,形成一个负反馈环路。其中:

[0128]

如图3所示,可变参考源电路包括鉴相器、环路滤波器、压控振荡器、功分器、两个分频器及滤波器,其中参考f

ref

进入到鉴相器后经过鉴相器进行r2分频鉴相,该信号经环路滤波进入振荡器,振荡器将该信号进行功分后,一路直接输出后经过m3分频产生f2信号,一路经分频器进行m2分频后,经过滤波器与鉴相器进行鉴相,形成一个负反馈环路。其中:

[0129]

如图4所示,频率变换电路由混频器和放大器构成,基准锁相源和可变参考源输出信号经混频器进行频率变换后经放大器放大后输入至分频器中。所述分频器由低通滤波器和可变分频器构成。基准锁相源头产生的信号f1和可变参考源产生的信号f2经混频器混频后产生信号f3,该信号经两级分频,分频比分别为r3、r4,经分频后进行滤波处理,并最终形成信号f4。

[0130]

如图5所示,主锁相源包括鉴相器、环路滤波器、助锁器、压控振荡器、功分器、衰减器、放大器、分频器及滤波器。主锁相源将上一级电路产生的信号f4经过n1倍的信号锁定后产生信号f5,即f5=f4*n1,其中n1可根据实际情况选择整数或者小数。

[0131]

如图6所示,频率扩展电路包括均衡器、温度补偿器、放大器、三个衰减器、单刀双掷开关、分频器、倍频器构成。主锁相源产生的信号f5经过均衡器和温度补偿器后提高在高低温下的功能指标,后经放大器进行功率方法,经开关进行高频段和低频段的频率切换,其中高频段信号经n2倍频后实现高频段的频率扩频,即f0=f5*n2(其中n2的取值为2、4、8

…

)。低频段信号接开关的另一路输出,该路信号经n3分频后,实现低频段频率信号的产生,即f0=f5/n3(其中n3的取值范围为1、2、4、8、16、32

…

),可实现低频段的频率输出。

[0132]

如图7所示,所述开关滤波电路包括3个单刀双掷开关,2个滤波器、3个可调衰减器。开关滤波电路为增加信号的频谱纯度,提取出除中心频率外的其余频率信号,提高系统的杂散指标。

[0133]

如图8所示,所述功率调整电路包括放大器、可调衰减器、数控衰减器、均衡器、温度补偿器和放大器,功率调整电路对最终输出的信号进行功率调整,并实现可变衰减功能。

[0134]

通过上述设计,本发明巧妙的避开了细步进频率合成方法中遇到的杂散点问题,并且补偿了多个电路的引入带来的相位噪声恶化问题,是对传统细步进频率合成方法的改进,有效提升了单锁相环细步进频率合成方法的杂散和频率步进,可将杂散指标提升至70dbc以下。

[0135]

上述实施例仅为本发明的优选实施方式之一,不应当用于限制本发明的保护范围,但凡在本发明的主体设计思想和精神上作出的毫无实质意义的改动或润色,其所解决的技术问题仍然与本发明一致的,均应当包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1